### ESCOLA POLITÉCNICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO DOUTORADO EM CIÊNCIA DA COMPUTAÇÃO

**GUILHERME HECK**

# THE IMPACT OF VOLTAGE SCALING OVER DELAY ELEMENTS WITH FOCUS ON POST-SILICON TESTS

Porto Alegre

2018

### PÓS-GRADUAÇÃO - *STRICTO SENSU*

Pontifícia Universidade Católica do Rio Grande do Sul

## THE IMPACT OF VOLTAGE SCALING OVER DELAY ELEMENTS WITH FOCUS ON POST-SILICON TESTS

# **GUILHERME HECK**

Dissertation submitted to the Pontifical Catholic University of Rio Grande do Sul in partial fulfillment of the requirements for the degree of PhD in Computer Science.

Advisor: Prof. Dr. Ney L. V. Calazans

### Ficha Catalográfica

H448i Heck, Guilherme

The impact of voltage scaling over delay elements with focus on post-silicon tests / Guilherme Heck . -2018.

147.

Tese (Doutorado) – Programa de Pós-Graduação em Ciência da Computação, PUCRS.

Orientador: Prof. Dr. Ney Laert Vilar Calazans.

1. Delay elements. 2. Voltage scaling. 3. Asynchronous. 4. Bundled-data. 5. Resiliency. I. Calazans, Ney Laert Vilar. II. Título.

Elaborada pelo Sistema de Geração Automática de Ficha Catalográfica da PUCRS com os dados fornecidos pelo(a) autor(a). Bibliotecária responsável: Salete Maria Sartori CRB-10/1363 Guilherme Heck

### The Impact of Voltage Scaling over Delay Elements with Focus on post-Silicon Tests

This Dissertation/Thesis has been submitted in partial fulfillment of the requirements for the degree of Doctor/Master of Computer Science, of the Graduate Program in Computer Science, School of Technology of the Pontificia Universidade Católica do Rio Grande do Sul.

Sanctioned on March 9<sup>th</sup>, 2018.

### **COMMITTEE MEMBERS:**

Prof. Dr. Tiago Roberto Balen (PGMicro/UFRGS)

Prof. Dr. Letícia Maria Bolzani Poehls (PPGEE/PUCRS)

Prof. Dr. César Augusto Missio Marcon (PPGCC/PUCRS)

Prof. Dr. Ney Laert Vilar Calazans (PPGCC/PUCRS - Advisor)

To my family.

"Whoever you are, no matter what social position you have, rich or poor, always show great strength and determination, and always do everything with much love and deep faith in God. One day you will reach your goal." (Ayrton Senna da Silva, 1991)

#### ACKNOWLEDGMENTS

Gostaria de agradecer muito aos meus pais. Meu pai Reinaldo Heck e minha mãe Ida heck foram as peças fundamentais para a conclusão dessa etapa. Foram tempos difíceis e, graças a eles, voltei a ter forças para seguir essa ardua caminhada. Esse trabalho eu dedico principalmente a vocês que fizeram tantos sacrifícios e estiveram sempre comigo. Sou grato também aos meus irmãos Marcos Heck e Bárbara heck que também se preocuparam com o desenrolar dessa novela e pelo apoio emocional. Agradeço aos meus cunhados Sônia Heck e Sérgio Ucoski que também estiveram ao meu lado. De um modo todo especial também gostaria de agradecer aos meus sobrinhos Artur, Henrique, Caroline, Eduardo, Diego e Isadora. Estiveram sempre em meus pensamentos e, assim como todos, me alegraram e deram força para seguir essa história. Peço desculpa pela falta de tempo para com vocês, mas serei eternamente grato a cada um pela compreenção. Não fazem ideia de quão importantes foram para a conclusão dessa etapa. Amo muito todos vocês.

Ao Ney, meu orientador, agradeço pelas horas de conversa e pelos auxílios durante os trabalhos realizados aqui. Tudo que consta aqui só foi possível com sua ajuda. Fizeste uma grande diferença na minha visão de acadêmico e tudo que aprendi com você serviu de referência para meu futuro profissional. Agradeço também aos demais professores do Grupo de Apoio ao Projeto de Hardware (GAPH) e do Grupo de Sistemas Embarcados (GSE). Alexandre Amory e seus auxílios em testes e uma pitadinha de robótica. Carlos Moratelli e as conversas do cotidiano e da política econômica. César Marcon pelo grande apoio no desenrolar dessa caminhada. Fabiano Hessel pelas discuções acaloradas de futebol. Fernando Moraes pelas conversas técnicas e discuções de trabalho. Grandes papos sobre infraestrutura e sobre tecnologia. Obrigado pelos papos fundamentais para acalmar os ânimos e seguir em frente. Sérgio Johann Filho e os papos aleatórios desde alimentação com sucos de laranja e frangos assados de televisão de cachorro a questões técnicas sobre implementações de SPI em hardware. Esse contato quase que diário me mostrou como um professor deve ser. Me mostrou quanto orgulho vocês tem em ajudar os outros e trazer um pouco de luz na escuridão atual.

Aos meus colegas de laboratório nessa caminhada, todos sabem o que desejo. Mas fica aqui um agradecimento especial aos meus colegas diretamente relacionados ao grupo de assíncronos: Leandro Heck, Ricardo Guazzelli, Matheus Gibiluka e Matheus Moreira. O Leandro me apoiou e ensinou a necessidade de deixar tudo organizado. A memória nem sempre ajuda num período tão longo. Sharelatex é vida. Ricardo sempre pronto para ajudar em algum projeto, dando várias ideias e levantando discuções relevantes. Obrigado pelas ajudas e pelas conversas. Matheus Gibiluka também incistiu em trabalhar com algo semelhante ao meu trabalho (voltage scaling). Agradeço pelas ajudas desde o mestrado quando bolsista até durante o doutorado. Por fim, mas não menos importante, Matheus Moreira me ajudou muito nas questões técnicas justamente por se interessar por tudo envolvendo microeletrônica. Muito obrigado por ter me recebido em sua casa em Los Angeles e pelos altos churrascos. Agradecimento especial também ao Felipe Kuentzer e ao Leonardo Rezende que, por várias vezes ouviram e discutiram problemas de testabilidade dos circuitos comigo. Os demais integrantes do GAPH e GSE tiveram importância principalmente em manter minha sanidade mental, dentre eles André Del Mestre, Bruno Oliveira, Eduardo Wachter, Felipe Magalhães, Felipe Bortolon, Gelmar da Costa, Guilherme Castilhos, Guilherme Madalozzo, Guilherme Medeiros, Lucas Copetti, Luciano Caimi, Luciano Ost, Marcelo Links, Marcelo Mandelli, Marcelo Ruaro, Walter Lau Neto. Desculpe a chatice e intrometimento nos papos. A intenção é sempre ajudar e melhorar. Muitas cervejas tomadas, churrascos comidos, mas principalmente muita amizade. Obrigado pelo convívio.

I am so grateful to Peter. Thanks for all the technical discussions we had. Thanks for always being so supportive. Thanks also go to my friends at USC who received me with open arms. Special thanks to Fei and Dylan, who became good friends. I also thank my colleagues and friends in the Async lab, Atharva, Yang, Ramy and Will, for the technical discussions and fun times. Thank you for all the good times in Los Angeles!

Finally, thank's to IEEE and its societies, specially the Computer Society and the Circuits and Systems Society, for the awards and student grants that helped me attending conferences. Agradeço à Faculdade de Informática (FACIN), ao Programa de Pós-Graduação em Ciências da Computação (PPGCC) e à Pontifícia Universidade Católica do Rio Grande do Sul (PUCRS) pela excelente estrutura e grandes funcionários. Agradeço à Hewlett-Packard (HP) que me forneceu auxílio durante o período do doutorado, além dos auxílios provenientes do governo brasileiro junto ao Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq) (Processo 142263/2012-5) e também o auxílio durante o período de Sanduíche na University of Southern California (USC) (processo 202519/2014-7), e a Coordenação de Aperfeiçoamento de Pessoal de Nível Superior (CAPES) (programa PROSUP taxas) e, por fim, à DELL que proporcionaram algumas das taxas de matrículas à PUCRS além da IEEE (grants em eventos).

# O IMPACTO DE VARIAÇÕES DA TENSÃO DE ALIMENTAÇÃO SOBRE ELEMENTOS DE ATRASO COM FOCO EM TESTES PÓS-FABRICAÇÃO

#### RESUMO

A demanda sem precedentes por poderosos dispositivos de processamento gerou quebras consecutivas de paradigma de projeto de circuito na área de Circuitos Integrados (CIs). O uso de tecnologia submicrométrica profunda aumenta a densidade de integração a níveis nunca vistos antes. No entanto, com CIs mais densos, a inclinação do relógio e outros efeitos requerem compensações em design síncrono, o que pode aumentar a área e o consumo de energia a valores inaceitáveis. Como alternativa, o paradigma assíncrono está re-emergindo, focado na eficiência de energia. Entre os modelos clássicos de projeto assíncrono, o Empacotamento-de-Dados (ED) se destaca pela sua capacidade de fornecer alto desempenho, reduzir a potência e obter resultados de área semelhante à dos modelos síncronos. Diferentemente dos modelos mais robustos de guase-atraso insensível, uma outra classe comum de modelos para implementar circuitos assíncronos, circuitos ED requerem o uso extensivo de Elementos de Atraso (EAs) para garantir a correta funcionalidade. No entanto, todos os circuitos são afetados por variações de Processo, Tensão e Temperatura (PTT), incluindo a Lógica Combinacional (LC) em ED impondo margem em elementos de atraso. Além disso, projetos atuais usam escalonamento de tensão para melhorar a eficiência de energia, o que afeta o atraso diferentemente em LCs e EAs adicionando mais margem em EAs. Um novo modelo baseado em ED chamado Blade usa o conceito de resiliência como uma esperança para evitar a margem de atraso causada por PTT e escalonamento de tensão. Contudo, o uso de dois elementos de atraso irá representar mais margens e mais tempo de teste no circuito final. Assim, este trabalho mostra uma análise do comportamento de elementos de atraso sob escalonamento de tensão e o impacto em testes pós-silício. Ele introduz um novo termo para determinar o impacto da escala de tensão sobre os elementos de atraso e também a comparação entre os EAs mais utilizados em

projetos ED usando esta nova métrica. Uma análise de testes em modelos ED e Blade é apresentada e o impacto da escala de tensão nestes projetos é analisado. Finalmente, um novo elemento de atraso é proposto focando na redução de margem e redução no tempo de teste para o modelo Blade.

**Palavras-Chave:** Elementos de Atraso, Escalonamento de Tensão, Assíncronos, Empacotamento de Dados, Resiliência, Variação de Processo, Tensão e Temperatura, Teste Pós-Silício.

# THE IMPACT OF VOLTAGE SCALING OVER DELAY ELEMENTS WITH FOCUS ON POST-SILICON TESTS

#### ABSTRACT

The unprecedented demand for powerful processing devices has generated consecutive circuit design paradigm breaks in the Integrated Circuits (ICs) arena. The use of deep submicron technology increases the integration density to levels never seen before. However, with denser ICs, clock skew and other effects require compensations in synchronous design, which can increase area overhead and power consumption to unacceptable values. As an alternative, the asynchronous paradigm is re-emerging, focused on power efficiency. Among classical asynchronous design templates, the Bundled-Data (BD) one stands off for its capability to provide high performance, reduce power and achieve area results similar to that of synchronous designs. Unlike the more robust Quasi-Delay Insensitive (QDI) templates, another common class of templates to implement asynchronous circuits, BD circuits require the extensive use of Delay Elements (DEs) to guarantee correct functionality. However, all circuits are affected by Process, Voltage and Temperature (PVT) variations, including the Combinational Logic (CL) on BD imposing margin on delay elements. In addition, current designs use voltage scaling to improve power efficiency, which impacts the delay differently in CLs and DEs adding more margin in DEs. A new template based on BD called Blade uses resiliency concept as a hope to avoid the delay margin caused by PVT and voltage scaling. Although, the use of two delay elements will represents more margins and extra test time on final circuit. So, this work shows an analysis of delay elements behavior under voltage scaling and the impact on post-silicon tests. It introduces a new term to determine the voltage scaling impact on delay elements and also the comparison between the most used DEs on BD designs using this novel metric. An analysis of tests in BD and Blade templates are presented and the impact of voltage scaling in these

designs is analyzed. Finally, a novel delay element is proposed focusing in margin reduction and reduction in test time for Blade template.

**Keywords:** Delay Elements, Voltage Scaling, Asynchronous, Bundled-Data, Resiliency, Blade, Process, Voltage and Temperature (PVT) Variations, Post-Silicon Tests.

# LIST OF FIGURES

| 2.1  | A typical stage of a synchronous circuit.                                                                                                                                                                                                         | 31 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | The original Razor design template, as proposed in [EKD+03]                                                                                                                                                                                       | 33 |

| 2.3  | An example of an asynchronous pipeline circuit segment                                                                                                                                                                                            | 34 |

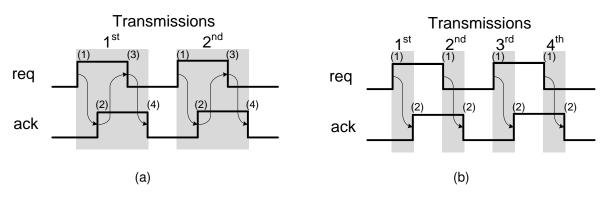

| 2.4  | Handshake protocols: (a) 4-phase and (b) 2-phase.                                                                                                                                                                                                 | 34 |

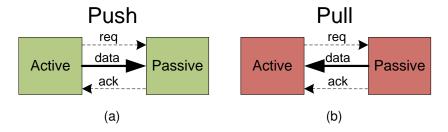

| 2.5  | The organization of (a) Push and (b) Pull data channels in BD asynchronous designs.                                                                                                                                                               | 35 |

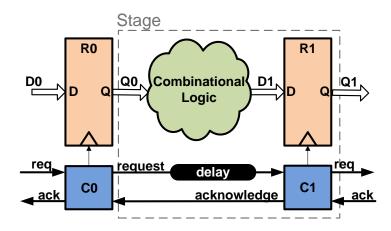

| 2.6  | Bundled-data stage segment using a push channel, with a delay element in the request line                                                                                                                                                         | 36 |

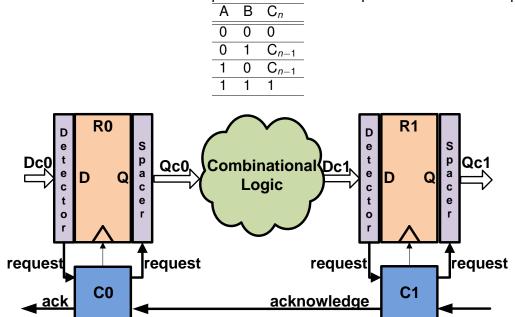

| 2.7  | A partial view of a quasi delay insensitive pipeline.                                                                                                                                                                                             | 37 |

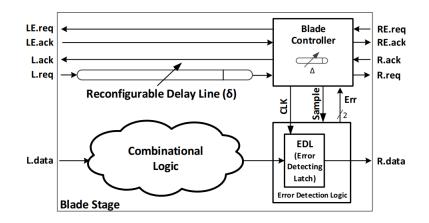

| 2.8  | The Blade template [HMH+15]                                                                                                                                                                                                                       | 39 |

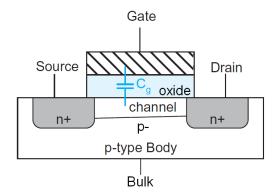

| 2.9  | A traditional n-channel MOSFET structure, highlighting the transistor termi-<br>nals, based on [WH11].                                                                                                                                            | 41 |

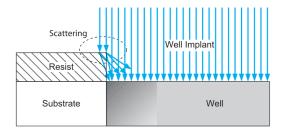

| 2.10 | Well-edge proximity effect increasing the doping level near the edge of the well [WH11].                                                                                                                                                          | 43 |

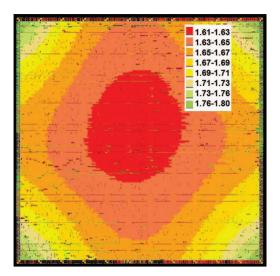

| 2.11 | IR Drop plot of a test pattern applied to wb_conmax benchmark [TPC11]                                                                                                                                                                             | 45 |

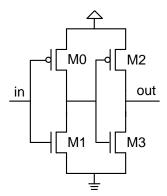

| 2.12 | Gate delay element.                                                                                                                                                                                                                               | 47 |

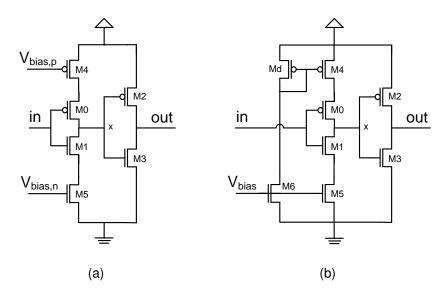

| 2.13 | Current-starved inverter topologies: (a) using two independent $V_{bias}$ and (b) using a single $V_{bias}$                                                                                                                                       | 48 |

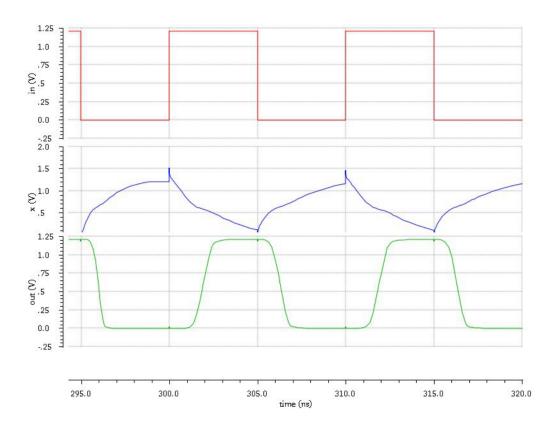

| 2.14 | Graphs depicting the transient simulation of Figure 2.13(b) current-starved inverter.                                                                                                                                                             | 49 |

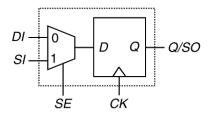

| 2.15 | The structure of a Muxed-D flip-flop [WST10].                                                                                                                                                                                                     | 51 |

| 2.16 | Scan-based tests [TPC11]: (a) launch-off-shift, (b) launch-off-capture and (c) enhanced scan.                                                                                                                                                     | 52 |

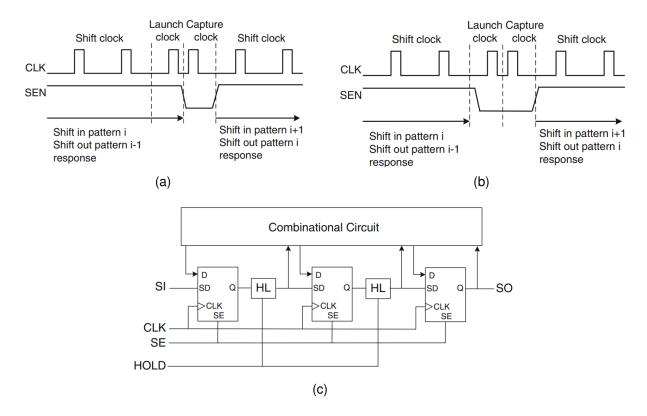

| 3.1  | Variation of the effective threshold voltage ( $\hat{V}_{T0}$ ) (author notation for $V_t$ ), according to the transistor length ( <i>L</i> ) [TM11]: (a) without short-channel effects acting; (b) with short-channel effects considered.        | 58 |

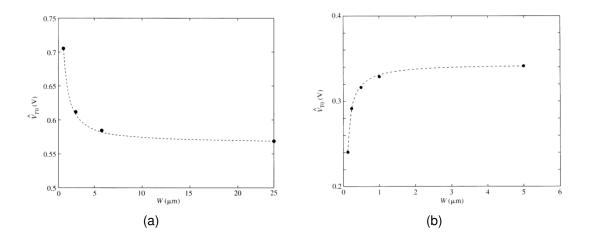

| 3.2  | Illustrating the variation of the effective threshold voltage ( $\hat{V}_{T0}$ is the notation for $V_t$ employed in reference [TM11]) with transistor width ( $W$ ): (a) using the LOCOS isolation process; (b) using the STI isolation process. | 59 |

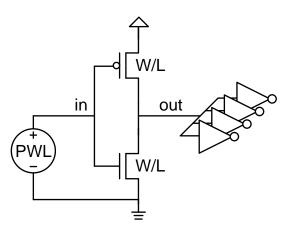

| 3.3  | Circuit schematic used to evaluate $VSDR$ according to variations in transistors width ( $W$ ) and length ( $L$ ) under different supply voltages.                                                                                                | 59 |

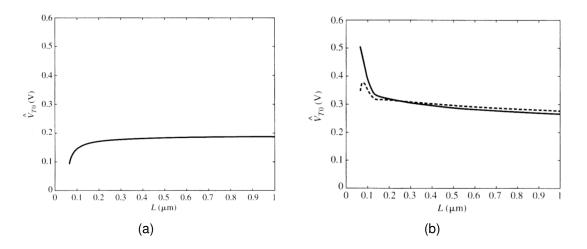

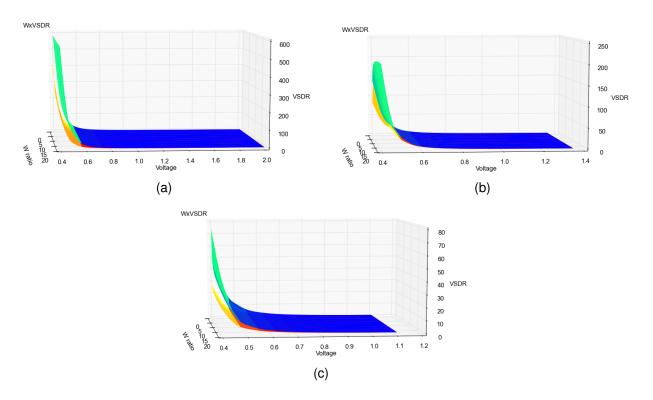

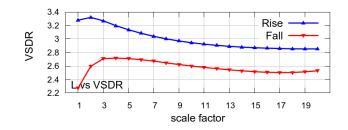

| 3.4  | The <i>VSDR</i> variation due to changes in W and in the supply voltage: (a) for the TSMC 180nm bulk CMOS technology; (b) for the STmicroelectronics 65nm bulk CMOS technology; and (c) for the STmicroelectronics 28nm FDSOI technology.                     | 60 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

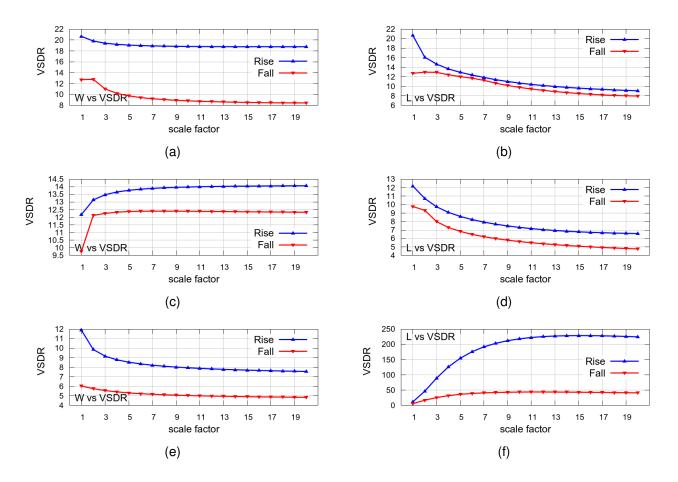

| 3.5  | The <i>VSDR</i> variation as a function of: (a) Width and (b) Length in 180nm, (c) Width and (d) Length in 65nm, and (e) Width and (f) Length in 28nm                                                                                                         | 61 |

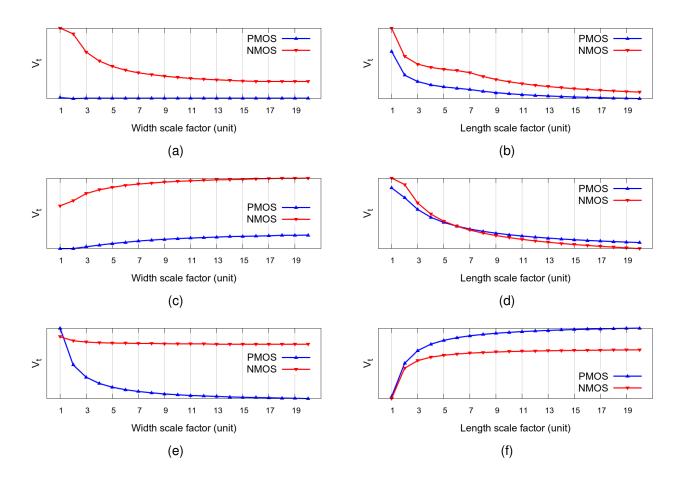

| 3.6  | $V_t$ variation according to: (a) Width and (b) Length in 180nm; (c) Width and (d) Length in 65nm; and (e) Width and (f) Length in 28nm                                                                                                                       | 62 |

| 3.7  | VSDR variation in the 180nm technology varying length ( $L$ ) for a 0.9V supply.                                                                                                                                                                              | 63 |

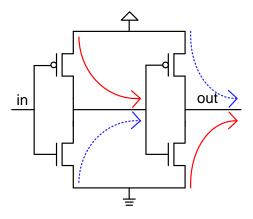

| 3.8  | Circuit topology to reduce VSDR rise/fall difference.                                                                                                                                                                                                         | 64 |

| 3.9  | The <i>VSDR</i> variations after applying the rise/fall difference reduction tech-<br>nique: (a) Width and (b) Length for the 180nm technology, (c) Width and (d)<br>Length for the 65nm technology, and (e) Width and (f) Length for the 28nm<br>technology. | 64 |

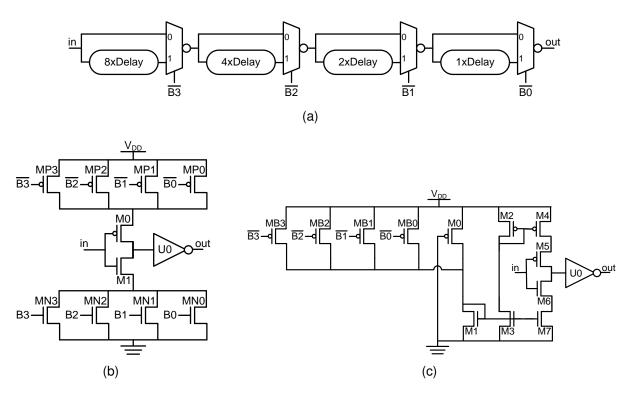

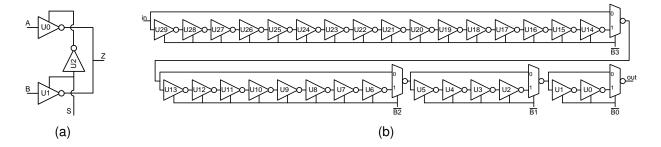

| 3.10 | The basic schematic of the three DEs investigated: (a) the MUX-DE [TBW <sup>+</sup> 09];<br>(b) the DCCS-DE [MNS03]; and (c) the CMCS-DE [MNS05]                                                                                                              | 67 |

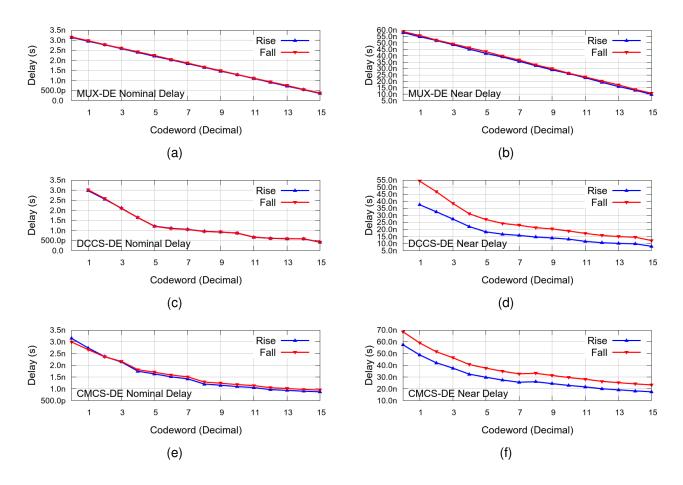

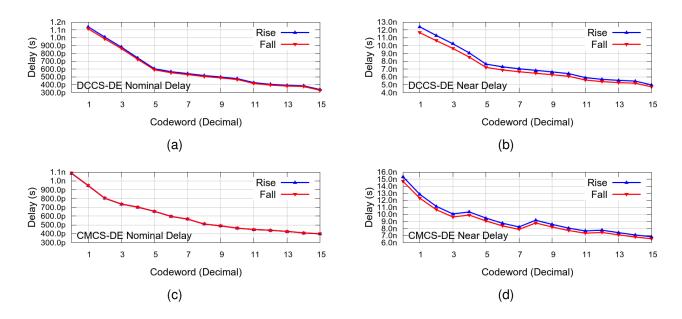

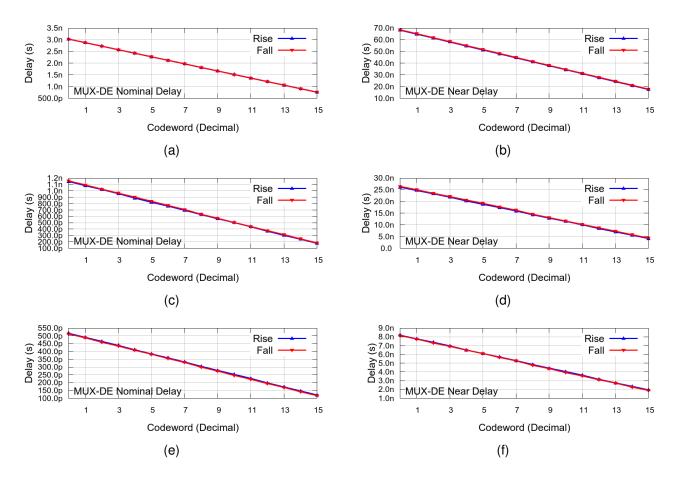

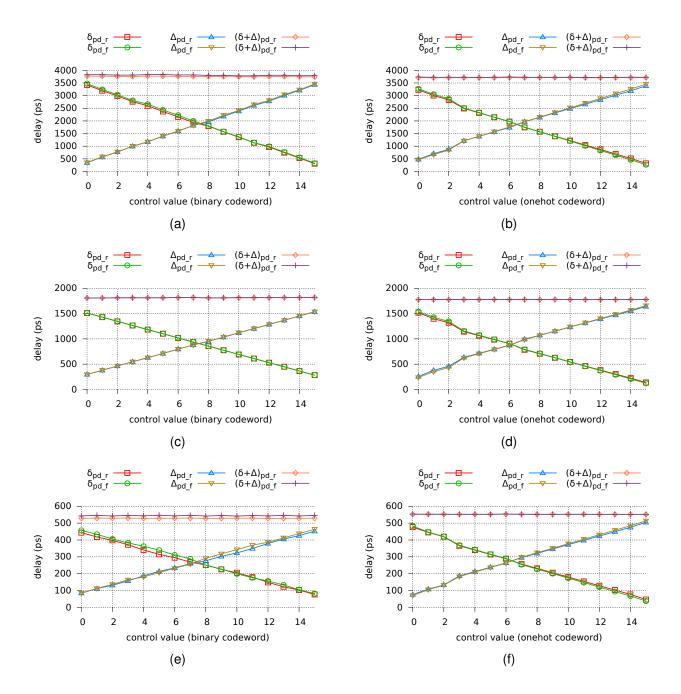

| 3.11 | Delay produced by programmable DEs implemented in 180nm: (a) MUX-<br>DE @ nominal and (b) MUX-DE @ near, (c) DCCS-DE @ nominal and (d)<br>DCCS-DE @ near, and (e) CMCS-DE @ nominal and (f) CMCS-DE @ near.                                                   | 70 |

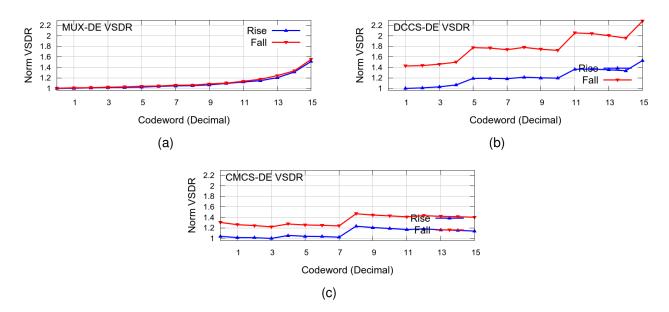

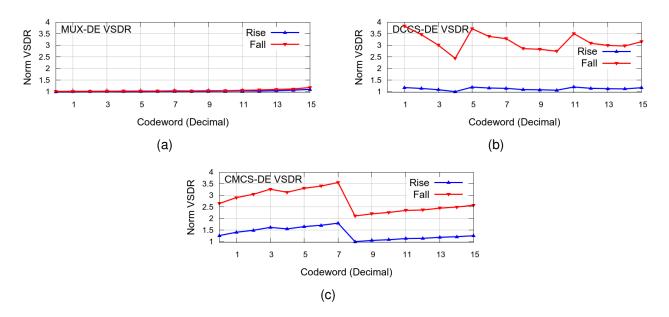

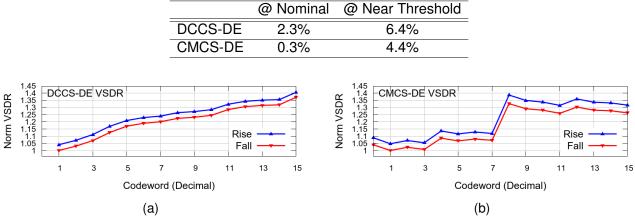

| 3.12 | Normalized <i>VSDR</i> values for DEs implemented in 180nm: (a) MUX-DE, (b) DCCS-DE and (c) CMCS-DE.                                                                                                                                                          | 71 |

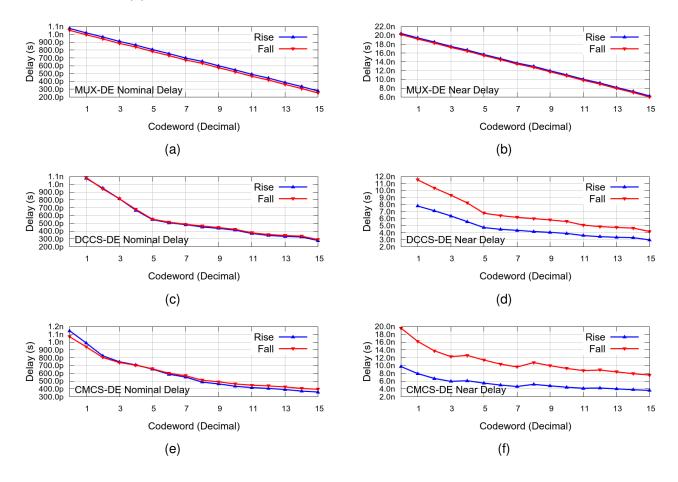

| 3.13 | Delay produced by the programmable DEs implemented in 65nm: (a) MUX-<br>DE @ nominal and (b) MUX-DE @ near, (c) DCCS-DE @ nominal and (d)<br>DCCS-DE @ near, and (e) CMCS-DE @ nominal and (f) CMCS-DE @ near.                                                | 71 |

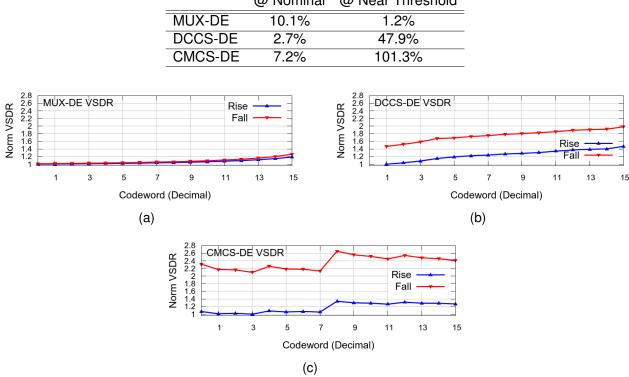

| 3.14 | Normalized <i>VSDR</i> values for DEs implemented in 65nm: (a) MUX-DE, (b) DCCS-DE and (c) CMCS-DE.                                                                                                                                                           | 72 |

| 3.15 | Delay produced by programmable DEs implemented in 28nm: (a) MUX-<br>DE @ nominal and (b) MUX-DE @ near, (c) DCCS-DE @ nominal and (d)<br>DCCS-DE @ near, and (e) CMCS-DE @ nominal and (f) CMCS-DE @ near.                                                    | 73 |

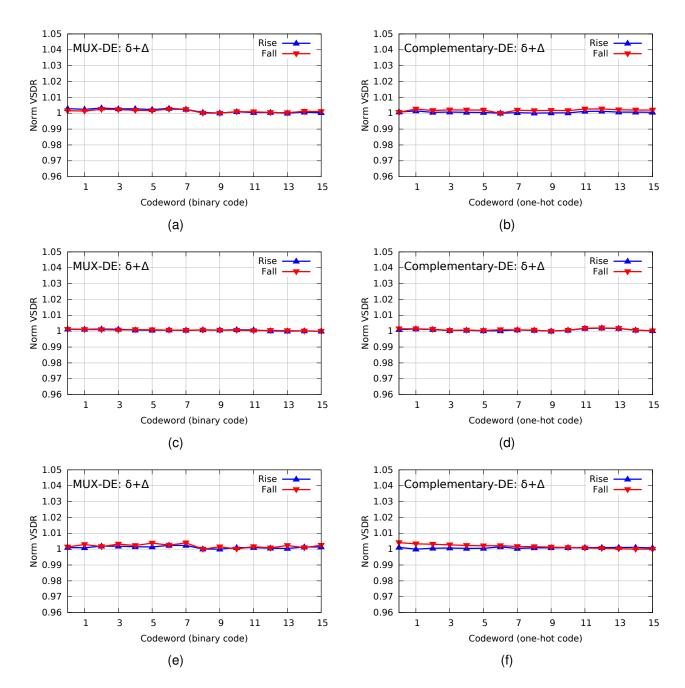

| 3.16 | Normalized <i>VSDR</i> values for DEs implemented in 28nm: (a) MUX-DE, (b) DCCS-DE and (c) CMCS-DE.                                                                                                                                                           | 74 |

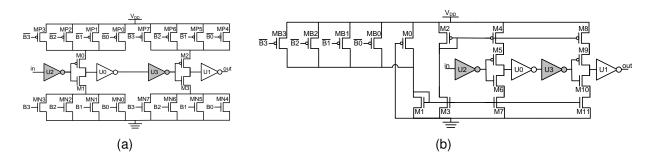

| 3.17 | Schematic of DEs after applying the balancing rise and fall times optimiza-<br>tion: (a) Balanced DCCS-DE and (b) Balanced CMCS-DE                                                                                                                            | 75 |

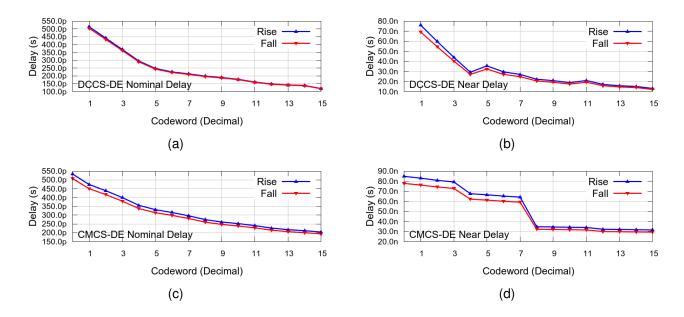

| 3.18 | Delay produced by programmable DEs implemented in 180nm using the proposed optimization technique: (a) DCCS-DE @ nominal and (b) DCCS-DE @ near, and (c) CMCS-DE @ nominal and (d) CMCS-DE @ near                                                             | 76 |

| 3.19 | Normalized <i>VSDR</i> for each DEs implemented in 180nm: (a) MUX-DE, (b) DCCS-DE and (c) CMCS-DE.                                                                                                                                                                     | 76  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

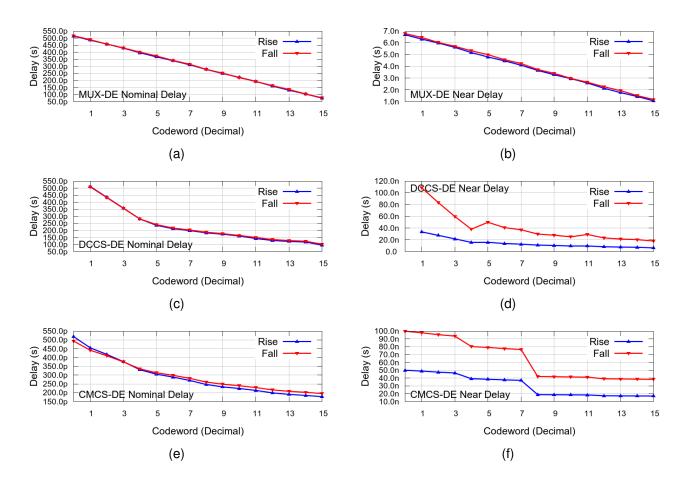

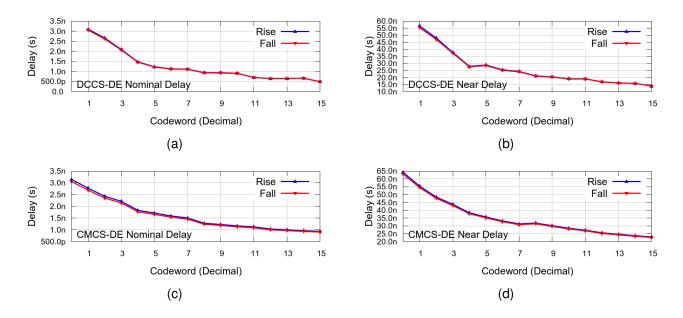

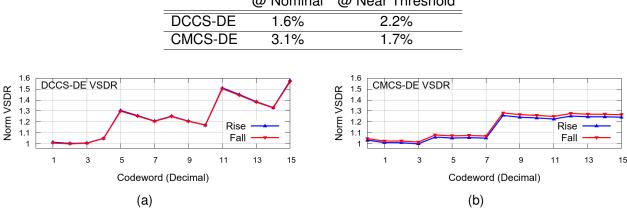

| 3.20 | Delay produced by programmable DEs implemented in 65nm using the pro-<br>posed optimization technique: (a) DCCS-DE @ nominal and (b) DCCS-DE<br>@ near, and (c) CMCS-DE @ nominal and (d) CMCS-DE @ near                                                               | 77  |

| 3.21 | Normalized <i>VSDR</i> for each DEs implemented in 65nm: (a) MUX-DE, (b) DCCS-DE and (c) CMCS-DE.                                                                                                                                                                      | 77  |

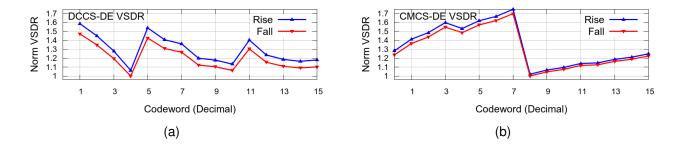

| 3.22 | Delay produced by programmable DEs implemented in 28nm using the pro-<br>posed optimization technique: (a) DCCS-DE @ nominal and (b) DCCS-DE<br>@ near, and (c) CMCS-DE @ nominal and (d) CMCS-DE @ near                                                               | 78  |

| 3.23 | Normalized <i>VSDR</i> for each DEs implemented in 28nm: (a) MUX-DE, (b) DCCS-DE and (c) CMCS-DE.                                                                                                                                                                      | 79  |

| 3.24 | (a) A multiplexer designed with tristates. (b) The new tristate-based MUX-DE.                                                                                                                                                                                          | 80  |

| 3.25 | Delay produced by new tristate-based MUX-DE implemented in: (a) 180nm<br>@ nominal and (b) 180nm @ near, (c) 65nm @ nominal and (d) 65nm @<br>near, and (e) 28nm @ nominal and (f) 28nm @ near                                                                         | 80  |

| 3.26 | The normalized <i>VSDR</i> variation values for: (a) the original MUX-DE @ 180nm; (b) the tristate-based MUX-DE @ 180nm; (c) the original MUX-DE @ 65nm; (d) the tristate-based MUX-DE @ 65nm; (e) the original MUX-DE                                                 | _ / |

|      | @ 28nm; (f) the tristate-based MUX-DE @ 28nm                                                                                                                                                                                                                           | 81  |

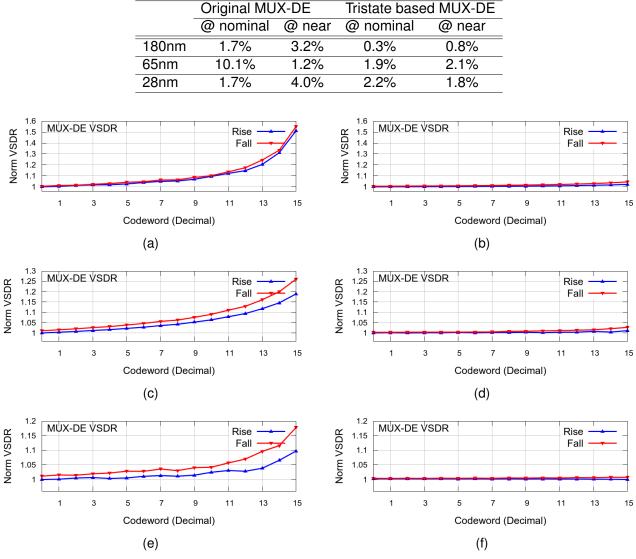

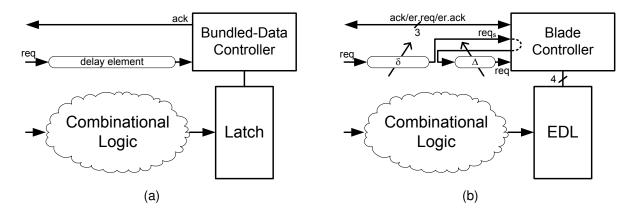

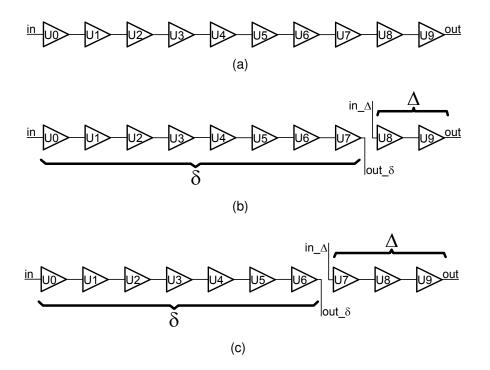

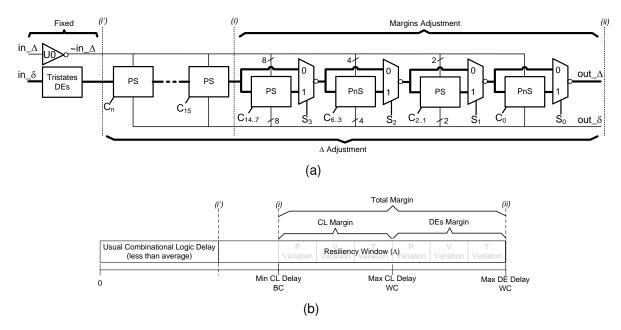

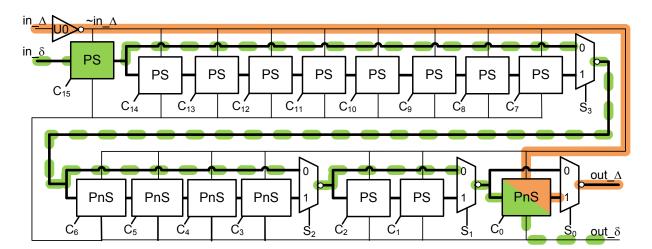

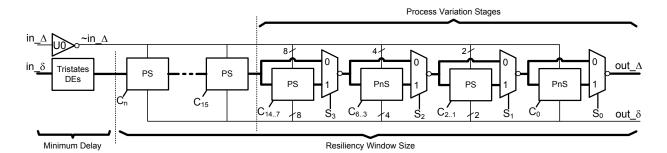

| 5.1  | Delay elements in distinct BD templates: (a) Bundled-data; (b) Blade                                                                                                                                                                                                   | 94  |

| 5.2  | Examples of delay element in: (a) Bundled-data; (b) Blade (example 1); (c) Blade (example 2).                                                                                                                                                                          | 95  |

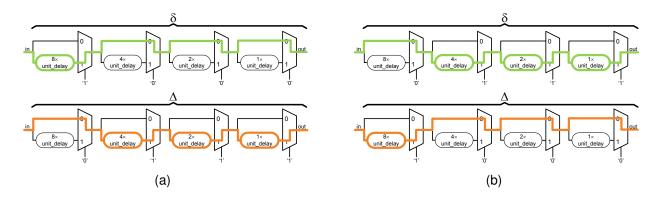

| 5.3  | Example of Blade DEs consecutive paths: (a) $\delta$ = "1000" and $\Delta$ = "0111";<br>(b) $\delta$ = "0111" and $\Delta$ = "1000".                                                                                                                                   | 96  |

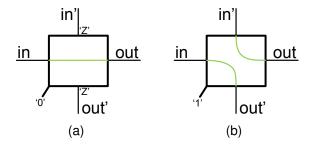

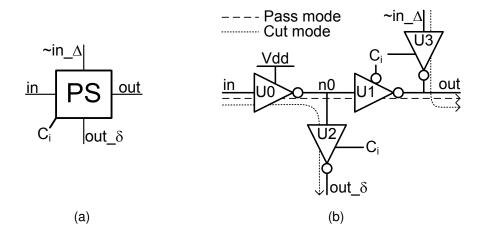

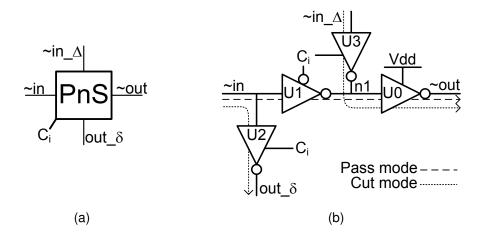

| 5.4  | The functionality of the Pass-Section DE module in its two possible config-<br>urations: (a) Pass and (b) Section                                                                                                                                                      | 97  |

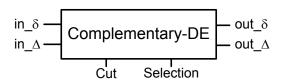

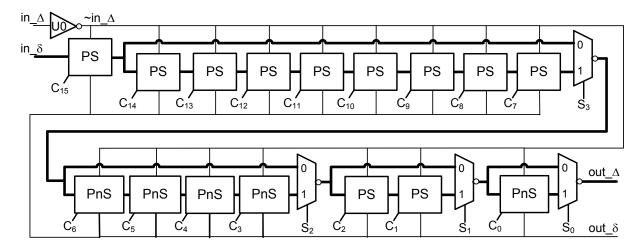

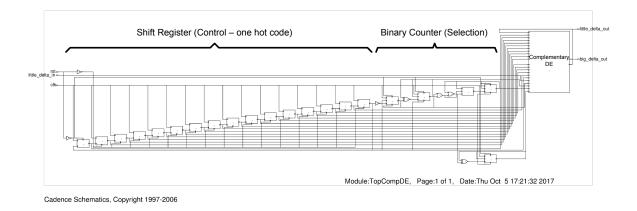

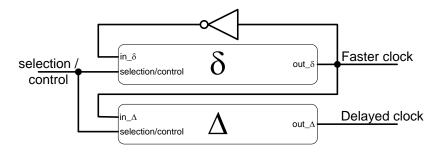

| 5.5  | The Complementary-DE external interface.                                                                                                                                                                                                                               | 97  |

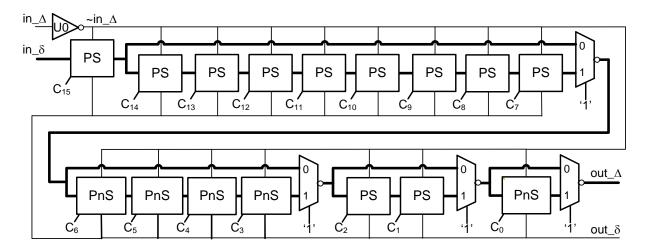

| 5.6  | The Complementary-DE structure, using a mux-DE implementation approach.                                                                                                                                                                                                | 97  |

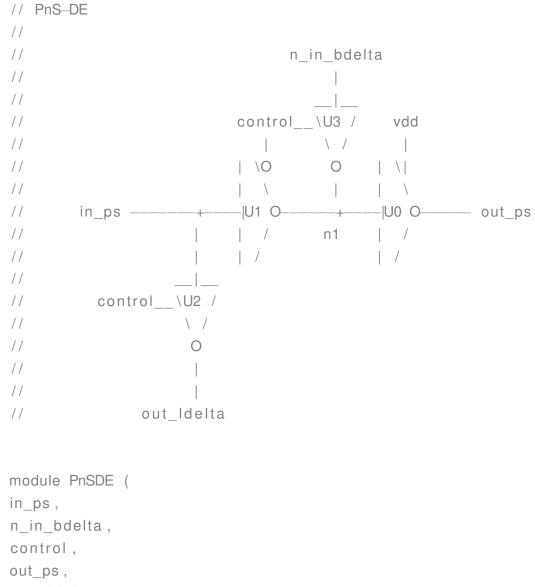

| 5.7  | The Pass-Section DE: (a) external interface; (b) schematic. In the Pass mode the element connects <i>in</i> to <i>out</i> (works like a buffer), while in Cut mode it derives <i>in</i> to <i>out_</i> $\delta$ while connects $\sim in_{\Delta} \Delta$ to <i>out</i> | 98  |

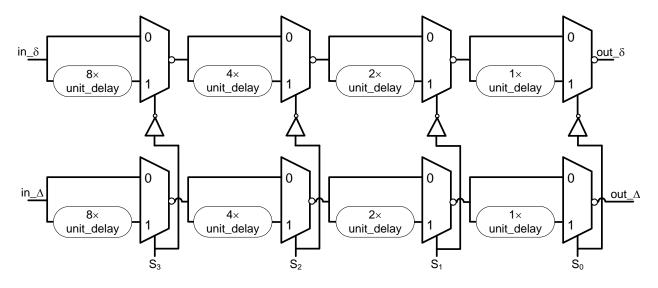

| 5.8  | The Pass-nSection DE: (a) external interface; (b) schematic.                                                                                                                                                                                                           | 99  |

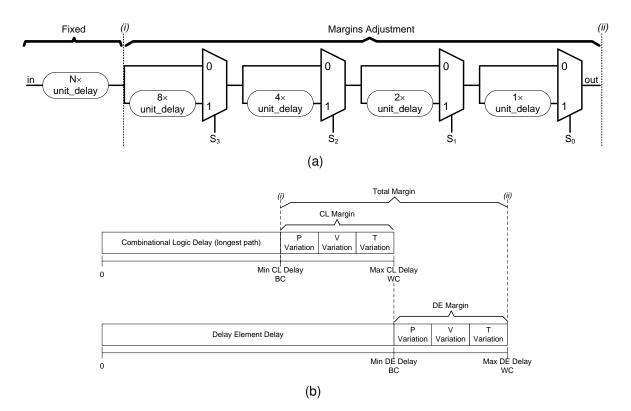

| 5.9  | BD delay adjustments: (a) Example of a conventional BD DE; (b) BD timing diagrams (BC = Best Case, WC = Worst Case).                                                                                                                                                   | 100 |

| 5.10 | Blade delays: (a) Example of Complementary-DE adjustments; (b) Blade timing diagram (BC=Best Case, WC=Worst Case).                                                                                                                                                     | 100 |

| 5.11 | Complementary-DE configuration example ( <i>control</i> = "0000000000000001"<br>and <i>selection</i> = "0001"                                                                                                          |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.12 | Complementary-DE parameters for HDL input file                                                                                                                                                                         |

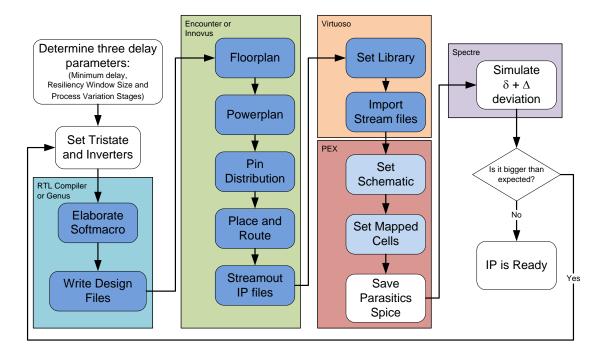

| 5.13 | The design flow for Complementary-DE IP production                                                                                                                                                                     |

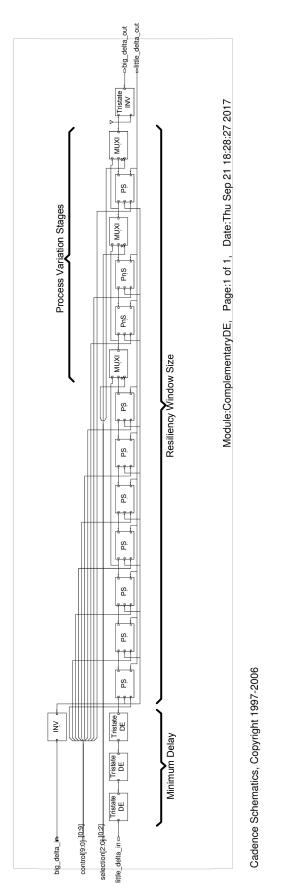

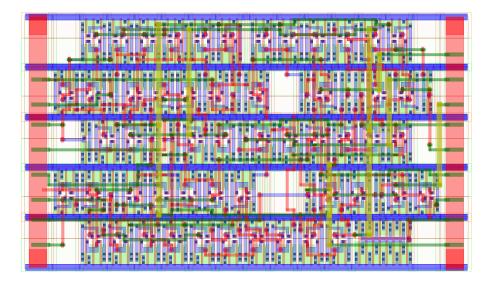

| 5.14 | Illustration of a Complementary-DE synthesized in Cadence Genus using the proposed parameterizable Verilog                                                                                                             |

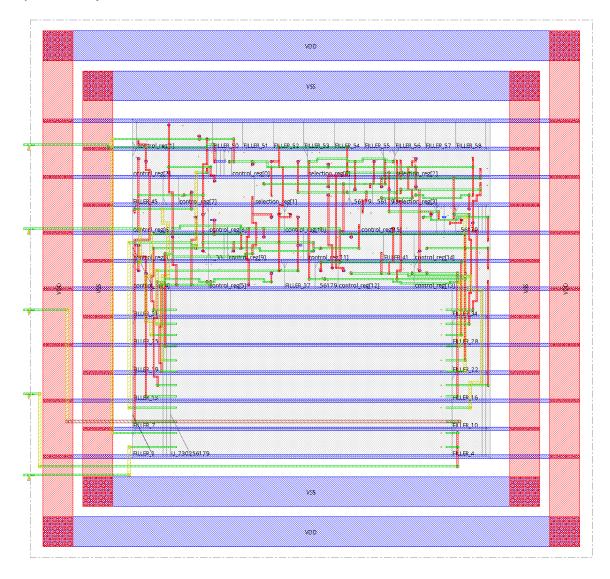

| 5.15 | An example of power plan and pin distribution for the Complementary-DE IP. 106                                                                                                                                         |

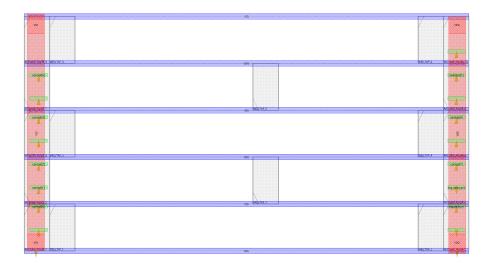

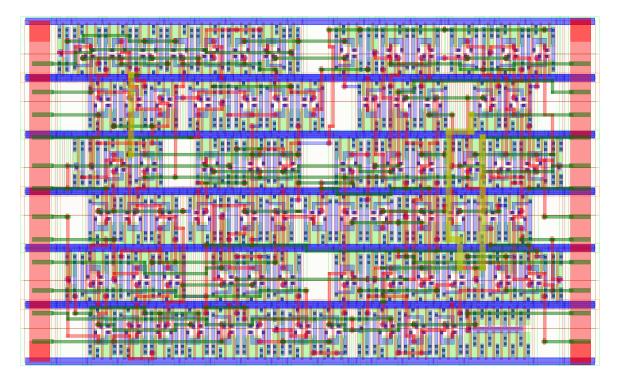

| 5.16 | An example of the final layout for the Complementary-DE IP, with a limited number of layout layers displayed                                                                                                           |

| 5.17 | An example Complementary-DE IP layout, as imported in Virtuoso 108                                                                                                                                                     |

| 5.18 | Example final layout for a Complementary-DE IP with Minimum Delay = 0,<br>Resiliency Window Size = 16, and Process Variation Stages = 4                                                                                |

| 5.19 | A schematic view of a testbench for the Complementary-DE, with the results<br>of the testbench logic synthesis, containing the test circuit and an instace of<br>the Complementary-DE                                  |

| 5.20 | Example result of the test circuit physical synthesis, with the Complementary-<br>DE occupied area as an empty box at the bottom center of the layout 110                                                              |

| 5.21 | A complete layout example of a testbench circuit instantiating a Complementary-<br>DE IP                                                                                                                               |

| 5.22 | The Complementary-DE configuration used for comparison simulations 113                                                                                                                                                 |

| 5.23 | The MUX-DE structure for comparison purposes                                                                                                                                                                           |

| 5.24 | Produced delays and delay sums in: (a) MUX-DE 180nm, (b) Complementary-<br>DE 180nm, (c) MUX-DE 65nm and (d) Complementary-DE 65nm, (e) MUX-<br>DE 28nm and (f) Complementary-DE 28nm. 28nm results do not take wiring |

|      | effects into account                                                                                                                                                                                                   |

| 5.25 | Impact in the $\delta$ + $\Delta$ sum delay margin considering PVT variations for: (a) 180nm, (b) 65nm, and (c) 28nm                                                                                                   |

| 5.26 | The <i>VSDR</i> variation in $\delta$ + $\Delta$ : (a) MUX-DE in 180nm, (b) Complementary-<br>DE in 180nm, (c) MUX-DE in 65nm, (d) Complementary-DE in 65nm, (e)<br>MUX-DE in 28nm, and (f) Complementary-DE in 28nm   |

| 5.27 | The clock operation in a Razor template                                                                                                                                                                                |

| 5.28 | A proposal of clock generator for Razor templates, based on the Complementary-                                                                                                                                         |

|      | DE                                                                                                                                                                                                                     |

# LIST OF TABLES

| 1.1 | Low power Design Technology Improvements and Impact on Dynamic and Static Power [ITR].                                                       | 24  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Behavior of a basic 2-input C-element with inputs A and B and output C                                                                       | 37  |

| 2.2 | The structure of a single bit dual-rail code                                                                                                 | 38  |

| 2.3 | Approximation of intrinsic MOS gate capacitance [WH11].                                                                                      | 46  |

| 3.1 | Maximum difference between rise and fall delays in DEs implemented in 180nm.                                                                 | 69  |

| 3.2 | Maximum difference between rise and fall delays in DEs implemented in 65nm.                                                                  | 72  |

| 3.3 | Maximum difference between rise and fall delays in DEs implemented in 28nm.                                                                  | 73  |

| 3.4 | Maximum difference between rise and fall delays in DEs implemented in 180nm.                                                                 | 76  |

| 3.5 | Maximum difference between rise and fall delays in DEs implemented in 65nm.                                                                  | 77  |

| 3.6 | Maximum difference between rise and fall delays in DEs implemented in 28nm.                                                                  | 78  |

| 3.7 | Maximum difference between rise and fall delays in the original MUX-DE and in the tristate-based MUX-DE                                      | 81  |

| 3.8 | A comparison of programmable DEs relevant design parameters. Blue num-<br>bers indicate best values, while red numbers indicate worst values | 82  |

| 5.1 | Comparison between MUX-DE and Complementary-DE (180nm)                                                                                       | 114 |

| 5.2 | Comparison between MUX-DE and Complementary-DE (65nm)                                                                                        | 114 |

| 5.3 | Comparison between MUX-DE and Complementary-DE (28nm)                                                                                        | 114 |

# LIST OF ALGORITHMS

| 4.1 | Synchronous delay fault test.                                                | 84 |

|-----|------------------------------------------------------------------------------|----|

| 4.2 | Bundled-Data delay test with fixed delay for a 2-phase circuit.              | 87 |

| 4.3 | Bundled-Data delay test under voltage scaling with fixed delay for a 2-phase |    |

|     | circuit.                                                                     | 88 |

| 4.4 | Blade delay test with fixed $\delta + \Delta$ .                              | 90 |

| 4.5 | Blade delay test with multiple $\delta$ + $\Delta$ combinations              | 91 |

| 4.6 | Blade Delay Test under Voltage Scaling with fixed $\delta + \Delta$          | 92 |

| 4.7 | Blade Delay Test under Voltage Scaling with multiple $\delta$ + $\Delta$     | 93 |

|     |                                                                              |    |

### LIST OF ACRONYMS

- ADE Analog Design Environment

- AICSP Analog Integrated Circuits and Signal Processing

- AS At-Speed

- ATPG Automatic Test Pattern Generation

- BD Bundled-Data

- BIST Built-In Self-Test

- BTBT Band-To-Band Tunneling

- CAD Computer Aided Design

- CL Combinational Logic

- CMCS Current mirror-Controlled Current-Starved

- CMOS Complementary Metal Oxide Semiconductor

- **CPU Central Processing Unit**

- CSI Current-Starved Inverter

- CUT Circuit Under Test

- DCCS Direct-Controlled Current-Starved

- DCO Digitally Controlled Oscillator

- **DE Delay Element**

- DEF Design Exchange Format

- DFS Dynamic Frequency Scaling

- DFT Design For Testability

- DI Delay Insensitive

- DIBL Drain-Induced Barrier Lowering

- DLL Delay-Locked Loop

- DSM Deep SubMicron

- DVFS Dynamic Voltage and Frequency Scaling

- DVS Dynamic Voltage Scaling

- ECAD Electronic Computer Aided Design

- EDL Error Detector Logic

- FDSOI Fully Depleted Silicon-On-Insulator

- FET Field Effect Transistor

- FF Flip-Flop

- FFT Fast Fourier Transform

- FO4 Fanout Of Four

- FS Frequency Scaling

- FTAS Faster-Than-At-Speed

- GALS Globally Asynchronous Locally Synchronous

- GDS Graphic Database System

- GIDL Gate-Indiced Drain Leakage

- HDL Hardware Description Language

- IC Integrated Circuit

- IOT Internet of Things

- IP Intellectual Property

- ITRS International Technology Roadmap for Semiconductors

- LASCAS Latin America Symposium in Circuits and Systems

- LEF Library Exchange File

- LFSR Linear Feedback Shift Register

- LOC Launch-Off-Capture

- LOCOS LOCal-Oxidation of Silicon

- LOS Launch-Off-Shift

- LUT Look Up Table

- LVS Layout Versus Schematic

- MOS Metal Oxide Semiconductor

- MOSFET Metal Oxide Semiconductor Field Effect Transistor

- MUX Multiplexer

- NCL Null Convention Logic

- NDA Non-Disclosure Agreement

- NRZ Non-Return to Zero

- OASIS Open Artwork System Interchange Standard

- ORA Output Response Analyzer

- PDF Path-Delay Fault

- PDK Process Design Kit

- PEX Practices EXtraction

- PLL Phase-Locked Loop

- PNS Pass-nSection

- PS Pass-Section

- PVT Process, Voltage and Temperature

- PWL PieceWise Linear

- QDI Quasi-Delay Insensitive

- **RF** Radio Frequency

- RTL Register-Transfer Level

- RZ Return to Zero

- SDD Small-Delay Defect

- SDF Standard Delay Format

- SEE Single Event Effect

- STI Shallow-Trench Isolation

- STM STMicroelectronics

- TDF Transition-Delay Fault

- **TPG** Test Pattern Generation

- TSMC Taiwan Semiconductor Manufacturing Company

- TDC Time-to-Digital Converter

- VLSI Very Large Scale Integration

- VS Voltage Scaling

- VSDR Voltage Scaled Delay Ratio

# CONTENTS

| 1     | INTRODUCTION                                                                                | 23         |

|-------|---------------------------------------------------------------------------------------------|------------|

| 1.1   | MOTIVATION                                                                                  | 25         |

| 1.2   | DESCRIPTION OF THE PROBLEM TO ADDRESS                                                       | 26         |

| 1.3   | GOALS                                                                                       | 27         |

| 1.4   | ORIGINALITY OF THIS THESIS                                                                  | 28         |

| 1.5   | DOCUMENT STRUCTURE                                                                          | 28         |

| 2     | AN OVERVIEW OF BASIC CONCEPTS                                                               | 30         |

| 2.1   | SYNCHRONOUS CIRCUIT DESIGN                                                                  | 30         |

| 2.1.1 | THE CLASSICAL SYNCHRONOUS CIRCUIT DESIGN APPROACH                                           | 31         |

| 2.1.2 | THE RESILIENT SYNCHRONOUS CIRCUIT DESIGN APPROACH                                           | 32         |

| 2.2   | THE ASYNCHRONOUS CIRCUIT DESIGN APPROACH                                                    | 33         |

| 2.2.1 | THE BUNDLED-DATA ASYNCHRONOUS CIRCUIT DESIGN APPROACH                                       | 34         |

| 2.2.2 | THE DELAY INSENSITIVE AND QUASI DELAY INSENSITIVE ASYNCHRONOUS<br>CIRCUIT DESIGN APPROACHES | <b>3</b> 6 |

| 2.2.3 | THE RESILIENT ASYNCHRONOUS CIRCUIT DESIGN APPROACH                                          | 39         |

| 2.3   | METAL OXIDE SEMICONDUCTOR FIELD EFFECT TRANSISTORS (MOSFET)                                 | 40         |

| 2.3.1 | MOSFET ADVANCED TECHNOLOGY EFFECTS                                                          | 42         |

| 2.3.2 | MOSFET VARIABILITY                                                                          | 42         |

| 2.3.3 | IR-DROP EFFECTS                                                                             | 44         |

| 2.4   | DELAY ELEMENTS                                                                              | 46         |

| 2.4.1 | DIGITAL CELL DELAY ELEMENTS                                                                 | 46         |

| 2.4.2 | CURRENT-STARVED INVERTER DELAY ELEMENTS                                                     | 47         |

| 2.5   | TEST ON INTEGRATED CIRCUITS                                                                 | 49         |

| 3     | DELAY ELEMENTS OPERATING UNDER VOLTAGE SCALING                                              | 55         |

| 3.1   | VOLTAGE SCALING EFFECTS                                                                     | 56         |

| 3.1.1 | THE VSDR CONCEPT VALIDATION                                                                 | 58         |

| 3.1.2 | RISE AND FALL VSDR DIFFERENCE REDUCTION                                                     | 63         |

| 3.2   | DELAY ELEMENTS FOR 2-PHASE BUNDLED-DATA                                                     | 65         |

| 3.3   | THE IMPACT OF VOLTAGE SCALING IN DELAY ELEMENTS                                             | 67         |

| 3.3.1 | VOLTAGE SCALING EFFECTS ON NON-OPTIMIZED DELAY ELEMENTS                                     | 68         |

| 3.3.2 | OPTIMIZING DELAY ELEMENTS TO OPERATE UNDER VOLTAGE SCALING        | 74  |

|-------|-------------------------------------------------------------------|-----|

| 4     | POST-SILICON TEST ANALYSIS ON BUNDLED-DATA DESIGNS                | 83  |

| 4.1   | CONVENTIONAL BUNDLED-DATA DELAY TEST ANALYSIS                     | 84  |

| 4.1.1 | COMBINATIONAL LOGIC VS DE DELAY                                   | 85  |

| 4.1.2 | VOLTAGE SCALING DELAY TEST                                        | 87  |

| 4.2   | BLADE DELAY TEST ANALYSIS                                         | 88  |

| 4.2.1 | COMBINATIONAL LOGIC VS DE DELAY                                   | 89  |

| 4.2.2 | VOLTAGE SCALING DELAY TEST                                        | 92  |

| 5     | THE COMPLEMENTARY DELAY ELEMENT                                   | 94  |

| 5.1   | THE COMPLEMENTARY DELAY ELEMENT                                   | 95  |

| 5.1.1 | THE PASS-SECTION DELAY ELEMENT                                    | 97  |

| 5.1.2 | THE COMPLEMENTARY-DE PROCESS VARIATIONS COMPENSATION              | 98  |

| 5.2   | THE COMPLEMENTARY-DE DESIGN FLOW                                  | 101 |

| 5.2.1 | THE PARAMETERIZABLE COMPLEMENTARY-DE                              | 102 |

| 5.2.2 | SYNTHESIS, EXTRACTION AND INSTANTIATION OF COMPLLEMENTARY-<br>DES | 103 |

| 5.3   | COMPLEMENTARY-DE SIMULATION AND COMPARISON WITH MUX-DE            | 111 |

| 5.3.1 | THE COMPLEMENTARY-DE VS MUX-DE COMPARISON                         | 112 |

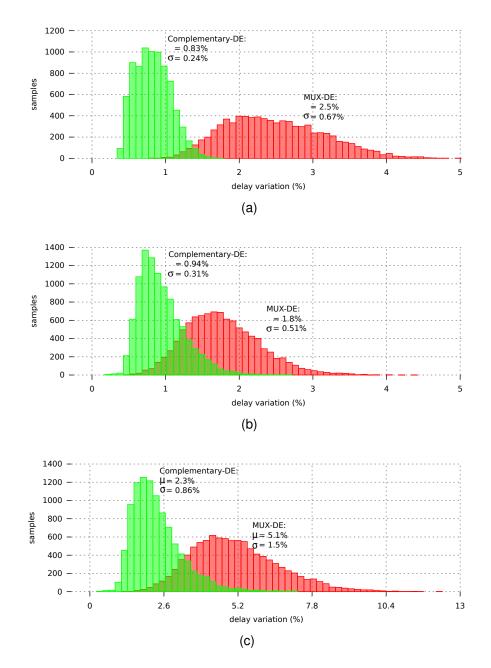

| 5.3.2 | DELAY MARGIN ANALYSIS                                             | 113 |

| 5.4   | RAZOR CLOCK GENERATION BASED ON THE COMPLEMENTARY-DE              | 119 |

| 6     | CONCLUSIONS AND FURTHER WORK                                      | 121 |

| 6.1   | THESIS ORIGINAL CONTRIBUTIONS                                     | 121 |

| 6.1.1 | THESIS CONTRIBUTIONS                                              | 121 |

| 6.1.2 | OTHER CONTRIBUTIONS                                               | 123 |

| 6.2   | FUTURE WORK                                                       | 124 |

|       | REFERENCES                                                        | 127 |

|       | <b>APPENDIX A</b> – The Parameterizable Complementary-DE Code     | 136 |

|       | <b>APPENDIX B</b> – Pin Placement in Complementary-DE synthesis   | 145 |

|       | APPENDIX C – List of Published Articles                           | 147 |

### 1. INTRODUCTION

The semi-conduction property of some chemical elements and compounds and the almost limitless exploitation of their potential enabled most of the technological feats in the recent history of Humankind. Silicon electronic devices were invented taking advantage of this property. The reliability of these devices compared to the available alternatives led to their increasing adoption and spurred the production of information processing systems that changed the speed and way with which many, if not most human activities are conducted. Discrete electronic devices evolved into Integrated Circuits (ICs) in silicon. The miniaturization of device dimensions and the mass manufacturing of these create the possibility of building highly complex information processing systems in very small packages at a very low cost. Small and cheap systems can be deployed easily everywhere. Based on Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs), most of these systems are widely used, being present in many home appliances as well as in satellites that orbit planets.

Very-Large-Scale Integration (VLSI) technology allows to put a complete Central Processing Unit (CPU) on a single chip since 1970 [Wol05]. In that time, synchronous circuit design techniques, which provide continuous time abstraction, help designers to easily design and fabricate complex circuits. The number of registers and clock-dependent gates did not pose a problem to distribute global signals such as clock and reset to all transistors involved. Today, the use of Deep SubMicron (DSM) technologies increases transistor integration density deeply, leading to devices that can exceed 30 billion transistors in a single chip [Gaz15].

The gains achieved by using DSM do not come free from problems. Global or semiglobal wires distribution, their delay determination and related effects constitute a highly complex problem in multi-billion-transistor designs. Clock, reset and power lines are examples of signals that require careful design. Effects that need tight control include, but are not restricted to:

- *i* The skew in clocks, caused by wire parasitic resistances and large capacitive loads;

- *ii* Voltage drops in power supply lines, affected by gate switching activity and by the relative length and resistivity of supply wires;

- iii Crosstalk in wide buses carrying data among chip modules.

Current methods and tools implemented in Electronic Computer Aided Design (ECAD or simply CAD) try to compensate such effects by specific techniques, like inserting buffers or deskewers (specific cells for handling clock delays) when automatically generating clock distribution trees. These solutions increase the IC area overhead and power consumption. According e.g. to Amde et al. [AFE<sup>+</sup>05], the power consumption for distributing a clock signal in a synchronous chip can reach up to 50% of the total chip power consumption.

| Table 1.1 - Low power Design Technology Improvements and Impact on Dynamic and Static |  |

|---------------------------------------------------------------------------------------|--|

| Power [ITR].                                                                          |  |

| DT Improvement                                  | Year     | Dynamic Power<br>Improvement (x) | Static Power<br>Improvement (x) | Description of Improvements                                                                  |

|-------------------------------------------------|----------|----------------------------------|---------------------------------|----------------------------------------------------------------------------------------------|

| Low Power Physical Libraries                    |          | 1.50                             | 1.50                            | Optimizing transistor size, layout style and cell<br>topology for the standard-cell library  |

| Back Biasing                                    | -        | 1.00                             | 1.35                            | Biasingwells of devices independently of the sources to shift the threshold voltage          |

| Adaptive Body Biasing (ABB)                     | -        | 1.20                             | 2.00                            | Delivering a positive or negative voltage below a transistor to reduce leakage               |

| Power Gating                                    | -        | 0.90                             | 10.00                           | Turning off the power supplies to idle blocks<br>for leakage reduction                       |

| Dynamic Voltage and Frequency<br>Scaling (DVFS) | -        | 1.50                             | 1.00                            | Dynamic management of supply voltage and operating frequency for power reduction             |

| Multilevel Cache Architecture                   | -        | 1.00                             | 1.20                            | Reduce amount of off-chip memory accesses for<br>performance improvement and power reduction |

| Hardware Multithreading                         | - Before | 1.00                             | 1.30                            | Using multithreads to improve hardware<br>utilization with leakage reduction                 |

| Hardware Virtualization                         | 2011     | 1.00                             | 1.20                            | Using one physical server to support multiple guest operating systems simultaneously         |

| Superscalar Architecture                        | -        | 1.00                             | 2.00                            | Parallel instruction issue and execution for<br>performance improvement and power reduction  |

| Symmetric Multiprocessing (SMP)                 | -        | 1.50                             | 1.00                            | Lowering the frequency by using multiple processors and parallel programing                  |

| Software Virtual Prototype                      | 2011     | 1.23                             | 1.20                            | Virtualization tools to allow the programmer to develop software prior to silicon            |

| Frequency Islands                               | 2013     | 1.26                             | 1.00                            | Designing blocks that operate at different frequencies                                       |

| Near-Threshold Computing                        | 2015     | 1.23                             | 0.80                            | Lowering Vdd to 400 - 500 mV                                                                 |

| Hardware/Software<br>Co-Partitioning            | 2017     | 1.18                             | 1.00                            | Hardware/software partitioning at the<br>behavioral level based on power                     |

| Heterogeneous Parallel<br>Processing (HPP)      | 2019     | 1.18                             | 1.00                            | Using multiple types of processors in a<br>parallel computing architecture                   |

| Many Core Software<br>Development Tools         | 2021     | 1.20                             | 1.00                            | Using multiple types of processors in a<br>parallel computing architecture                   |

| Power-Aware Software                            | 2023     | 1.21                             | 1.00                            | Developing software using power<br>consumption as a parameter                                |

| Asynchronous Design                             | 2025     | 1.21                             | 1.00                            | Non-clock driven design                                                                      |

In view of this situation and of a growing demand for low power devices, the International Technology Roadmap for Semiconductors (ITRS) [ITR] predicts the need for IC design paradigm changes. As presented in Table 1.1, the latest ITRS document available to date on IC design indicated the possibility of improvements on dynamic power by up to 23% using near-threshold voltage operation until 2015 and 21% gains through the adoption of asynchronous paradigm design in the following ten years targeting more energy efficient devices. Asynchronous design regained attention in several recent research works [BR07, CCGC10, ZSD10, CVPS11, Rab, LNS13, MAGC14, SHB+14, HHS+15, HMH+15, CLM+16, MCFB16, THG+16, HSL17]. This shows a trend to exploit this hardware design paradigm to develop low power ICs.

While synchronous circuits depend on the clock synchronization signal, asynchronous circuits employ handshake protocols to mediate data exchange. One classical asynchronous design template, the Quasi-Delay Insensitive (QDI), uses special information coding schemes to include part of the handshake signals within the data representation. This robust encoding combines control and data information, which provides an advantage when using a wide range of Voltage Scaling (VS) operation. Works such as [CL10, CCGC10, HCGC15] show QDI circuits properly operating in subthreshold voltages, achieving very low power dissipation. However, QDI coding schemes usually increase area overhead considerably, which implies low efficiency under nominal voltage. Also, QDI design often requires the use of special types of logic gates, but current commercial technologies Process Design Kits (PDKs) and cell libraries do not include such gates, which is a major impediment to improve CAD tool support to QDI design.

An alternative to design asynchronous circuit can more easily take advantage of current commercial CAD tools are to use Bundled-Data (BD) templates. Unlike QDI asynchronous design templates, BD templates use classical information binary coding and the handshake protocol relies on Delay Elements (DEs). BD is also highlighted for its potential to provide high performance, low power and area similar to that of synchronous designs [THK+05].

Due to the intrinsic characteristics of BD templates, their design flow is similar to conventional synchronous circuits. Thus, much of the developed CAD tools for synchronous design can be applied for BD design flows. The handshake protocol substitutes the traditional clock signaling by handshake mechanisms. A common assumption among these in BD design consists in using DEs, as discussed e.g. in [TB02, KHS07, SLKR13, GMMC15, RGP+15, HMH+15, THG+16, RDH+17]. DEs are responsible for ensuring that the computed data are stable in some module input when activation of the handshake control signals takes place.

DEs are widely used in digital and analog circuits. Most applications, especially the Radio Frequency (RF) domain, require an accurate delay value even under Process, Voltage or Temperature (PVT) variations. Thus, it is common that these elements are designed and evaluated for tolerance to PVT variations as discussed e.g. in [AESK+12, KKJ12, JKMK13, HHM+16]. However, BD circuit designers recognize that these changes inevitably affect the Combinational Logic (CL), which involves insertion of additional margins in delay elements [TB02, KHS07, SLKR13, HHC+15, RDH+17].

This Thesis deals with the investigation, design and evaluation of delay elements deemed for use in asynchronous bundled-data circuits and, to a minor extent, in synchronous circuits.

#### 1.1 Motivation

The challenge to modern IC designers are the tight power budgets that extend from mobile applications concerned with battery lifetime, to high-end server processors concerned with heat dissipation [HB13]. The power dissipation in ICs can be estimated by the sum of static power ( $P_{static}$ ) and dynamic power ( $P_{dynamic}$ ) like Equation 1.1 shows.

$$P_{total} = P_{static} + P_{dynamic} \tag{1.1}$$

Static power is produced independent of any circuit activity. It is related to the current that leaks ( $I_{leak}$ ) from the circuit. Dynamic power, on the other hand, comes from the circuit switching activity when wires change logic values. The switching activity in synchronous circuits is directly dependent on the clock frequency (*f*). In this case, Equation 1.1 can be rewritten as [WH11]:

$$P_{total} = I_{leak} \cdot V_{DD} + I_{avg} \cdot V_{DD} = I_{leak} \cdot V_{DD} + \alpha \cdot f \cdot C \cdot V_{DD}^2$$

(1.2)

where  $V_{DD}$  is the supply voltage,  $I_{avg}$  is the average current consumed during circuit switching,  $\alpha f$  is the effective switching frequency and *C* is the overall circuit capacitance.

Analyzing Equation 1.2, it is possible see two ways to handle power: change the frequency activity and changing the supply voltage. Dynamic Frequency Scaling (DFS) [WH11] [RLCM12] [HHM<sup>+</sup>15] is the easiest technique to reduce power in synchronous circuits, by changing clock period according to power constraints. However, the benefits of the technique in power grow linear and do not interfere in  $P_{static}$  values. Dynamic Voltage Scaling (DVS) is in turn more efficient to reduce power [RCN03, WH11]. In addition to linear static power dependence, dynamic power depends quadratically on the supply voltage. Nevertheless, gate delay also depends on the supply voltage, resulting in an interdependence between supply voltage and clock period [RCN03]. Because of this effect, many designers plead for the use of Dynamic Voltage and Frequency Scaling (DVFS) techniques instead of DVS [GJZ<sup>+</sup>17, MRSM17].

Despite the wide range of studies available involving the analysis and design of voltage scaling techniques in synchronous circuits, few works deal with the impact of VS in BD circuits. The lack of studies in BD covering VS is a relevant and so far neglected research field, specially with regard to impacts of VS in delay elements. This constitutes a basic motivation for the research proposed herein.

#### **1.2 Description of the Problem to Address**

Bundled-data templates use delay elements to provide the self-timed characteristic of asynchronous circuits [SF13]. However, the structure and physical characteristics of DEs are distinct from those of their associated combinational logic.

Usually, it is easy to match the combinational logic delay with the DE delay for specific process, voltage and temperature conditions. However, as DEs employ specific gates or cells, that often are not those used to build combinational logic, when process, voltage or temperature vary, the delay produced in these two circuit parts may evolve in

different ways. The usual solution in this case is add delay margins in DEs to guarantee a minimum delay that considers the worst case scenario, which may result losses in area, power and performance. In this case, performance in BD templates can be bad, even worse than that of a synchronous solution.

To reduce the delay margin effects, one of the most efficient solutions is to implement programmable DEs. Programmable DEs allow adjustments in the produced delay to increase performance. Basically, programmable DEs can be adjusted at design time or at runtime. However, voltage variations can affect circuitry faster than it can be sensed and compensated [WH11], producing unexpected delays and resulting in timing violations. Alternatives to handle timing violation using resilient circuit design techniques have recently received attention and variant design techniques now exist for BD circuits.

By now, it should be clear the importance of modeling the delay behavior in delay elements and other gates and reference these changes to voltage scaling. Understanding how the delay behavior of logic is affected, it can be possible to predict the impact of VS in both DE and data processing logic, thus reducing the need to add delay margins.

It is also important to indicate how to design DEs for BD with focus on correct operation and high performance reducing margins even under VS. Obviously, discrepancies between how delay parameters in DEs and in the remainder of the circuit change cannot interfere in circuit functionality.

Despite resilient alternatives to BD design templates can circumvent or recover from timing violation, this architecture can add complexities in the design and production of systems that were not previously considered. This shows the importance of analyzing and proposing techniques to reduce the complexity of designing and producing this kind of circuits.

### 1.3 Goals

Given the exposed motivation and the description of the problem to address, the strategic goal of this Thesis is to propose a set of contributions that enhance the delay element design for bundled-data asynchronous design templates.

To accomplish this strategic goal, the following set of specific objectives were defined:

- 1. To develop a model enabling to evaluate voltage scaling effects in delay elements and other parts of a circuit;

- 2. To evaluate the voltage scaling impact in DEs;

- 3. To analyze resilient alternative for BD templates;

4. To reduce the need to add delay margins in DEs and combinational logic.

#### 1.4 Originality of this Thesis

This work has its roots in the DE delay margin reduction for bundled-data templates under voltage scaling. The paper [HHS<sup>+</sup>15] approached for the first time the voltage scaled delay ratio modeling of cells. It also evaluates three classical programmable delay elements usually implemented in bundled-data templates. This paper was presented at the 2015 VLSI Design conference and its results are extended in this Thesis.

Another original contribution is the proposition of how to design a programmable DE to reduce voltage scaled delay ratio variations. A new delay element is proposed focused in this point. Obtained improvements are around 90% better results when compared with other solutions, for selected relevant parameters.

Voltage scaling affects not only delay but may change functionality. It is necessary to guarantee manufactured devices work properly. A brief analysis about delay test complexity is brought here mainly concentrated in small delay defects and on the resilient BD alternative. The necessity of reducing the number of test runs is highlighted.

Focusing on test runs reduction, a novel delay element for resilient BD templates is proposed. The main characteristic of this DE is to reduce process variation impact during DE reconfiguration. The Thesis shows that the reduction in delay margin can reduce the number of test runs or at least can improve test coverage. Delay margins are reduced by at least 67% and this can reach up to 88% reduction in recent technologies. The new DE can be implemented as part of a clock generator for resilient synchronous templates as well.

All Thesis experiments are replicated for three widely distinct commercial technologies to properly validate the research predictions. Two of these are bulk CMOS technologies and the third is based on fully depleted silicon on insulator devices.

### 1.5 Document Structure

The remaining of this document comprises five Chapters. Chapter 2 presents basic definitions and concepts used in this volume. Next, Chapter 3 proposes an analysis of voltage scaling impacts in delay. The Voltage Scaled Delay Ratio (*VSDR*) model is also discussed in this Chapter. Tree different delay elements are evaluated and a new one is proposed to reduce *VSDR* margin. Chapter 4 brings a procedure for delay fault tests in BD templates, focusing on delay elements characteristics. This Chapter includes the impact of voltage scaling in time and number of test runs. It also shows an alternative to detect

small delay defects in BD templates using the resilient BD template. Chapter 5 discusses the peculiarities of resilient BD design template, with target on two-DEs implementation. Alternatively, it brings the proposal of a new DE, designed to reduce delay margins from process variations under dynamic configuration. Finally, Chapter 6 presents a set of final considerations and discusses future work. Note that each chapter in this Thesis presents a revision of the state-of-the-art relative to its content when this makes sense.

### 2. AN OVERVIEW OF BASIC CONCEPTS

This Chapter provides an introductory overview of several concepts that serve as basis for the work developed in this Thesis. It starts with a discussion of the classical synchronous circuit design process, in Section 2.1. This Section also approaches some contemporary synchronous circuit design techniques based on error resiliency, and addresses some of their characteristic issues. Next, Section 2.2 addresses the problem of designing asynchronous circuits, scrutinizing different ways to design them. The Section also covers an alternative bundled-data asynchronous template, with error resiliency capabilities. Section 2.3 explores some specifically relevant information on the main electronic component addressed in this work, the Metal Oxide Semiconductor (MOS) Field Effect Transistor (FET). The diversity of delay elements for bundled-data design are the subject of Section 2.4. Finally, Section 2.5 brings some fundamental concepts related to the test of Integrated Circuits (ICs), including topics on delay fault tests with focus on the voltage scaling impact on postsilicon tests of synchronous digital ICs. Alongside the discussion, this Chapter establishes a precise terminology employed throughout the rest of the document.

### 2.1 Synchronous Circuit Design

According to Calazans [Cal98], a digital design allows abstracting input or output signals from physical quantities such as voltage and current into discrete signals with a numerical representation. This characteristic allows increasing the circuit design abstraction level, facilitating the process of complex information handling. Another possible abstraction level includes treating time as a discrete variable that can be associated to the just mentioned digital signal abstraction. If time is taken as a set of discrete equally spaced moments in time domain, the digital signal is called *synchronous*. The usual way to discretize time relies on the use of a periodic control signal called *clock*. The clock simultaneously controls every action in a digital system. When a digital signal does not rely on a discrete notion of time, it is denominated an *asynchronous* signal.

This Section introduces and explains the basic concepts about the classical synchronous approach, based on information representation using synchronous signals. It also explores the synchronous resilient template proposed in the past to improve performance and/or power efficiency of digital circuits.

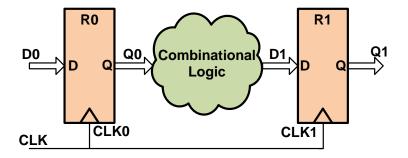

Figure 2.1 – A typical stage of a synchronous circuit.

### 2.1.1 The Classical Synchronous Circuit Design Approach

A digital circuit that uses exactly one periodic control signal to control all its registers, is a synchronous circuit [RCN03]. The clock simultaneously updates all registers, allowing an orderly data propagation process along all IC modules. Through this simple concept, the synchronous paradigm allows the hardware developer to abstract timing issues almost completely, facilitating the design of ICs enormously. For this reason, most digital designs employ this paradigm, even if locally, in the case of current complex systems.

A conventional synchronous digital circuit usually consists of a set of stages composed by registers that encircle a piece of Combinational Logic (CL), as depicted by the example stage of Figure 2.1. The use of registers controlled by a same clock allows that data present in the output of a register Q0 remain stable between clock ticks, which control their propagation through the CL between two successive clock edges. When the second of two successive edges occurs, data present at input *D1* of register *R1* is stored and propagated to output *Q1*. Equation 2.1 based on [RCN03] allows determining the minimum clock period ( $t_{clk(n)}$ ) for a given circuit stage *n*, by summing the time the first register *R0* takes to propagate its input to the output ( $t_{p_{R(n)}}$ ), the computation time required by the CL ( $t_{p_{CL(n)}}$ ) and the setup time of the next register ( $t_{setup_{R(n+1)}}$  of *R1*). Since the clock signal is global, its minimum period is the minimum time necessary to satisfy all instances of Equation 2.1, for all stages in the circuit.

$$t_{clk(n)} \ge t_{p_{R(n)}} + t_{p_{CL(n)}} + t_{setup_{R(n+1)}}$$

(2.1)

Conceptually, a synchronous circuit connects the clock signal to all circuit registers [RCN03]. However, variations caused by the wires used to route the clock, as well as gate and parasitic capacitances can affect the clock propagation delay. *Clock skew* is the generic denomination of the effect that dictates that the clock signal might not reach all registers exactly at the same time.

According to Rabaey et al. [RCN03], the clock skew implies loss of performance and functionality in digital systems. When considering a clock skew effect of value d (in

seconds) between two points where the clock connects to registers *CLK0* and *CLK1* in Figure 2.1, the circuit could operate at a higher frequency than previously defined, according to Equation 2.2. However, *d* also involves adding extra time to maintain the hold time of registers, as Equation 2.3 shows. It is important to highlight the skew uncertainty at each stage [DS94]. Due to long distances, effects such as crosstalk, power distribution and other manufacturing discrepancies can affect the clock skew. These variations in skew result in time margins, which in turn reduce the frequency, causing performance degradation.

$$t_{Clk(n)} \ge t_{\rho_{R(n)}} + t_{\rho_{CL(n)}} + t_{setup_{R(n+1)}} - d$$

(2.2)

$$t_{hold_{R(n)}} < t_{p_{R(n)min}} + t_{p_{CL(n)min}} - d$$

$$(2.3)$$

Skew effects can be quantitatively significant. Accordingly, Computer Aided Design (CAD) tools try to compensate this effect by inserting buffers or dedicated elements to "deskew" the clock, i.e. to reduce clock skew. However, in recent technologies, the price paid to keep clock skew within tolerable values can be significant as pointed out, for example, in references like [LSGB11], [SRG+01] and [SGB11].

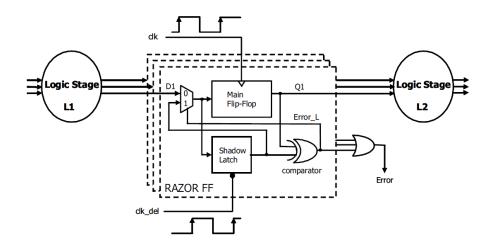

#### 2.1.2 The Resilient Synchronous Circuit Design Approach

Energy consumption is one of the most relevant issues in most current digital systems, from high-performance servers to portable devices. To cope with the energy-performance trade-off it is necessary to employ innovative circuit architectures. One family of such architectural innovations appeared along the proposal of the Razor approach to design synchronous digital circuits [EKD+03, DTP09, KKFK13, FFKP13]. Razor is a family of resilient synchronous techniques proposed by Ernst et al. consisting in adopting speculative operation techniques for circuit design. Originally designed for voltage scaling applications, Razor circuits can operate at a frequency higher than that predicted by the use of worst-case delay margins. Of course, this implies the circuit will eventually incur in timing violations. When such violations do occur, special circuits detect it and trigger the on-the-fly execution of error correction procedures.

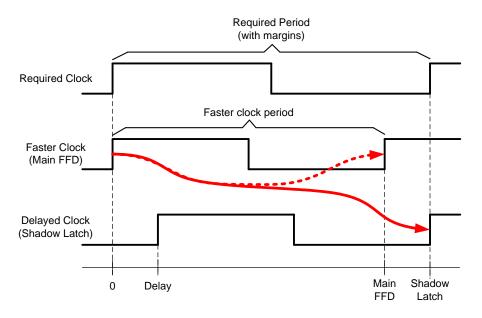

As Figure 2.2 shows, using a delayed version of the clock, a shadow latch collects data computed after the main flip-flop. The design of the shadow latch and of the delayed clock guarantee that the computed worst-case delays of the circuit are always respected. If data collected in these two latches differ, the circuit indicates an error and the data stored in the shadow latch replace the contents of the flip-flops in the circuit data flow.

However, the authors of [EKD<sup>+</sup>03] show that precautions are necessary when computing the delay applied to the clock. If the delay is too small, data collected in the shadow

Figure 2.2 – The original Razor design template, as proposed in [EKD+03].

latch can sample the same (wrong) value of the main flip-flop, not signaling the error while the CL is still computing. If the delay is longer than the ideal, the latch may loose computed data and get a next data, which also causes incorrect operation.

Razor can detect incorrectly stored data, but the clock dependency makes the circuit sensitive to skew. Metastability on the main flip-flop, possibly caused by an early clock edge (with regard e.g. to too long a computation taking place in the Logic Stage *L1*) can also propagate to the error signaling gate, maybe taking the entire circuit to an unknown state [HMH<sup>+</sup>15]. Thus, it is natural to consider asynchronous design paradigms as an alternative to Razor. Studies such as the ITRS [ITR] indicate a continuous trend of migration from the use of synchronous to asynchronous signaling. The next Section briefly explores the scene of asynchronous circuit design as it stands today.

### 2.2 The Asynchronous Circuit Design Approach

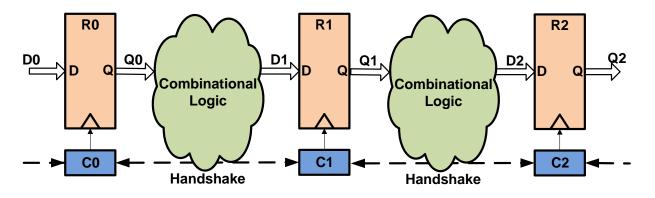

Asynchronous designs, unlike synchronous ones, do not abstract time, obliging designers not only to reason about the logic, but also to consider a large amount of time constraint effects during design [SF13]. Asynchronous circuits employ, instead of clock tree, handshake processes between registers to perform synchronization, communication and sequencing of operations [BOF10, SF13]. Thus, asynchronous circuits can potentially lead to lower power consumption, higher operation speed, less emission of electromagnetic noise, more robustness towards PVT variations, better composability and modularity and avoid-ance of global clock distribution and the associated clock skew problems.

In a more abstract view, the control of asynchronous circuits relies on token handling. Consider for example Figure 2.3. For some data to be stored and be available at the output Q1 of register R1, controller C1 requires two tokens. One comes from the predecessor circuit that informs data is stable in D1 to be stored. The other comes from the next

Figure 2.3 – An example of an asynchronous pipeline circuit segment.

Figure 2.4 – Handshake protocols: (a) 4-phase and (b) 2-phase.

control circuit, *C2*, which indicates data in its register was consumed (*R2* being thus free to receive new data).

Considering the manipulation of logic tokens as a criterion, asynchronous circuits can be grouped into two major classes: Bundled-Data (BD) and Delay Insensitive (DI) circuits. In the first class, control tokens flow through dedicated (control) channels only, which run parallel to the CL blocks and the data paths. In the second class of circuits, data available tokens usually mingle with data in data paths (through the use of special DI codes), while the data consumed token usually employs a dedicated control channel.

### 2.2.1 The Bundled-Data Asynchronous Circuit Design Approach

The term Bundled-Data (BD) refers to a situation where data signals use ordinary Boolean encoding to carry information, and where separate request and acknowledge lines control the flow of data as a bundle [SF13]. According to the use of level or transition signaling, there are two types of communication protocols useful to pass tokens between controllers: 4-phase and 2-phase protocols. Figure 2.4 illustrates these two protocol types.

In the 4-phase protocol, shown in Figure 2.4(a), both the request (*req*) and acknowledge (*ack*) wires use Boolean levels to carry information and 4 summarizes the number of

Figure 2.5 – The organization of (a) Push and (b) Pull data channels in BD asynchronous designs.

steps taken for one information exchange action. Initially assume, without loss of generality, that both wires are at '0'. To pass a token, the protocol requires four steps:

- The sender issues data and sets *req* to '1' (for example, in Figure 2.3 *C0* sends a token to *C1*);

- 2. The receiver absorbs the data and sets *ack* to '1';

- 3. The sender responds by taking req to '0';

- 4. The receiver acknowledges this, by making *ack* low (in Figure 2.3, *C1* sends a token back to *C0*).

The main disadvantage of using this kind of protocol are the mandatory return-tozero phases, which cost time and energy. 2-phase protocols, shown in Figure 2.4(b) allow the use of only one transition of each signal to transmit data. In this protocol, there is no difference between '0'  $\rightarrow$  '1' or '1'  $\rightarrow$  '0' transitions, because both represent a "signal event". Thus, the protocol has only two steps:

- 1. The sender issues data and changes req (C0 sends a token to C1);

- 2. The receiver absorbs the data and changes ack (C1 sends a token back to C0).

Another classification for BD circuits refers to how controllers command the send/receive data channel. Each of these acts as an active or passive entity. An active entity initiates a communication, sending or receiving data from another controller, the passive entity. Thus, when data come from the side of the active entity, it constitutes a *push channel*, i.e. data follow the same direction as *req* (see Figure 2.5(a)). If the producer is on the passive entity side, this characterizes a *pull channel*, where data flow with the passive entity acknowledge signal, according to what appears in Figure 2.5(b). The next characteristic of BD circuits to explore is the requirement of delay elements.