# PONTIFÍCIA UNIVERSIDADE CATÓLICA DO RIO GRANDE DO SUL FACULDADE DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DE COMPUTAÇÃO

# Design and Exploration of 3D MPSoCs with on-Chip Cache Support

### **RODRIGO CADORE CATALDO**

Submitted in partial fulfilment of the requirements for the degree of Master of Science in Computer Science at Pontificia Universidade Católica do Rio Grande do Sul.

Advisor: César Augusto Missio Marcon Co-Advisor: Débora da Silva Motta Matos

Porto Alegre, Brazil

December 2015

# Dados Internacionais de Catalogação na Publicação (CIP)

C357d Cataldo, Rodrigo Cadore

Design and exploration of 3D MPSoCs with on-chip cache support / Rodrigo Cadore Cataldo. -2015. 129 f.

Diss. (Mestrado) – Faculdade de Informática, PUCRS. Orientador: Prof. Dr. César Augusto Missio Marcon. Co-orientador: Prof<sup>a</sup>. Dr<sup>a</sup>. Débora da Silva Motta Matos.

Multiprocessadores.

Energia Elétrica – Consumo.

Arquitetura de Computador.

Informática.

Marcon, César Augusto Missio.

Matos, Débora da Silva Motta.

Título.

CDD 23 ed. 004.35

Ramon Ely CRB 10/2165 Setor de Tratamento da Informação da BC-PUCRS

# Pontifícia Universidade Católica do Rio Grande do Sul

FACULDADE DE INFORMÁTICA

PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

# TERMO DE APRESENTAÇÃO DE DISSERTAÇÃO DE MESTRADO

Dissertação intitulada "Design and Exploration of 3D MPSoC with On-Chip Cache Support" apresentada por Rodrigo Cadore Cataldo como parte dos requisitos para obtenção do grau de Mestre em Ciência da Computação, aprovada em 4 de março de 2016 pela Comissão Examinadora:

| leen Angoto Himis Vangan                                             |                      |

|----------------------------------------------------------------------|----------------------|

| Prof. Dr. César Augusto Missio Marcon-<br>Orientador                 | PPGCC/PUCRS          |

| Debord etto                                                          |                      |

| Profa. Dra. Débora da Śilva Motta Matos –<br>Coorientadora           | UERGS                |

| Prof. Dr. Fernando Gehm Moraes –                                     |                      |

| Prof. Dr. Fernando Gehm Moraes –                                     | PPGCC/PUCRS          |

| Martha Johanna Sypilveda F.                                          |                      |

| Profa. Dra. Martha Johanna Sepúlveda Florez - EI SEC TU              | JM - Munich/Alemanha |

|                                                                      |                      |

| Homologada em $30./26./3016$ , conforme Ata No. $0.13$ Coordenadora. | . pela Comissão      |

| Merican                                                              |                      |

| Prof. Dr. Luiz Gustavo Leão Fernandes<br>Coordenador.                |                      |

|                                                                      |                      |

Av. Tr

Campus Central Av. Ipiranga, 6681 – P. 32 – sala 507 – CEP: 90619-900 Fone: (51) 3320-3611 – Fax (51) 3320–3621

E-mail: <u>ppgcc@pucrs.br</u>

CIÊNCIA DA COMPUTAÇÃO E-mail: ppgcc@pucrs.br www.pucrs.br/facin/pos

# PROJETO E EXPLORAÇÃO DE MPSOCS 3D COM SUPORTE A CACHES INTRACHIP

### **RESUMO**

Avanços na tecnologia de fabricação de semicondutores permitiram implementar um sistema computacional completo em um único chip, em inglês de *System-on-Chip* (SoC). SoCs integram múltiplos elementos de processamento (PEs), componentes de memória e dispositivos de entrada/saída. Este trabalho emprega o termo inglês *Multiprocessor System-on-Chip* (MPSoCs) para um SoC que integra múltiplos PEs cooperantes.

À medida que o número de PEs aumenta em um MPSoC, torna-se necessário o uso de arquiteturas que proveem escalabilidade e concorrência da comunicação. A rede intrachip, em inglês *Network-on-Chip* (NoC), que interconecta o sistema através de roteadores distribuídos no chip foi proposta para atender estes requisitos.

O sistema de interconexão também deve prover recursos para atender a comunicação entre PEs e módulos de memória. Infelizmente, trabalhos prévios demonstraram que basear toda a comunicação de memória com uma NoC não é adequado para atender os requisitos de latência. Além disso, muitas propostas baseadas em NoC descartam o suporte à programação do tipo memória compartilhada que permanece um requisito básico de aplicações paralelas.

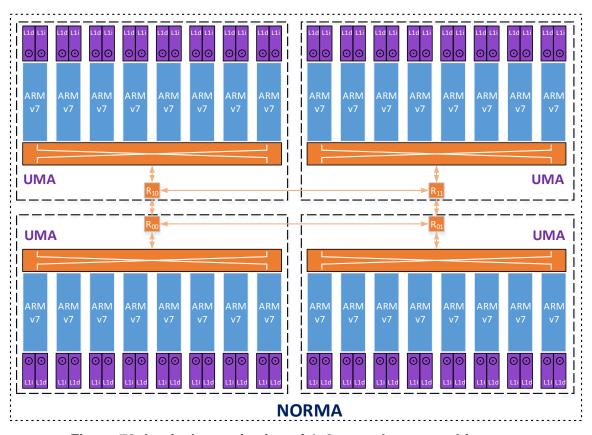

A principal contribuição deste trabalho é o projeto e exploração experimental de MPSoCs 3D com suporte a caches intrachip que empregam uma matriz de chaveamento com suporte à coerência de cache para comunicação entre PEs e a hierarquia de memória, e uma NoC para a intercomunicação de PEs, devido à sua eficiência em transmitir pequenos pacotes e sua escalabilidade.

Resultados experimentais foram realizados com o simulador Gem5 utilizando o conjunto de instruções da ARM e dois benchmarks: PARSEC e NASA NAS. Os resultados foram organizados em três conjuntos de avaliação:

- 1. Avaliação da memória principal utilizando memórias emergentes baseadas em tecnologias 3D e duas memórias tradicionais para desktops: Double Data Rate (DDR) e Low Power (LP) DDR. Para a pluralidade das aplicações, memórias emergentes resultaram em um impacto igual ou menor que 10% de acréscimo no tempo de execução provendo significativa redução no consumo de energia, quando comparadas às memórias tipo DDR;

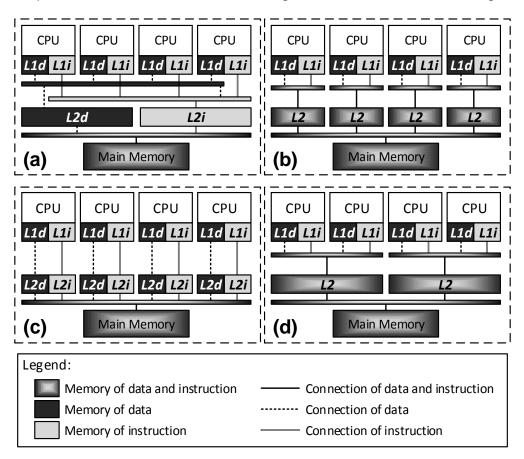

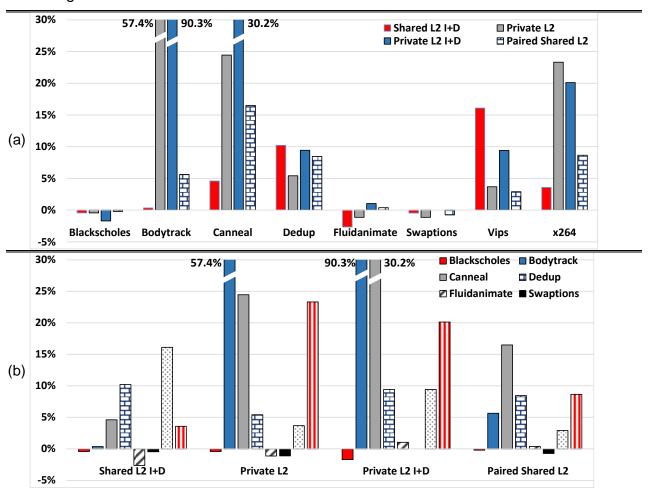

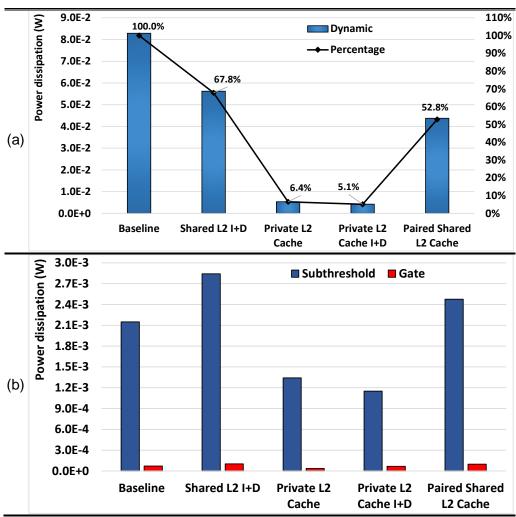

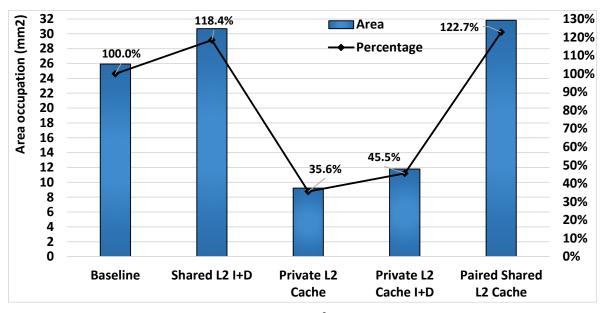

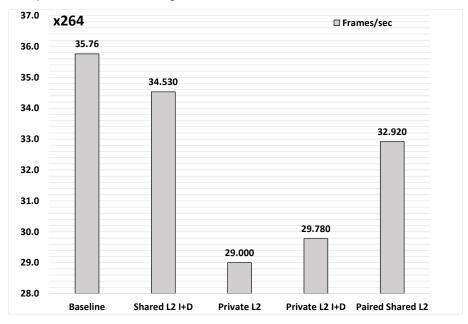

- 2. Avaliação de caches utilizando cinco arquiteturas de cache e explorando seus efeitos no tempo de execução de aplicações e consumo de energia. Foram exploradas três arquiteturas compartilhadas e duas arquiteturas privadas em caches L2. Para a maioria das aplicações, a tradicional arquitetura compartilhada da L2 mostrou o melhor tempo de execução. Entretanto, para o consumo de energia, as arquiteturas L2 privadas obtiveram os melhores resultados;

- 3. Avaliação da escalabilidade do sistema proposto. Os experimentos utilizaram vários tamanhos de *clusters* e aplicações baseadas em troca de mensagens.

**Palavras Chave**: MPSoC baseado em NoC, MPSoC 3D, Hierarquia de memória, Coerência de cache, MPSoC com suporte a caches intrachip.

# DESIGN AND EXPLORATION OF 3D MPSOCS WITH ON-CHIP CACHE SUPPORT

### **ABSTRACT**

Advances in semiconductor manufacturing technology have allowed implement the whole computing system into a single chip, which is namely System-on-Chip (SoC). SoCs integrate several processing elements (PE), memory components and I/O devices. This work employs the term Multiprocessor Systems-on-Chip (MPSoCs) to SoCs that integrate several cooperating PEs.

The increasing quantity of PEs in an MPSoC demands the use of architectures that provide scalability and concurrent communication. The Network-on-Chip (NoC) that interconnects the system through distributed routers has come to tackle these requirements.

The interconnection system must also provide resources to fulfil the communication between PEs and memory modules. Unfortunately, previous works have shown that a single packet-based NoC is not well-suited to provide scalability and low latency for cache supported systems. Additionally, many NoC-based designs lack support for a shared-memory programming model that is an essential requirement for most of the parallel applications.

The main contribution of this work is the design and experimental exploration of 3D MPSoCs with on-chip cache support that employ a crossbar-based infrastructure for the cache-coherent memory hierarchy, and a packet-based NoC for inter-processor communication, due to its efficiency in travelling small packets and its benefits to ever-increasing scalability requirements.

Experimental results performed on the Gem5 simulator using the ARM's ISA and PARSEC and NASA NAS benchmarks were conducted under three evaluations scenarios:

- Main memory evaluation using emerging 3D memory technologies and two traditional desktop memories: Double Data Rate (DDR) and mobile Low Power (LP) DDR. For the plurality of the applications, the emerging 3D memory technologies had less or equal than 10% of runtime execution increase providing significant energy saving when compared with DDR memories;

- 2. Cache evaluation using five cache architectures and exploring its effects on execution runtime and energy consumption. Three shared L2 cache designs and two private L2 cache design were explored. For the majority of the applications evaluated, the traditional shared L2 design had the lowest execution runtime. However, the private L2 designs showed the lowest energy consumption;

- 3. Scalability evaluation of the proposed system. Experiments using various sizes of clusters and applications based on message exchange.

**Keywords**: NoC-based MPSoC, 3D MPSoC, Memory hierarchy, Cache coherence, MPSoC with on-chip cache support.

# **LIST OF FIGURES**

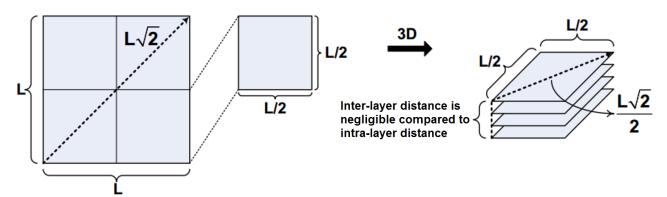

| FIGURE 1. V  | VIRING LENGTH OF SIMPLE LAYER VS A STACK OF SMALLER LAYERS [L106]            | 21       |

|--------------|------------------------------------------------------------------------------|----------|

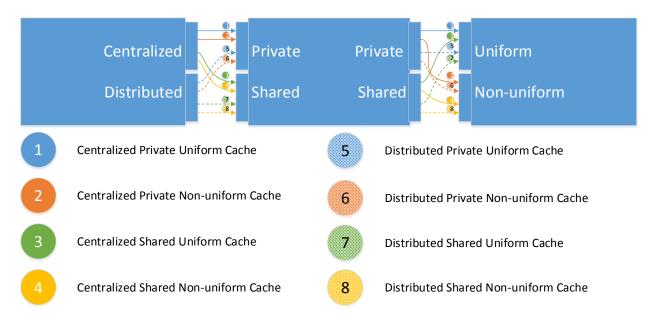

|              | EIGHT CATEGORIES OF CACHE ARCHITECTURES DERIVED FROM [BAL11]                 |          |

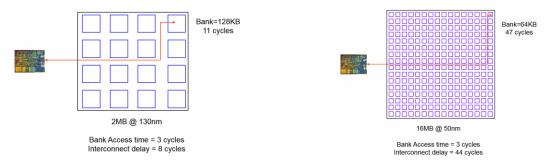

|              | EFFECT OF INCREASING DATA BANKS ON MULTI-BANKED L2 CACHES [LEE15A]           |          |

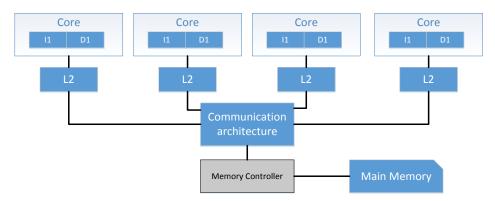

|              | SCHEMATIC EXEMPLIFICATION OF AN MPSOC WITH CACHE HIERARCHY COMPOSED BY       |          |

| 1 100KL 4. ( | PRIVATE L1 AND L2 CACHES (BASED ON [ASA09])                                  |          |

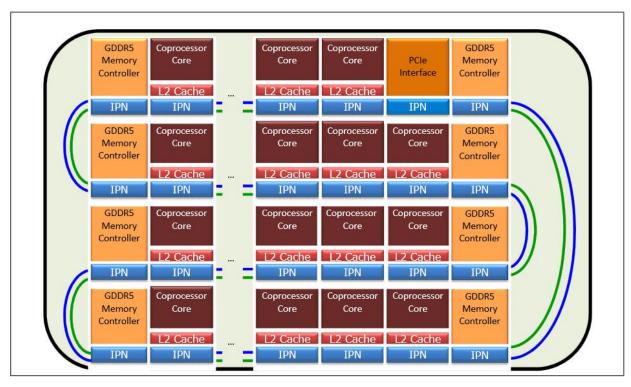

| FIGURE 5     | CONCEPTUAL DIAGRAM OF THE STRUCTURE OF THE INTEL XEON PHI COPROCESSOR        |          |

| I IGURE 3.   | [INT14]                                                                      |          |

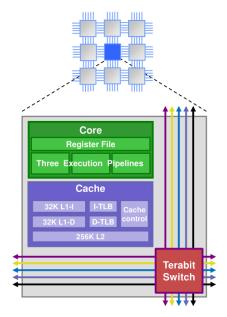

| FIGURE 6 C   | GENERAL-PURPOSE CORE UNIT OF TILE-GX100 [TIL118]                             | 20       |

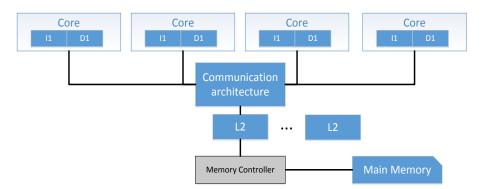

|              | SCHEMATIC ILLUSTRATION OF AN MPSOC WITH SHARED L2 CACHES (BASED ON           |          |

|              |                                                                              |          |

|              | [ASA09])                                                                     | 29       |

| FIGURE 8. F  |                                                                              |          |

| F 0 6        | [STA15][STA15][STA15]                                                        |          |

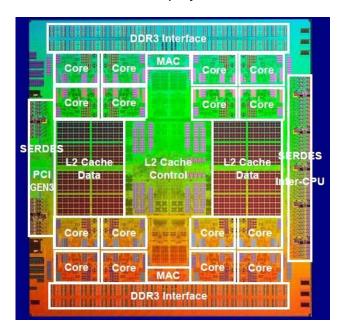

| FIGURE 9. S  | SPARC64-X DIE CONTAINING 16 CORES AND 4 BANKS OF L2 CACHE [REG15]            | 30       |

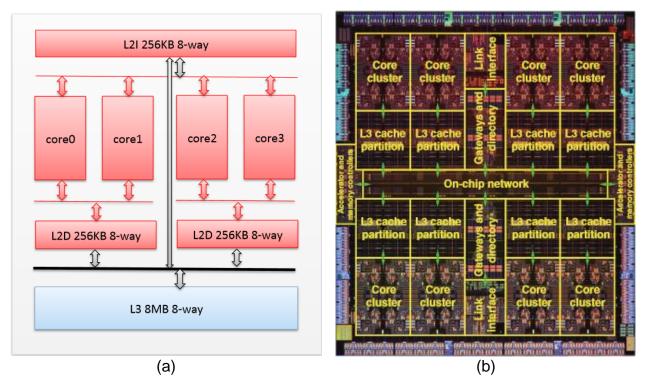

| FIGURE 10.   | SPARC M7: (A) SCHEMATIC OF CORE CLUSTER DESIGN, AND (B) CHIP LAYOUT [SIV14]. |          |

| _            |                                                                              |          |

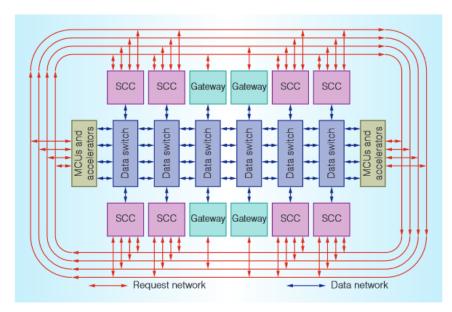

| FIGURE 11.   | ON-CHIP NETWORK REQUEST AND DATA TOPOLOGY. THE RESPONSE NETWORK IS           |          |

|              | OMITTED IN THIS REPRESENTATION [AIN15].                                      | 31       |

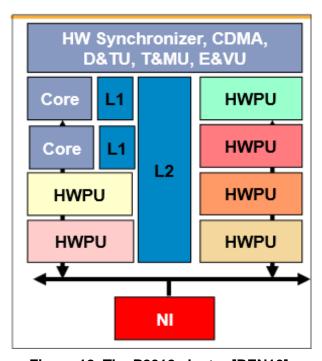

|              | THE P2012 CLUSTER [BEN10].                                                   |          |

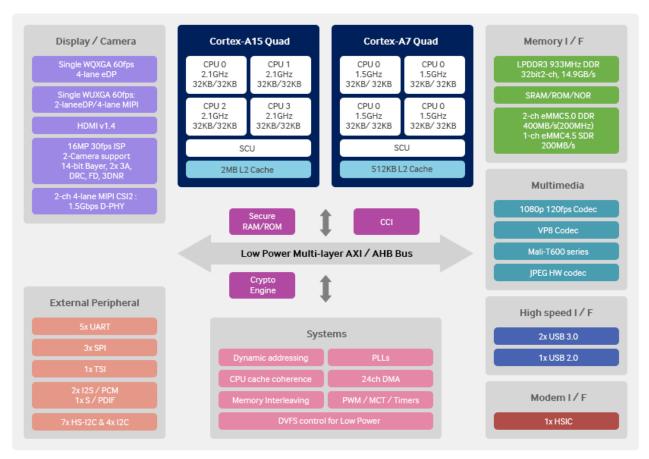

|              | ARCHITECTURE OF THE EXYNOS 5 OCTA SOC [SAM15A]                               |          |

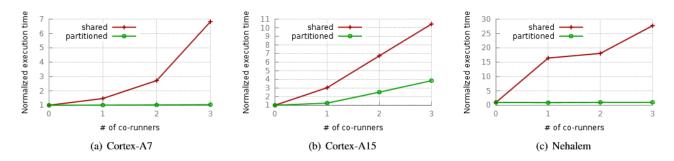

| FIGURE 14.   | NORMALIZED EXECUTION TIME FOR THREE SYSTEM CONFIGURATIONS [YUN15]            | 35       |

| FIGURE 15.   | EFFECTIVENESS OF CACHE ISOLATION IN (A) IN-ORDER CORES AND (B) O3 CORES      |          |

|              | [YUN15]                                                                      | 36       |

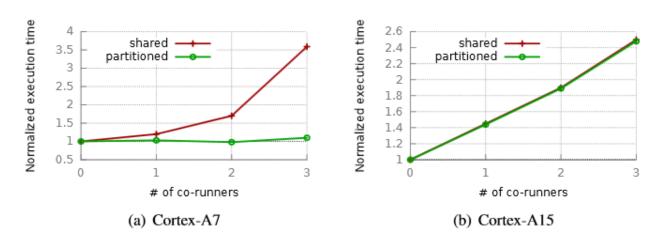

| FIGURE 16    | S. From single multithreaded to CMP and clustered multithreaded              |          |

|              | ARCHITECTURE (BASED ON [ELM05])                                              | 37       |

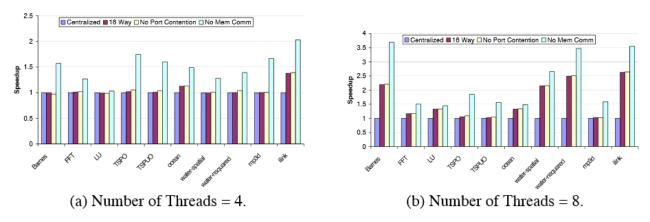

| FIGURE 17.   | PERFORMANCE OF THE CENTRALIZED CACHE [GAR05].                                | 37       |

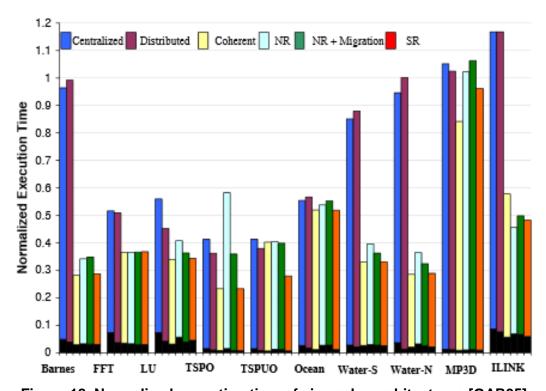

| FIGURE 18.   | NORMALIZED EXECUTION TIME OF SIX CACHE ARCHITECTURES [GAR05]                 | 38       |

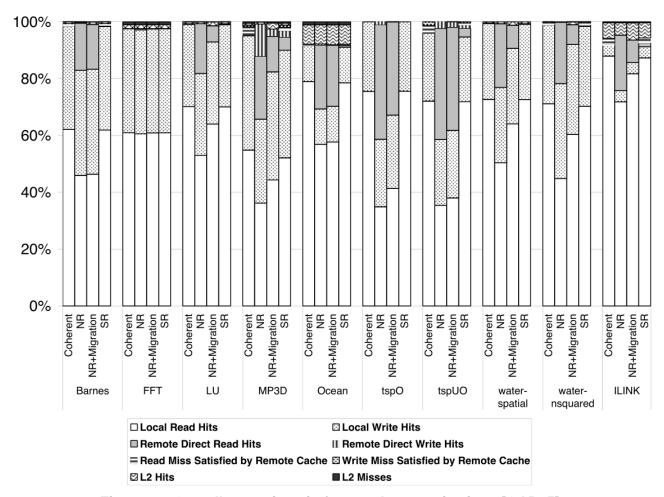

|              | OVERALL OPERATIONS IN FOUR CACHE ORGANIZATIONS [GAR05].                      |          |

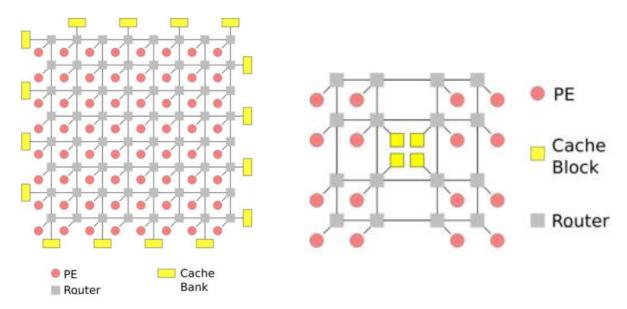

|              | TWO OF EIGHT L2 CACHE DESIGNS STUDIED ON A 2D MPSoC [YE10]                   |          |

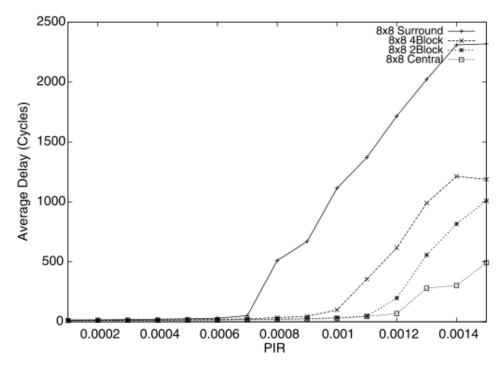

|              | AVERAGE DELAY OF FOUR L2 CACHE DESIGNS ON THE 8×8 2D MPSoC [YE10]. PIR IS    |          |

| 00.1.2 2     | THE PACKET INJECTION RATE EXPRESSED IN PACKETS PER CYCLE                     |          |

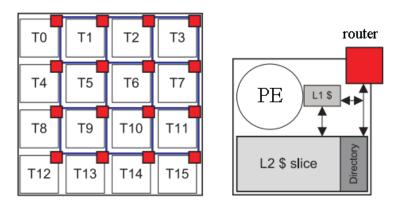

| FIGURE 22    | SIXTEEN CORE TILES (LEFT) AND THE DESIGN OF A SINGLE CORE (RIGHT) (BASED ON  |          |

| I IOOKL ZZ.  | [CHO06]).                                                                    |          |

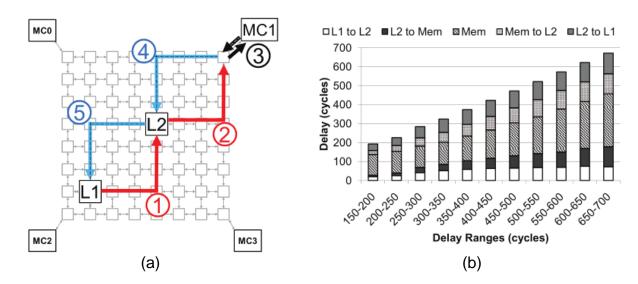

| FIGURE 23    | DETAILED FLOW (A) AND DELAY (B) OF MEMORY REQUESTS AND RESPONSES [SHA12].    |          |

| FIGURE 24    | WORKLOAD EMPLOYED BY SHARIFI ET AL. [SHA12].                                 | 43<br>44 |

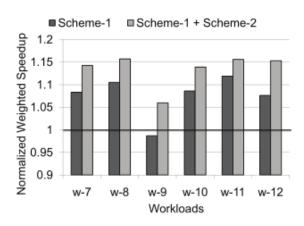

|              | NORMALIZED SPEEDUP FOR MEMORY INTENSIVE WORKLOADS [SHA12].                   |          |

|              | • •                                                                          |          |

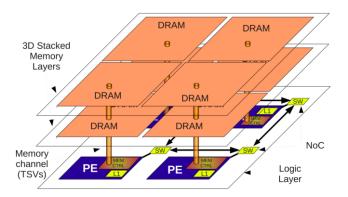

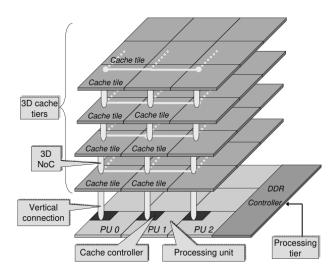

| FIGURE 20.   | 3D HARDWARE ARCHITECTURE [LOI10]                                             |          |

| FIGURE 27.   | ILLUSTRATION OF THE ARCHITECTURE PROPOSED BY [LOI10]                         | 40       |

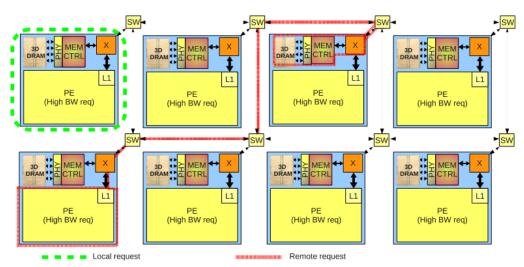

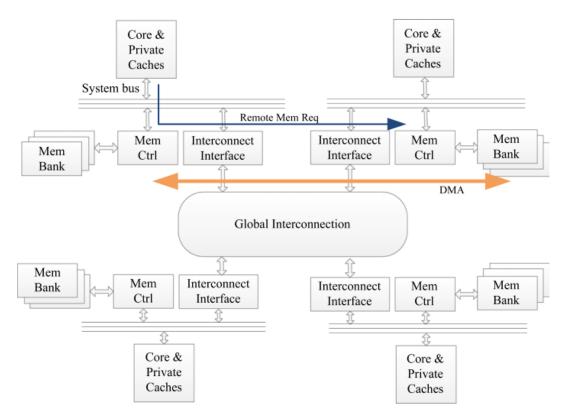

|              | DISTRIBUTED MEMORY WITH DIRECT ACCESS MODEL [FU14].                          |          |

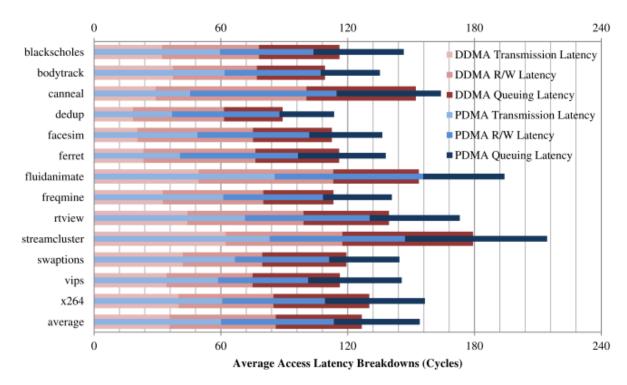

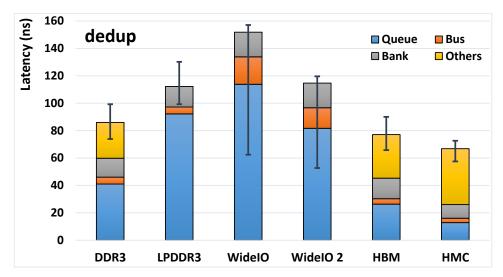

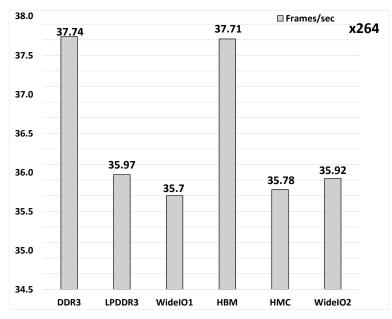

|              | . AVERAGE ACCESS LATENCY BREAKDOWN FOR THE PARSEC BENCHMARK SUITE            |          |

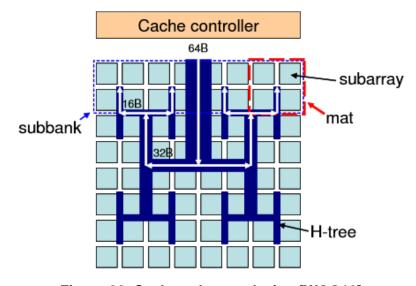

| <b>5</b>     | [FU14]CACHE SUBARRAY DESIGN [WOO10]                                          | 47       |

| FIGURE 30.   | CACHE SUBARRAY DESIGN [WOO10].                                               | 47       |

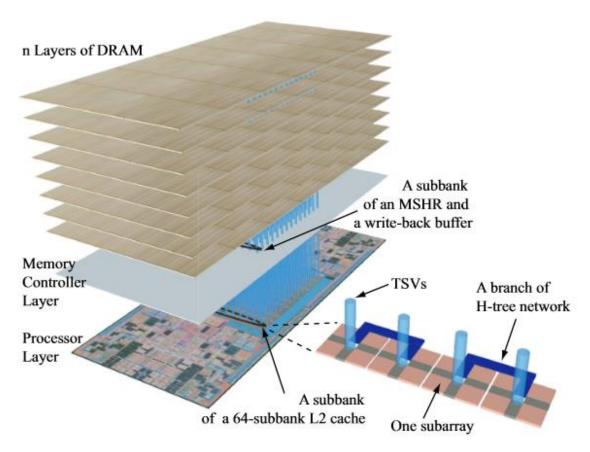

| FIGURE 31.   | SMART-3D DESIGN: 64 BYTES-WIDE BUS WITH TSVS DIRECTLY ON TOP OF EACH L2      |          |

|              | SUB-BANK [WOO10]                                                             |          |

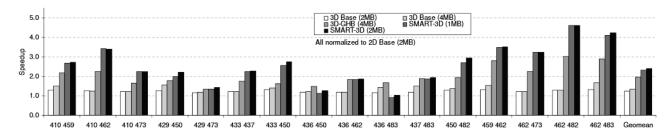

| FIGURE 32.   | 2-CORE SYSTEM PERFORMANCE IMPROVEMENT UNDER DIFFERENT ARCHITECTURES          |          |

|              | [WOO10]                                                                      | 48       |

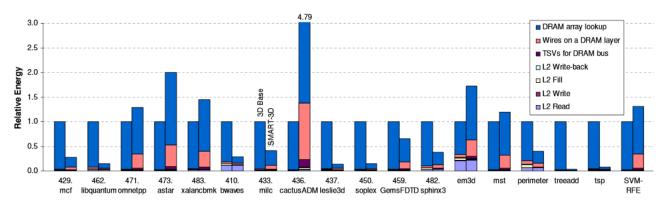

|              | DYNAMIC ENERGY CONSUMPTION OF 3D-BASE AND 3D-SMART [WOO10]                   |          |

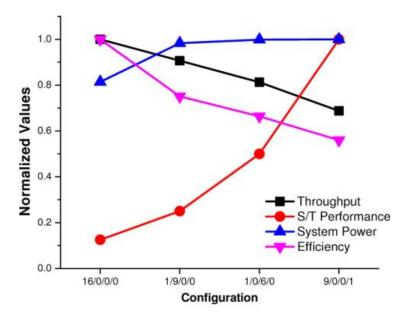

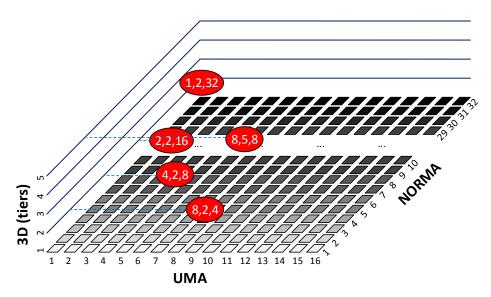

| FIGURE 34.   | RANGE OF SYSTEM CONFIGURATIONS UNDER A 250 MW POWER BUDGET [FIC13]           | 50       |

| FIGURE 35    | . MANYCORE ARCHITECTURE PROPOSED BY GUTHMUTTER, MIRO-PANADES AND             |          |

|              | GREINER [GUT12].                                                             | 51       |

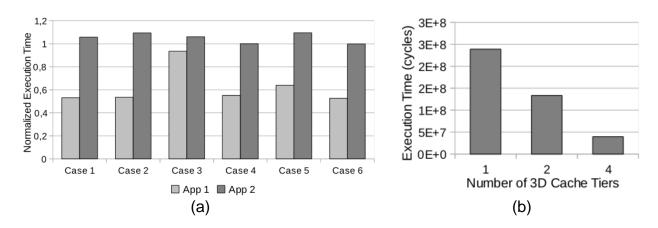

| FIGURE 36.   | (A) NORMALIZED EXECUTION TIME FOR ALL TEST CASES, AND (B) EXECUTION TIME FOR |          |

|              | THE FFT 220 BENCHMARK [GUT12].                                               |          |

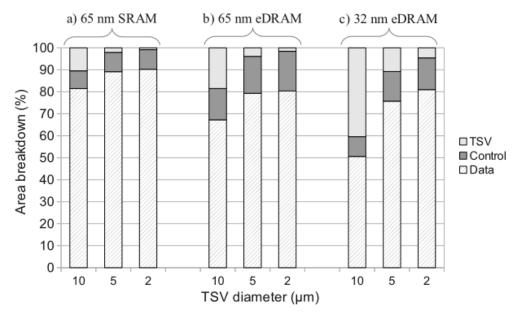

| FIGURE 37.   | AREA BREAKDOWN WITH THREE TSV DIAMETERS [GUT12]                              |          |

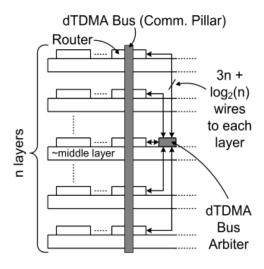

| EIGLIDE 20                                                                                           | TDMA BUS AS THE COMMUNICATION PILLAR [LI06].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                        |

|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

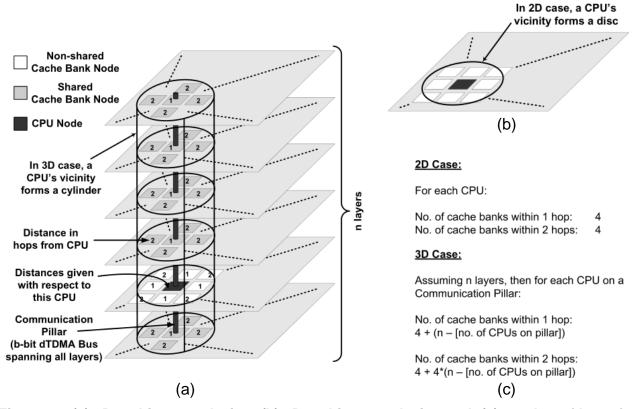

| FIGURE 39                                                                                            | . (a) 3D ARCHITECTURE DESIGN; (B) 2D ARCHITECTURE DESIGN AND; (C) NUMBER OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                        |

|                                                                                                      | HOPS FOR BOTH ARCHITECTURES [LI06].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 53                                                                     |

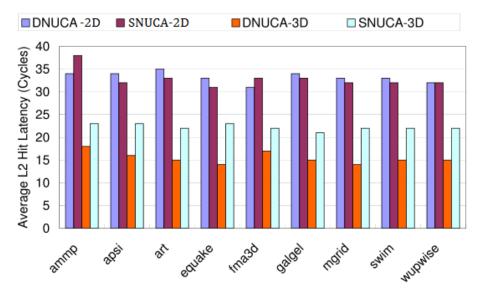

| FIGURE 40                                                                                            | AVERAGE L2 HIT LATENCY UNDER FOUR ARCHITECTURAL SCHEMES (BASED ON [LI06]).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .53                                                                    |

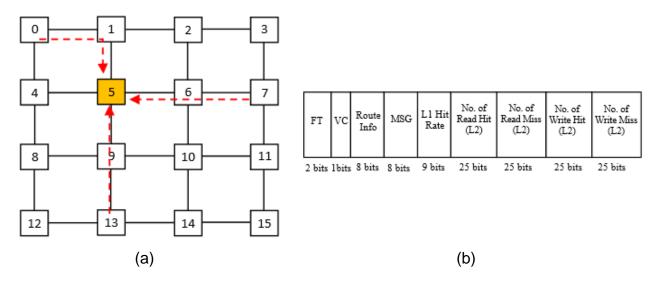

|                                                                                                      | . (A) THREE COMMUNICATIONS TARGETING THE CENTRAL CORE, AND (B) THE CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                        |

|                                                                                                      | FLIT STRUCTURE [NIK15].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                        |

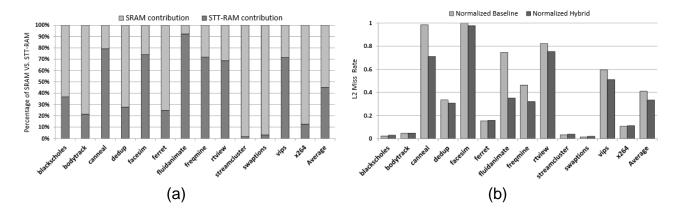

| FIGURE 42                                                                                            | (a) PERCENTAGE OF SRAM VS STT-RAM USE AND (B) L2 MISS RATE [NIK15]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                        |

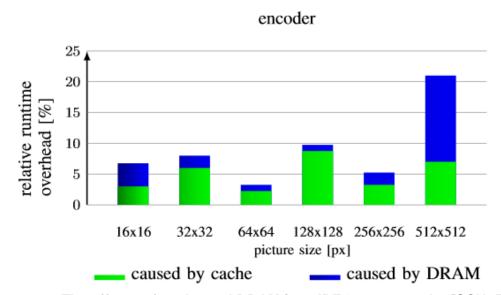

|                                                                                                      | THE EFFECTS OF CACHE AND DRAM IN A JPEG2000 ENCODER [SCH15a]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                        |

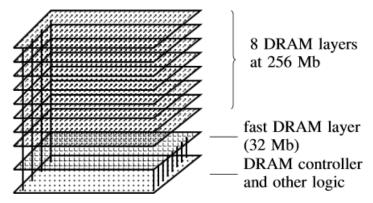

|                                                                                                      | FAST DRAM LAYER AND 8 DRAM LAYERS [SCH15A].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                        |

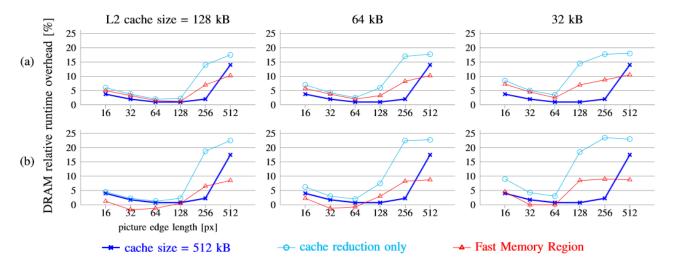

|                                                                                                      | SIMULATION RESULTS OF THE EFFECT OF L2 CACHE SIZE REDUCTION IN COMBINATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                        |

| FIGURE 43                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                        |

| <b>5</b>                                                                                             | WITH FAST DRAM LAYER, (A) ENCODER (B) DECODER [SCH15A]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

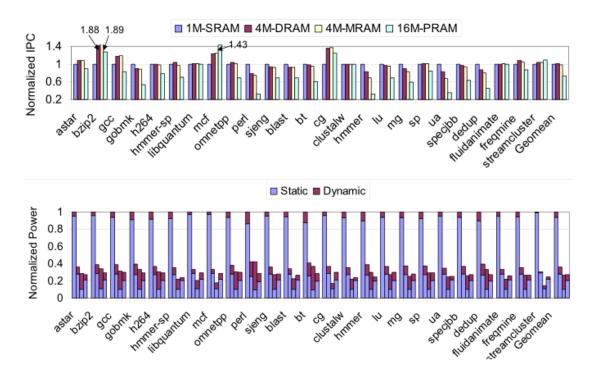

| FIGURE 46                                                                                            | Performance (TOP) and power (BOTTOM) COMPARISON OF THE FOUR L2 MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                        |

| _                                                                                                    | TECHNOLOGIES UNDER THE SAME AREA CONSTRAINT [WU09].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                        |

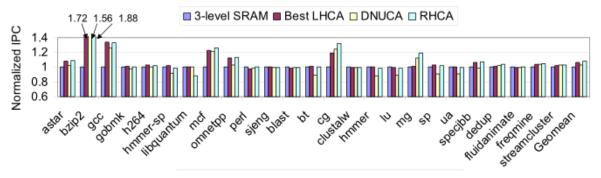

| FIGURE 47                                                                                            | PERFORMANCE OF SRAM-MRAM (HEREIN CALLED RHCA) AGAINST BASELINE SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                        |

|                                                                                                      | CACHE, BEST INTER LEVEL HYBRID CACHE (HEREIN CALLED LHCA), AND DYNAMIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|                                                                                                      | NUCA [WU09]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 57                                                                     |

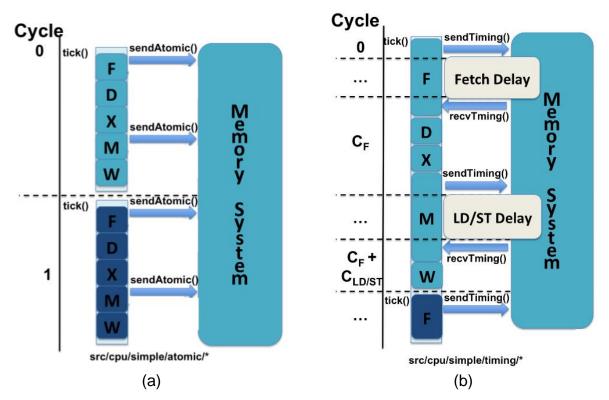

| FIGURE 48                                                                                            | NUCA [WU09]SCHEMATIC OF (A) ATOMICSIMPLE AND (B) TIMINGSIMPLE CPU MODELS [SAI12]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60                                                                     |

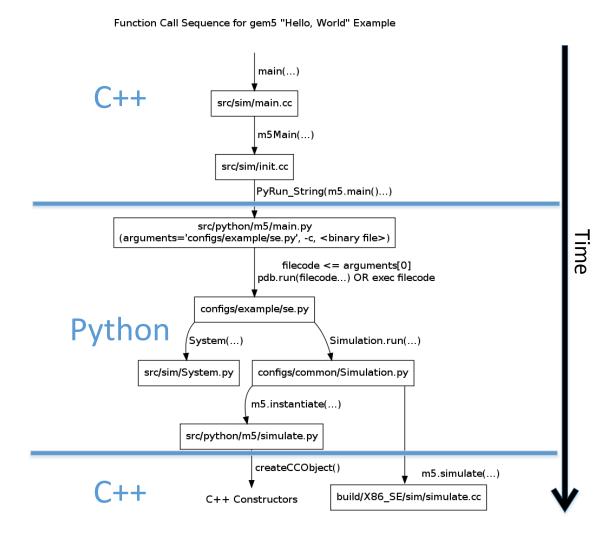

| FIGURE 49                                                                                            | INITIALIZATION OF GEM5 (BASED ON [GEM15E]).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 62                                                                     |

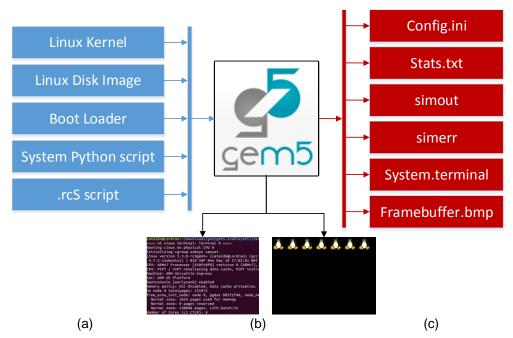

| FIGURE 50                                                                                            | GEM5 SIMULATION (A) INPUTS, (B) RUNTIME INTERFACES AND (C) OUTPUTS (BASED ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | J                                                                      |

|                                                                                                      | [WIE12])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63                                                                     |

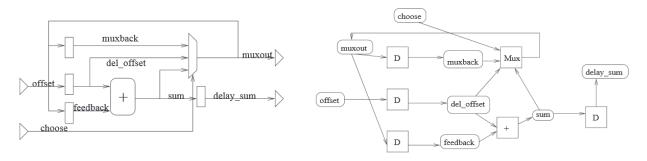

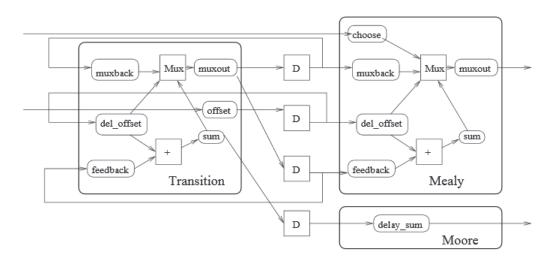

| FIGURE 51                                                                                            | EYAMDLE OF A SIMPLE HARDWARE (LEET) AND ITS REPRESENTATION AS A GRADE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                      |

| I IGUNE 31                                                                                           | EXAMPLE OF A SIMPLE HARDWARE (LEFT) AND ITS REPRESENTATION AS A GRAPH (RIGHT) [FRA04].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | '<br>65                                                                |

| FIGURE 52                                                                                            | . CABA REPRESENTATION OF THE PREVIOUS HARDWARE DESCRIPTION IN FIGURE 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 03                                                                   |

| FIGURE 32                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                        |

| F                                                                                                    | (THIS IS NOT THE FINAL OPTIMIZED VERSION) [FRA04]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                        |

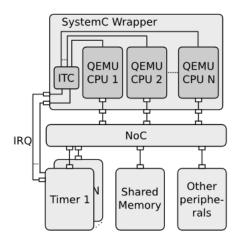

|                                                                                                      | EXAMPLE OF A SIMULATION PLATFORM IN RABBITS [GLI09].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                        |

|                                                                                                      | EXAMPLE OF A DML DEVICE PROGRAMMING INTERFACE [WIN10]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                        |

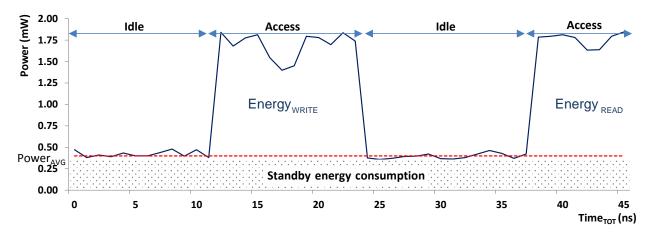

|                                                                                                      | EXEMPLIFICATION OF THE ENERGY CONSUMPTION OF A MEMORY CACHE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                        |

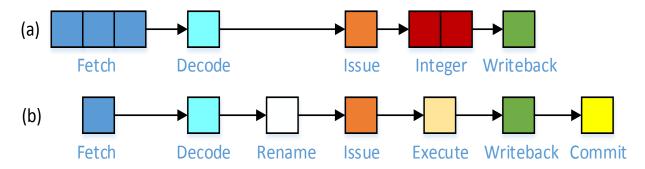

| FIGURE 56                                                                                            | . PIPELINE STAGES OF (A) CORTEX-A7 AND (B) GEM5 O3 CPU MODEL (BASED ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|                                                                                                      | [ARM11B][GEM15F])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 73                                                                     |

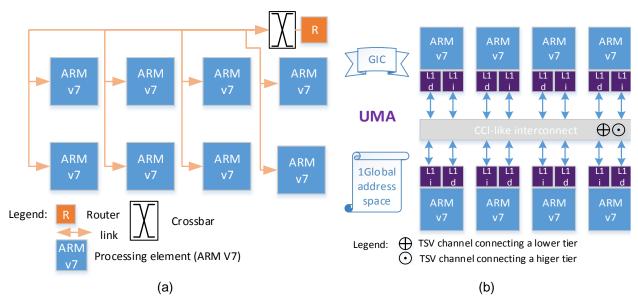

| FIGURE 57                                                                                            | . SCHEMATIC REPRESENTATION OF (A) ON-CHIP COMMUNICATION SYSTEM PERFORMED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | `                                                                      |

|                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                        |

|                                                                                                      | WITH A CROSSBAR CONNECTED TO A NOC THROUGH A ROUTER PORT; (B) THE SAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Ξ                                                                      |

|                                                                                                      | WITH A CROSSBAR CONNECTED TO A NOC THROUGH A ROUTER PORT; (B) THE SAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <u>=</u><br>′                                                          |

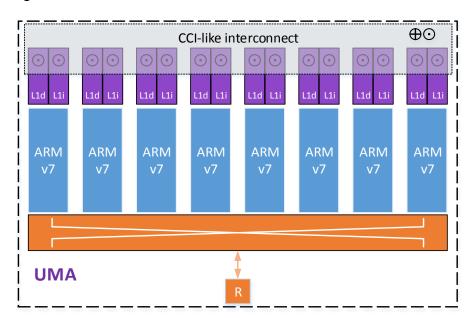

| FIGURE 58                                                                                            | WITH A CROSSBAR CONNECTED TO A NOC THROUGH A ROUTER PORT; (B) THE SAME PROCESSORS WITH L1 CACHES OF DATA AND CODE AND THE GEM5'S CCI MEMORY INTERCONNECTION.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ፤<br>′<br>.74                                                          |

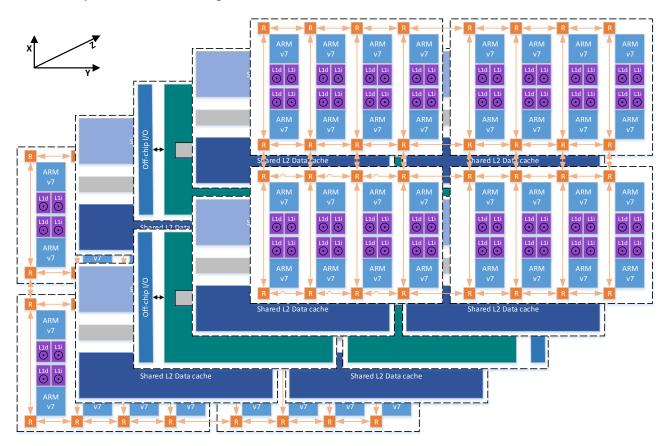

| FIGURE 58                                                                                            | WITH A CROSSBAR CONNECTED TO A NOC THROUGH A ROUTER PORT; (B) THE SAME PROCESSORS WITH L1 CACHES OF DATA AND CODE AND THE GEM5'S CCI MEMORY INTERCONNECTION.  A CLUSTER OF EIGHT PROCESSORS WITH MESSAGE COMMUNICATION AND MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ≣<br>(<br>. <b>74</b><br>(                                             |

|                                                                                                      | WITH A CROSSBAR CONNECTED TO A NOC THROUGH A ROUTER PORT; (B) THE SAME PROCESSORS WITH L1 CACHES OF DATA AND CODE AND THE GEM5'S CCI MEMORY INTERCONNECTION.  A CLUSTER OF EIGHT PROCESSORS WITH MESSAGE COMMUNICATION AND MEMORY ARCHITECTURES.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ≣<br>(<br>.74<br>(<br>.74                                              |

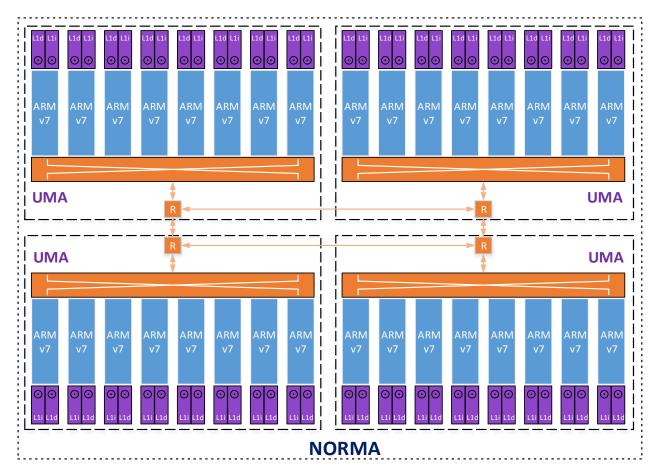

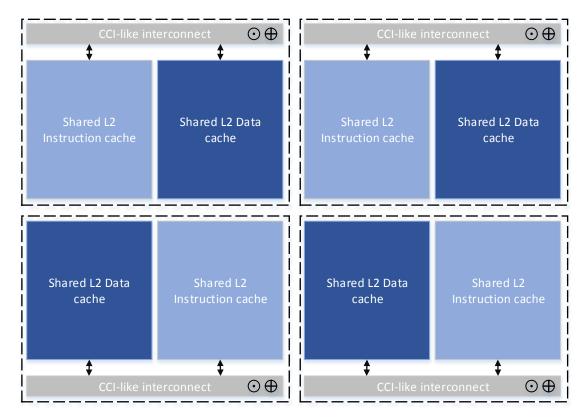

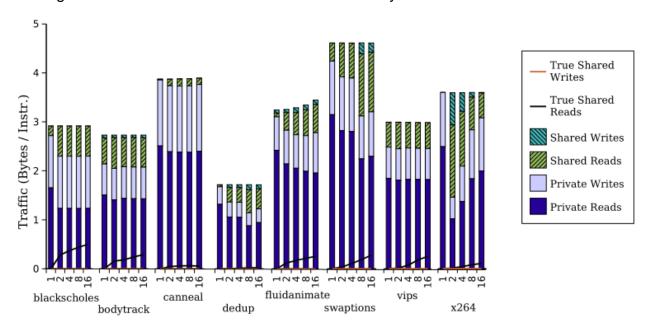

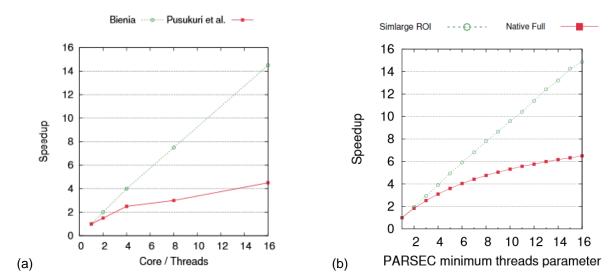

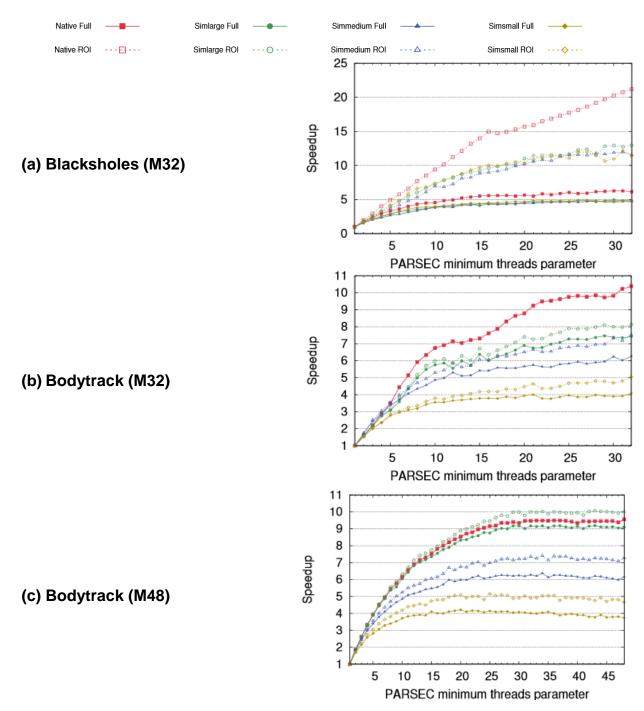

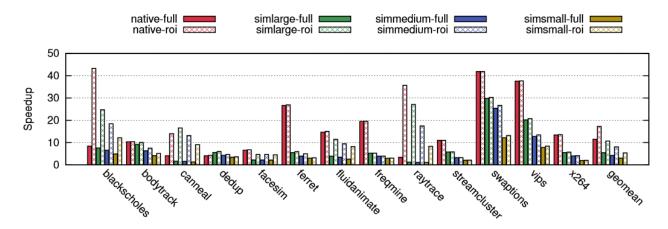

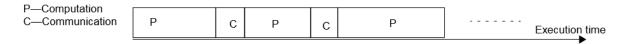

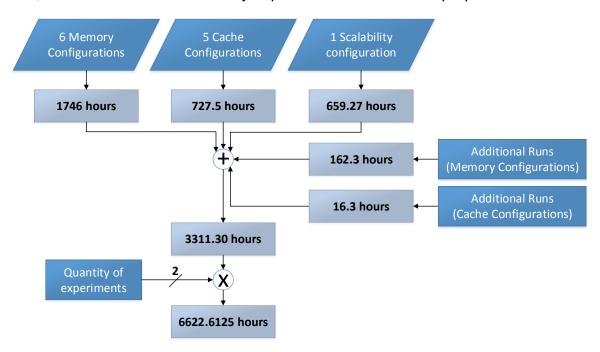

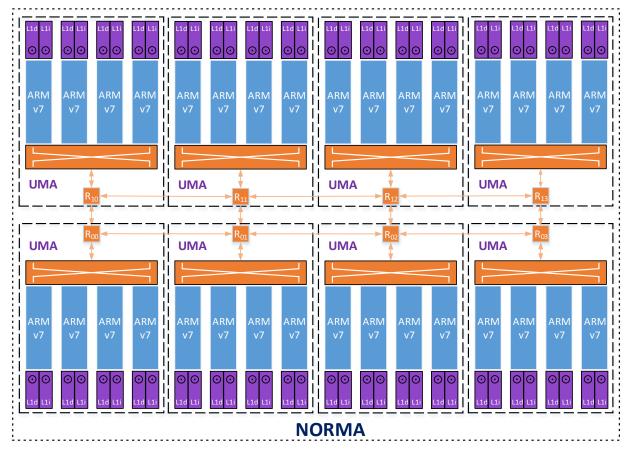

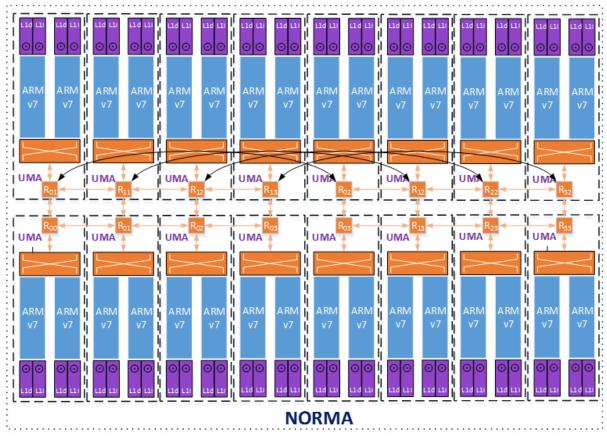

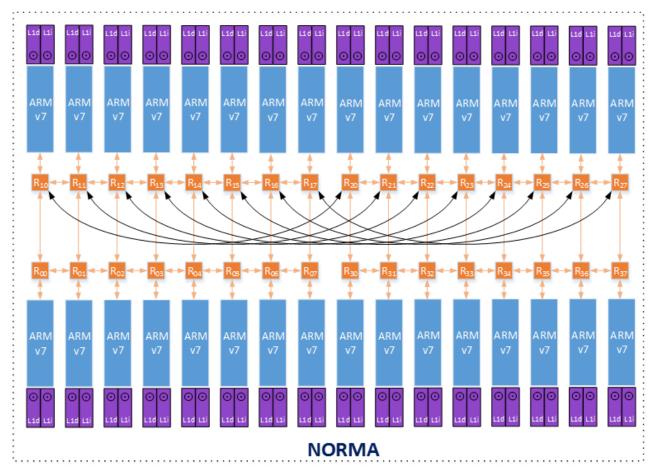

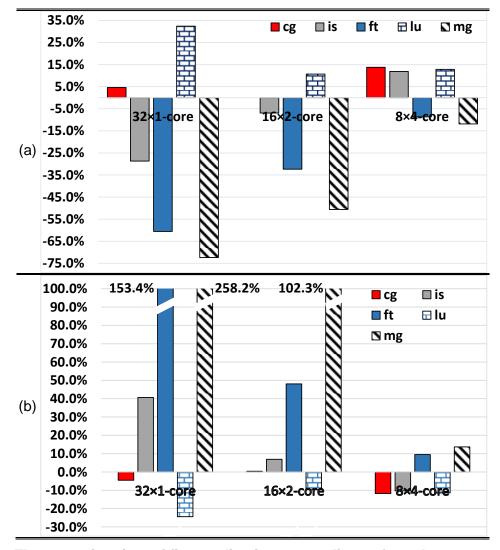

|                                                                                                      | WITH A CROSSBAR CONNECTED TO A NOC THROUGH A ROUTER PORT; (B) THE SAME PROCESSORS WITH L1 CACHES OF DATA AND CODE AND THE GEM5'S CCI MEMORY INTERCONNECTION.  . A CLUSTER OF EIGHT PROCESSORS WITH MESSAGE COMMUNICATION AND MEMORY ARCHITECTURES.  9. FIRST TIER OF THE SYSTEM (MESSAGE COMMUNICATION AND MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | :<br>(<br>. 74<br>(<br>. 74                                            |