## PONTIFÍCIA UNIVERSIDADE CATÓLICA DO RIO GRANDE DO SUL

#### FACULDADE DE INFORMÁTICA

# CONTRIBUTIONS TO THE DESIGN AND PROTOTYPING OF GALS AND ASYNCHRONOUS SYSTEMS

MATHEUS TREVISAN MOREIRA

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Computer Science at the Pontifícia Universidade Católica do Rio Grande do Sul

ADVISOR: PROF. NEY LAERT VILAR CALAZANS

PORTO ALEGRE 2012

M838c Moreira, Matheus Trevisan

Contributions to the design and prototyping of GALS and asynchronous systems / Matheus Trevisan Moreira. – Porto Alegre, 2012.

79 f.

Diss. (Mestrado) – Fac. de Informática, PUCRS. Orientador: Prof. Dr. Ney Laert Vilar Calazans.

1. Informática. 2. Circuitos Assíncronos. 3. Arquitetura de Redes. 4. Roteamento – Redes de Computadores. I. Calazans, Ney Laert Vilar. II. Título.

CDD 004.6

Ficha Catalográfica elaborada pelo Setor de Tratamento da Informação da BC-PUCRS

## Pontifícia Universidade Católica do Rio Grande do Sul FACULDADE DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

# TERMO DE APRESENTAÇÃO DE DISSERTAÇÃO DE MESTRADO

Dissertação intitulada "Contributions to the Design and Prototyping of GALS and Asynchronous Systems", apresentada por Matheus Trevisan Moreira como parte dos requisitos para obtenção do grau de Mestre em Ciência da Computação, Sistemas Embarcados e Sistemas Digitais, aprovada em 13/04/2012 pela Comissão Examinadora:

| Prof. Dr. Ney Laert Vilar Calazans –<br>Orientador                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PPGCC/PUCRS   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| French Shu lles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

| Prof. Dr. Fernando Gehm Moraes –                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PPGCC/PUCRS   |

| Eden Managuria &                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |

| Prof. Dr. Edson Ifarraguirre Moreno -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FACIN/PUCRS   |

| 03 . 06 . 2012                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |

| Homologada em $\Omega^{0}$ / $\Omega^{0}$ | pela Comissão |

| al 4. 1. 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |

Prof. Dr. Paulo Henrique Lemelle Fernandes Coordenador.

**PUCRS**

**Campus Central**

Av. Ipiranga, 6681 - P32- sala 507 - CEP: 90619-900

Fone: (51) 3320-3611 - Fax (51) 3320-3621

E-mail: <a href="mailto:ppgcc@pucrs.br">ppgcc@pucrs.br</a> www.pucrs.br/facin/pos

#### **ACKNOWLEDGMENTS**

To my advisor, who became a friend over these years, Prof. Dr. Ney Calazans, thanks for all his support and guidance in the development of this work. Thanks for the confidence deposited in me and for all the useful discussions we had. Thanks for the opportunities given to me and for always being available when I needed.

Thanks to the members of GAPH and GSE, to my friends and the people who contributed somehow in the development of this work. Thanks to all my friends and colleagues, especially to Felipe de Magalhães, Jerônimo Corrêa and Bruno Oliveira for their friendship and the support in the development of this work.

Thanks also go to Professors Fernando Moraes, Edson Moreno, Alexandre Amory and César Marcon for all the useful and insightful discussions we had. Special thanks to my colleague and friend Julian Pontes for all the discussions about microelectronics and asynchronous circuits and for solving my CAD tools problems.

Finally thanks to my family and to my girlfriend for all the support. Thanks for your love and patience. Without you this work would not have been possible

#### **A**BSTRACT

As CMOS technology nodes scale down, new problems arise concerning the design of synchronous circuits and systems. This is due to tight constraints resulting from the use of a single signal to control a whole complex integrated circuit. Moreover, modern chips integrate whole systems that require a large amount of intellectual property cores, each with specific requirements and design constraints. In this context, asynchronous design techniques present appealing solutions to help designers achieving efficient systems, as each core can be independently implemented and then employ asynchronous communication at the system level. Different works available in literature demonstrate that asynchronous circuits are well suited for low power, high speed and robust applications. However, these circuits are very difficult to be implemented, due to the lack of design automation tools and basic components. In this way, experiments with asynchronous circuits are practically limited to full custom approaches. In order to help overcoming such limitations, the Author has been involved with asynchronous circuits design for five years. This work presents details of part of this research work, including the implementation of five non-synchronous network-on-chip routers, a standard cell library with over five hundred components for asynchronous circuits and a design flow proposed for such components.

#### **RESUMO**

Com o avanço de tecnologias CMOS, novos desafios surgem para o projeto de circuitos e sistemas síncronos. Isso se deve ao fato de que o uso de um único sinal para controlar um circuito integrado complexo resulta em restrições de projeto difíceis de serem atendidas. Além disso, chips atuais integram sistemas inteiros, que necessitam de uma grande quantidade de núcleos de propriedades intelectual, cada um com necessidades e restrições específicas. Neste cenário, técnicas assíncronas de projeto representam soluções interessantes para ajudar projetistas a obter sistemas eficientes, uma vez que cada núcleo de propriedade intelectual pode ser projetado de forma independente e então comunicar-se assincronamente, a nível de sistema. Diversos trabalhos disponíveis na literatura demonstram que circuitos assíncronos são adequados para implementações que necessitem baixo consumo de potência, alto desempenho ou alta robustez. Entretanto, atualmente, é muito difícil de projetar tais circuitos, dada a falta de ferramentas de automação e de bibliotecas de componentes básicos. Dessa forma, o uso de circuitos assíncronos é praticamente limitado a abordagens full-custom. A fim de contribuir para a superação dessa barreira, o Autor está envolvido na pesquisa de circuitos assíncronos há cinco anos. Este trabalho apresenta detalhes de parte dessa pesquisa, incluindo a implementação de cinco roteadores de redes intra-chip não síncronos, uma biblioteca de células com mais de quinhentos componentes assíncronos e um fluxo de projeto proposto para o projeto de tais componentes.

## **LIST OF FIGURES**

| $Figure\ 1-A\ Basic\ 2-input\ C-Element\ truth\ table\ and\ its\ state\ diagram,\ assuming\ a\ symmetric\ behavior\ with\ regard\ to\ property and\ to\ property.$ | ALL     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| INPUTS                                                                                                                                                             | 24      |

| FIGURE 2 – STANDARD CELL PROPOSED DESIGN FLOW. THE THREE MAIN STEPS ARE: (A) SPECIFICATION, (B) DESIGN AND (C) VALIDATIO                                           | N.      |

| ACTIONS ARE REPRESENTED BY BOXES, DECISIONS BY DIAMONDS, DESCRIPTIONS AS ROUNDED CORNER BOXES AND THE REPOSITO                                                     | RY AS A |

| CYLINDER                                                                                                                                                           | 28      |

| FIGURE 3 — EXAMPLES OF SCHEMATIC FOR THE C2 CELL, A 2-INPUT C-ELEMENT.                                                                                             | 29      |

| FIGURE 4 – EXAMPLE OF THE GATE LEVEL VIEW OF A SIMULATION CIRCUIT GENERATED BY ROGEN.                                                                              | 29      |

| FIGURE 5 — EXAMPLE OF CES OUTPUT FOR A C-ELEMENT.                                                                                                                  | 32      |

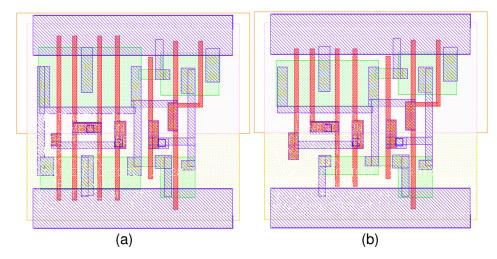

| FIGURE 6 – PHYSICAL LAYOUTS FOR (A) ONE BS AND (B) ONE BP IMPLEMENTATION OF THE 2-INPUT C-ELEMENT.                                                                 | 33      |

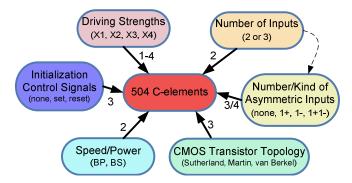

| FIGURE 7 – ASCEND-ST65 C-ELEMENTS COMPOSITION. ROUNDED CORNER RECTANGLES REPRESENT ONE PARAMETER CHOICE. EDGES                                                     | ARE     |

| LABELED WITH THE NUMBER OF CHOICES THE PARAMETER IMPLIES. THE DOTTED EDGE REPRESENTS DEPENDENCIES BETWEEN ASS                                                      | OCIATED |

| PARAMETER CHOICES                                                                                                                                                  | 35      |

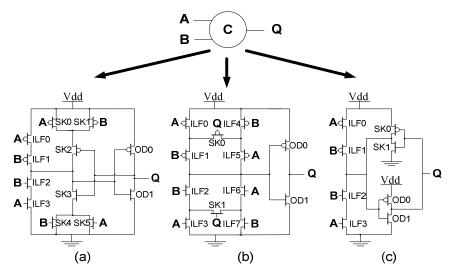

| FIGURE 8 – ALTERNATIVE CMOS TOPOLOGY IMPLEMENTATIONS OF THE C-ELEMENT: (a) SUTHERLAND'S PULL-UP PULL-DOWN, (B) VAI                                                 | N       |

| Berkel's and (c) Martin's weak feedback.                                                                                                                           | 36      |

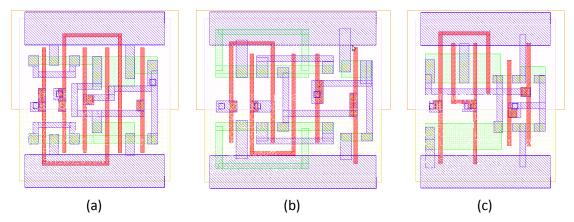

| FIGURE 9 — EXAMPLE PHYSICAL LAYOUT AT THE CELL LEVEL OF THE DESIGNED C-ELEMENTS: (A) SUTHERLAND'S PULL-UP PULL-DOWN, (I                                            |         |

| Berkel's, (c) Martin's weak feedback.                                                                                                                              | 37      |

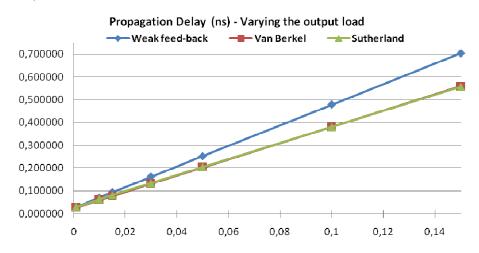

| FIGURE 10 – PROPAGATION DELAY OF THE DESIGNED STANDARD CELLS AFTER ELECTRICAL EXTRACTION AS A FUNCTION OF THE OUTPUT I                                             | OAD     |

| CAPACITANCE. RESULTS WERE OBTAINED BY FIXING THE INPUT SLOPE IN 1.2 PS AND VARYING THE OUTPUT LOAD FROM 0.001PF                                                    | то      |

| 0.15PF                                                                                                                                                             | 38      |

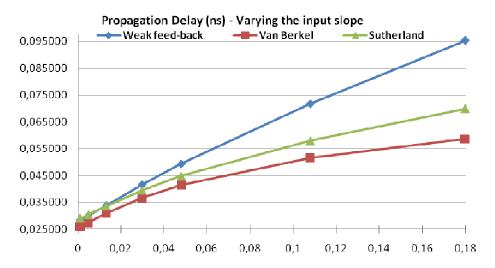

| FIGURE 11—PROPAGATION DELAY OF THE DESIGNED STANDARD CELLS AFTER ELECTRICAL EXTRACTION AS A FUNCTION OF THE INPUT SLC                                              | PE.     |

| RESULTS WERE OBTAINED BY ESTABLISHING THE OUTPUT LOAD IN 1FF AND VARYING THE INPUT SLOPE LOAD FROM 0.0012NS TO                                                     | )       |

| 0.180ns                                                                                                                                                            | 39      |

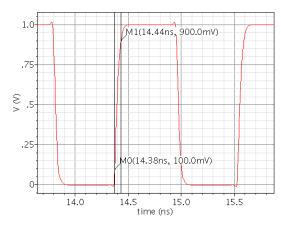

| FIGURE 12 – INPUT SLOPE OF A SINGLE CELL OF AN OSCILLATOR RING COMPOSED BY SUTHERLAND C-ELEMENTS                                                                   | 40      |

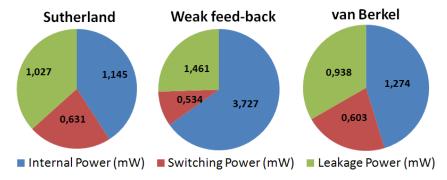

| FIGURE 13 – C-ELEMENTS POWER CONSUMPTION FOR EACH ASYNCHRONOUS RSA CRYPTOGRAPHIC CORE IMPLEMENTATION                                                               | 43      |

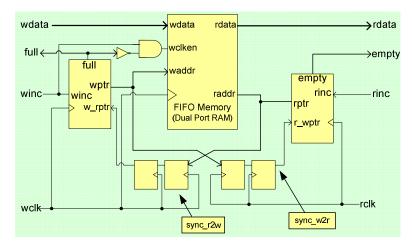

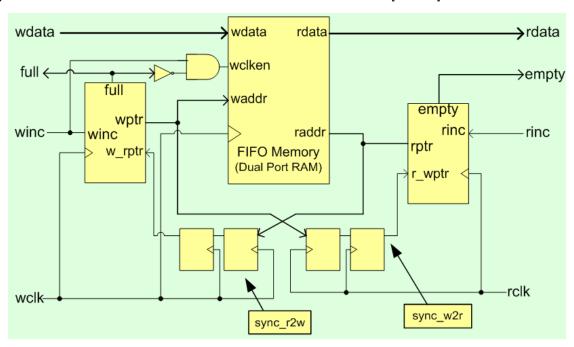

| FIGURE 14 – STRUCTURE OF A BY-SYNCHRONOUS FIFO.                                                                                                                    | 47      |

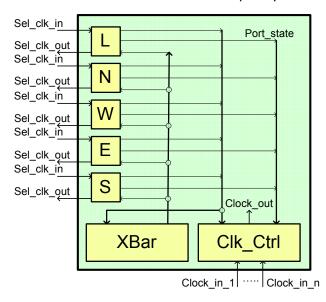

| FIGURE 15 – STRUCTURE OF THE HERMES-GLP ROUTER, HIGHLIGHTING THE CLOCK CONTROL MODULE STRUCTURES.                                                                  | 48      |

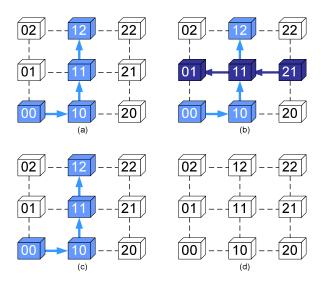

| FIGURE 16 – EXAMPLE OF DYNAMIC CLOCK DETERMINATION AND CLOCK GATING. THE DARKER THE ROUTER, THE HIGHER IS ITS OPERATI                                              | NG      |

| FREQUENCY. WHITE ROUTERS ARE UNDER CLOCK GATING                                                                                                                    | 49      |

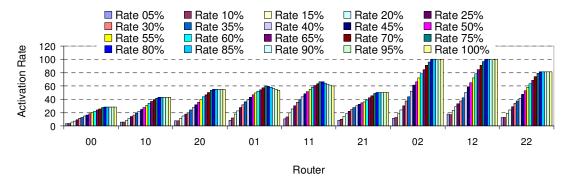

| FIGURE 17 – AVERAGE ACTIVATION RATE OF EACH ROUTER FOR FLOW (A) OF TABLE XIII, WITH INSERTION RATES VARYING BETWEEN 5                                              | % and   |

| 100%                                                                                                                                                               | 50      |

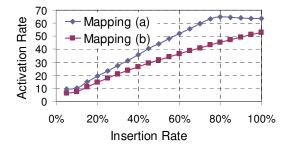

| FIGURE 18 – ACTIVATION RATE VARIATION OF HERMES-GLP NOC AS A FUNCTION OF MAPPING AND TRAFFIC INSERTION RATE                                                        | 50      |

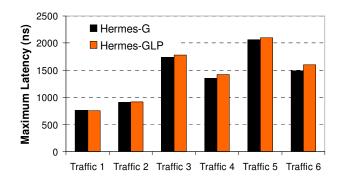

| FIGURE 19 – COMPARING PACKET MAXIMUM LATENCY FOR HERMES-G AND HERMES-GLP NOCS.                                                                                     | 51      |

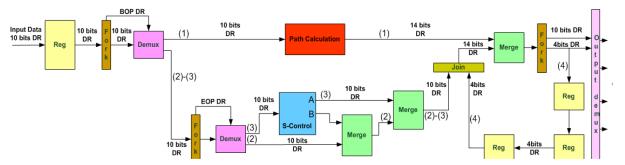

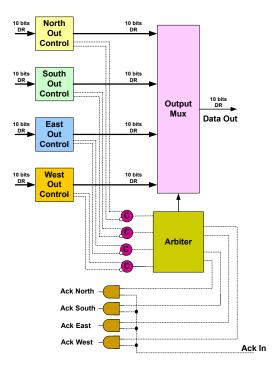

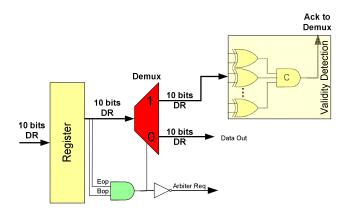

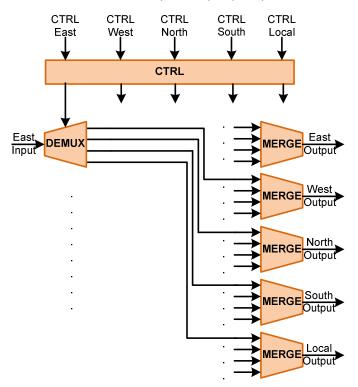

| FIGURE 20 – HERMES-A ROUTER INPUT PORT ARCHITECTURE. ALL PATHS EMPLOY DUAL-RAIL ENCODING.                                                                          | 54      |

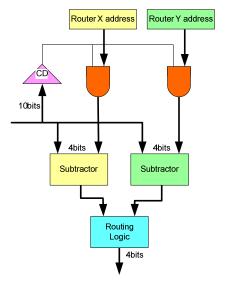

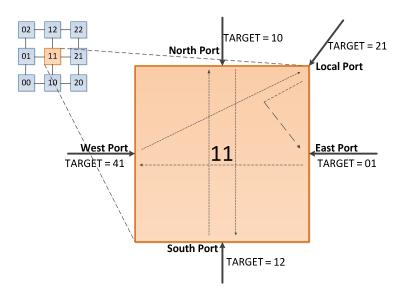

| FIGURE 21 — HERMES-A PATH CALCULATION CIRCUIT.                                                                                                                     | 55      |

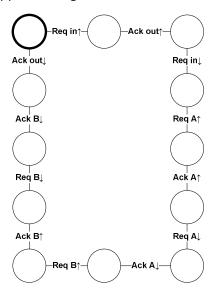

| FIGURE 22 – STATE MACHINE FOR THE S-CONTROL MODULE.                                                                                                                | 55      |

| FIGURE 23 – LOCAL OUTPUT PORT STRUCTURE. DASHED LINES REPRESENT ACTUAL WIRES. SOLID LINES REPRESENT DUAL-RAIL ENCODED                                              |         |

|                                                                                                                                                                    | 56      |

| FIGURE 24 – OUTPUT CONTROL STRUCTURE. ALL PATHS EMPLOY DUAL-RAIL ENCODING.                                                                                         | 57      |

| FIGURE 25 – SCAFFI NETWORK INTERFACE BETWEEN A HERMES-A ROUTER AND A SYNCHRONOUS PE. THE INTERFACE EMPLOYS CLOCK                                                   |         |

| STRETCHING TECHNIQUES TO AVOID METASTABILITY. THE STRETCHER CIRCUITS ARE NOT REPRESENTED IN THE PICTURE                                                            | 57      |

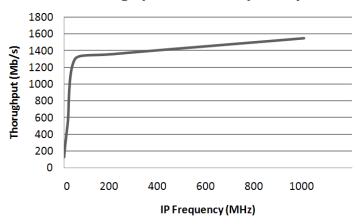

| FIGURE 26 – EIGHT BIT ROUTER THROUGHPUT VERSUS IP FREQUENCY.                                                                                                       | 59      |

| FIGURE 27 – SCENARIO FOR EVALUATING THE HERMES-AA ROUTER THROUGHPUT VARIATION WITH THE IP FREQUENCY                                                                | 60      |

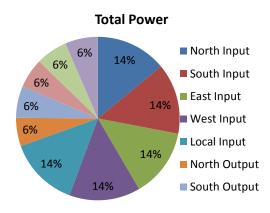

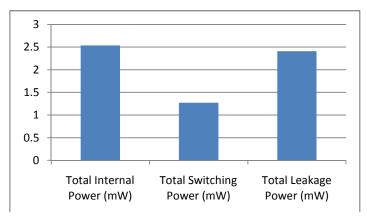

| FIGURE 28 – EIGHT BIT ROUTER MODULES PROPORTIONAL POWER.                                                                                                           | 60      |

| Figure 29 – Router Power Characterization.                                                                                                                         | 61      |

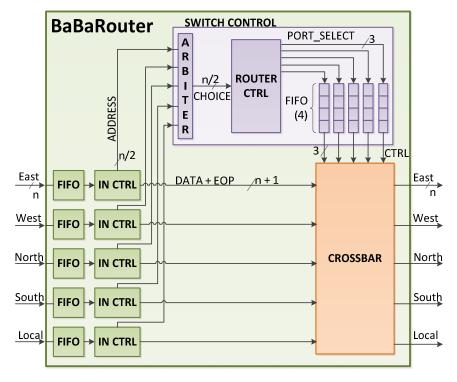

| FIGURE 30 – BABAROUTER IMPLEMENTATION BLOCK DIAGRAM. COMMUNICATION AND SYNCHRONIZATION TAKES PLACE THROUGH                                                         |         |

| HANDSHAKE CHANNELS. CONTROL SIGNALS ARE IMPLICIT IN THE DRAWING. FLIT SIZE IS DENOTED BY N, WHICH IS USED TO SPECIF                                                | Y THE   |

| ADOPTED INTERNAL CHANNEL WIDTHS.                                                                                                                                   | 62      |

| Figure 31 – BaBaRouter Crossbar block diagram.                                                                | 64     |

|---------------------------------------------------------------------------------------------------------------|--------|

| FIGURE 32 – BABAROUTER DATAFLOW FOR FIRST FLITS.                                                              | 65     |

| FIGURE 33 – BABAROUTER DATAFLOW FOR SECOND AND FOLLOWING FLITS.                                               | 65     |

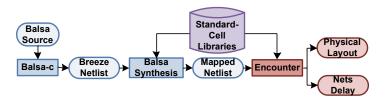

| FIGURE 34 – BABAROUTER DESIGN FLOW.                                                                           | 65     |

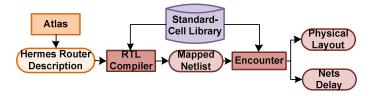

| Figure 35 — Hermes Router design flow                                                                         | 66     |

| FIGURE 36 – SCENARIO TO VALIDATE FUNCTIONALITY OF THE ROUTERS.                                                | 68     |

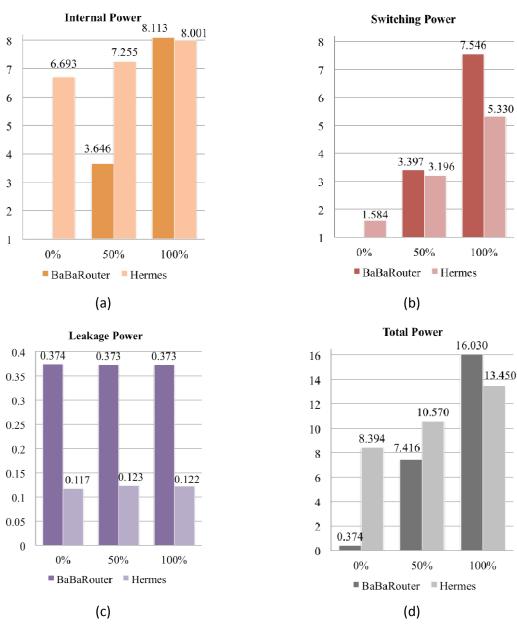

| Figure 37 –Power results (in mW) comparison between BaBaRouter and Hermes: (a) internal power , (b) switching | POWER, |

| (c) leakage power and (d) total power. Three scenarios were evaluated, routers always idle (0%), routers      |        |

| TRANSMITTING DATA 50% OF THE TIME (50%) AND ROUTERS ALWAYS TRANSMITTING DATA (100%)                           | 69     |

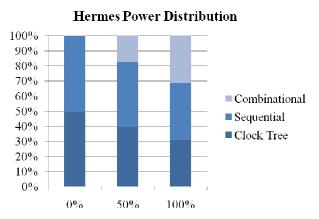

| Figure 38 – Power distribution in BaBaRouter.                                                                 | 70     |

| Figure 39 – Power distribution in the Hermes router                                                           | 71     |

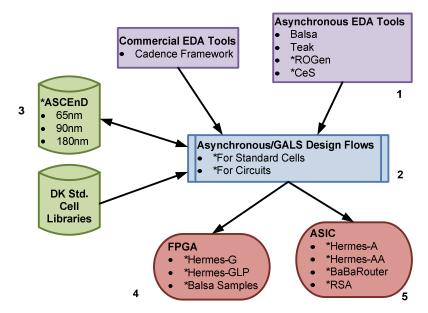

| FIGURE 40 – DIAGRAM EXPRESSING THE CONTRIBUTIONS OF THE AUTHOR'S WORK ON THE DESIGN AND DESIGN AUTOMATION OF  |        |

| ASYNCHRONOUS CIRCUITS AND GALS SYSTEMS. A "*" INDICATES AUTHOR'S CONTRIBUTIONS.                               | 73     |

|                                                                                                               |        |

## LIST OF TABLES

| <code>FABLEI-Proposed</code> cell set logic functions [MOR11a]. $	ilde{Q}$ is the cell single output. RST is a reset signal. Note the last ce | .LL    |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------|

| DISPLAYS AN ASYMMETRIC BEHAVIOR.                                                                                                              | 28     |

| TABLE II – A COMPARISON OF ASYNCHRONOUS AND SYNCHRONOUS IMPLEMENTATIONS OF AN RSA CRYPTOGRAPHIC CORE                                          | 31     |

| ABLE III – A comparison of power consumption for asynchronous and synchronous implementations of the RSA                                      |        |

| CRYPTOGRAPHIC CORE                                                                                                                            | 31     |

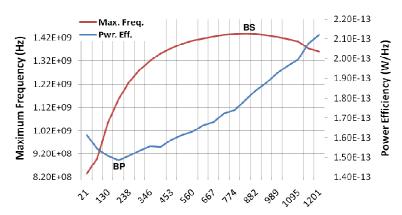

| TABLE IV — Transistors gate widths and performance figures for the circuits simulated with BS and BP C-Elements                               | 33     |

| TABLE V – Standard cell area and wire length for the asynchronous implementations of the RSA in STMicroelectronic                             | :S     |

| 65nm technology employing BS and BP versions of C-Elements.                                                                                   | 34     |

| TABLE VI — Power consumption for the asynchronous implementations of the RSA in STMicroelectronics 65nm techno                                |        |

| EMPLOYING BS AND BP VERSIONS OF THE C-ELEMENT.                                                                                                | 35     |

| TABLE VII – Area and parasitic capacitance required by CMOS implementations of the C-Elements after RC extraction                             | 37     |

| ABLE VIII – Capacitance of the input pins and power consumption of the designed standard cells, after electrical                              |        |

| EXTRACTION                                                                                                                                    | 38     |

| ABLE IX – Performance figures of the oscillator rings.                                                                                        | 40     |

| TABLE X – Area and wire results for the three asynchronous RSA cryptographic core implementations after place and i                           | ROUTE  |

|                                                                                                                                               | 41     |

| TABLE XI – POWER CONSUMPTION OF THE THREE ASYNCHRONOUS RSA CRYPTOGRAPHIC CORE IMPLEMENTATIONS                                                 | 42     |

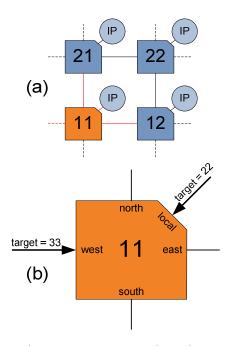

| ABLE XII – NoC-SoC classification as a function of router type and asynchronous interface positions. R=Router, IP=IP                          | )      |

| CORE                                                                                                                                          | 45     |

| ABLE XIII – Simulated producer consumer pairs                                                                                                 | 49     |

| TABLE XIV – A COMPARISON OF FULLY ASYNCHRONOUS INTERCONNECTION NETWORKS AND/OR ROUTERS FOR GALS SOCS. LEGEND A2                               | 2S,    |

| S2A – ASYNC. TO SYNC. / SYNC. TO ASYNC., As. – ASYNCHRONOUS, BE – BEST EFFORT SERVICE, DI – DELAY INSENSITIVE, GS –                           |        |

| GUARANTEED SERVICE, IRREG/REG – IRREGULAR/REGULAR, N.A. – INFORMATION NOT AVAILABLE, OCP – OPEN CORE PROTOCC                                  | oL, VC |

| - VIRTUAL CHANNEL                                                                                                                             | 52     |

| ABLE XV – ASIC IMPLEMENTATION RESULTS FOR AN 180NM XFAB TECHNOLOGY                                                                            | 58     |

| ABLE XVI – West first and XY Hermes-AA routers comparison.                                                                                    | 59     |

| ABLE XVII – West first and XY throughput comparison.                                                                                          | 60     |

| ABLE XVIII – Comparison of BaBaRouter and Hermes Router physical implementations.                                                             | 67     |

## **C**ONTENTS

| 1 INTRODUCTION                         | 19 |

|----------------------------------------|----|

| 1.1 CONTRIBUTIONS FOR ASYNCHRONOUS EDA | 20 |

| 1.2 Non-synchronous NoC Routers        | 21 |

| 1.3 OBJECTIVES                         |    |

| 2 CONCEPTS                             | 23 |

| 2.1 Asynchronous Circuits              | 23 |

| 2.1.1 The Muller C-Element             | 23 |

| 2.1.2 Metastability                    |    |

| 2.2 ASYNCHRONOUS EDA                   | 24 |

| 3 ASYNCHRONOUS EDA CONTRIBUTIONS       | 26 |

| 3.1 C-ELEMENT DESIGN FLOW              | 26 |

| 3.2 ASCEND                             | 35 |

| 4 NON-SYNCHRONOUS NOC ROUTERS          | 44 |

| 4.1 HERMES-G AND HERMES-GLP            | 45 |

| 4.2 HERMES-A AND HERMES-AA             | 51 |

| 4.2.1 Hermes-A                         | 53 |

| 4.2.2 Hermes-AA                        | 58 |

| 4.3 BABANOC                            |    |

| 5 CONTRIBUTIONS AND CONCLUSIONS        | 73 |

| REFERENCES                             | 75 |

## 1 INTRODUCTION

Synchronous digital circuits assume not only the use of discrete voltage levels that translate into Boolean values, but also a discrete notion of time. The latter is generally implemented with all components sharing a common control signal distributed throughout the circuit, the so-called *clock* signal. In this way, the complexity of designing circuits is considerably reduced, as the notion of event sequencing is commanded by pulses of the clock signal everywhere. However, as semiconductor technology nodes evolve, new challenges emerge concerning the design of synchronous circuits, specifically due to this signal's global nature.

Transistors are getting smaller and electrical characteristics such as static power consumption are no longer irrelevant in the design of a synchronous digital circuit. In this way, tighter design constraints are imposed on clocks and other global signals, increasing design complexity [EKE10]. Moreover, guaranteeing that the clock signal presents exactly the same phase and skew in all registers of a modern complex integrated circuit (IC) can be very difficult. Even when a synchronous design is fully verified, variations in the fabrication process of a single transistor may jeopardize the whole circuit behavior, due to strict timing constraints imposed by the synchronous paradigm. Timing closure of complex designs and design robustness have become major concerns in the last years [ZHA07].

Albeit techniques to cope with the difficulties of designing a synchronous circuit exist, they can end up being very expensive. For instance, the clock tree, employed to guarantee same phase and skew in the clock signal of all registers of a circuit is typically responsible for 30% and up to 50% of the total power consumed by a synchronous circuit. For this and other reasons, using non-synchronous design techniques for the design of future ICs is considered inevitable [ITR08].

Asynchronous circuits [SPA01] assume the use of discrete voltage levels that translate into Boolean values, just as synchronous circuits do, but the latter consider time as a continuous quantity. Synchronization, communication and sequencing of events among components are done through local handshaking. The result in "synchronous terms" is that registers are only activated when and where it is necessary. Such characteristic provides advantages when employing the asynchronous paradigm and according to [BER99] [SPA01] [MYE01] [BOU07] and [CRI10] for example, asynchronous circuits may present:

- Lower dynamic power consumption: when not computing, the circuit is quiescent, i.e. consumes only leakage current. When requested, the circuit starts to compute and consumes dynamic power. However, after the computation of a task, the circuit returns to a quiescent point until the next request arrives.

- Higher operating speed: the operating speed is given by local latencies rather than by a global signal. Asynchronous circuits may thus operate with average case delays, while their synchronous counterparts are designed based on worst case delays.

- Better composability and modularity: since synchronization is given by local handshakes rather than a global signal.

- Lower electromagnetic emissions: because registers do not switch all or most at the same time. Instead, they switch at random moments, based on local requests.

- Higher robustness: asynchronous circuits may continue to operate correctly over a large range of variations in power supply and over several technologies. Moreover, since no assumptions are made about the inter-cell communication delays, such circuits are more tolerant to process, voltage and temperature variations.

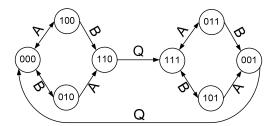

Complex systems-on-chip (SoCs) are composed today by a large amount of intellectual property (IP) cores, each of each using particular standards and/or protocols and presenting varying design constraints. Often, the requirements for each IP core determine the use of specific communication protocols and/or operating frequencies. These requirements make the design of SoCs easier if implemented with multiple frequency domains that communicate and synchronize using asynchronous techniques. SoCs designed through this approach are classified as globally asynchronous locally synchronous (GALS) [CHA84] and may help overcoming the limitations of synchronous design, while at the same time maintaining a mostly synchronous design flow. Conversely, the lack of adequate electronic design automation (EDA) tools imposes a great barrier in the design of asynchronous circuits/interfaces. This is because the majority of commercial applications target the synchronous paradigm. According to the ITRS 2009 Edition [ITR09] further progress in the asynchronous paradigm depends on commercial tool support. The high complexity of modern ICs makes the task of ensuring that such designs will operate correctly on silicon nearly impossible without the use of adequate EDA software and consolidated design methodologies [RAB03]. Additionally, most standard cell libraries provided by vendors still contain only basic devices for synchronous design, such as logic gates and flip-flops, and efficient asynchronous designs require other specific devices as well. In this way, asynchronous design is still used only in restricted applications domains.

The present work describes a set of contributions brought by the Author in previous years (since 2008) to advance the solution of some of the problems that restrain an ampler utilization of GALS and asynchronous systems and circuits in practice. In this period of time, several works were conducted by the Author to help in the development of design automation and facilitation of the design for asynchronous circuits and GALS systems.

## 1.1 Contributions for Asynchronous EDA

The Asynchronous Standard Cells Enabling n Designs (ASCEnD) Library [MOR10] and [ASC12], is a standard cell library designed to support the implementation of asynchronous circuits. It was initially designed for the XFab 180 nm CMOS technology as a simple set of basic asynchronous components drawn at the standard cell layout level. Its most recent version contains over five hundred standard cells and addresses the STMicroelectronics 65nm CMOS technology. Moreover, current work works on an extension of the library to other technologies. ASCEnD was built as part of the Author's End of Term work and has been since employed in the design of three NoC routers and other circuits. By design, ASCEnD is compatible with the basic standard cell libraries of the

underlying technology and has been extensively validated through simulation at several abstraction levels, including post-layout extraction at the physical level.

All components of ASCEnD result from a design flow proposed by the author in [MOR11a]. The flow counts with automated tools and the only manual process is the layout generation. An extension of this work modifies the flow to provide the designer with a choice between low power and high performance designs [MOR11b]. Currently, this flow is parameterizable and compatible with most CMOS technologies.

In [MOR11a], the Author also proposes the integration of ASCEnD with the Manchester Teak asynchronous synthesis tool [BAR09], based on the Balsa language [BAR98] [EDW06] and [SPA01]. Both, Balsa and Teak are developed and maintained by the Advanced Processor Technology Group [APT12] of the University of Manchester. Currently, ASCEnD is also compatible with the Balsa synthesis environment itself. Results show that lower area, higher performance and lower power consumption can be obtained with low design effort, since Balsa is a language specifically designed for implementing asynchronous circuits.

Another previous research work compares asynchronous components and their effect in the circuit after finishing the back end design. The article [MOR12a] describes part of this research. The paper demonstrates some weaknesses of the Teak synthesis tool, and points to possible directions for improvement of the tool. Current work comprises optimizing Teak and Balsa synthesis flows. To do so, a study is under way to scrutinize how asynchronous synthesis tools map the circuit to locate specific weaknesses and search for better solutions.

## 1.2 Non-synchronous NoC Routers

The Author took part in the design of five non-synchronous NoCs. Hermes-G and [PON08] is a NoC and associated router, planned to allow the implementation of GALS systems, by serving as a GALS system communication infrastructure. Its low power version is Hermes-GLP, presented in the same work. The router was developed to reduce power consumption and is based on a simple dynamic frequency scaling (DFS) mechanism that allows significant power dissipation reduction with small latency penalty. Instances of the Hermes-GLP NoC were prototyped and validated in field programmable gate arrays (FPGAs) as described in [HEC12]. There is currently an effort by others to design the Hermes-GLP modules in a 65nm CMOS technology and validate it through ASIC prototyping.

Hermes-A [PON10a] is a NoC router that employs a distributed routing scheme, where the router itself decides which path incoming packets will follow. The router was initially designed in the XFab 180nm CMOS technology and mapped to the foundry-provided standard cell library, and the initial version of ASCEnD. Later, it was implemented in the STMicroelectronics 65nm CMOS technology [PON10b], when the newest version of ASCEnD was released. Hermes-A was designed through a semi-custom approach, where handshake components are generated as schematics of standard-cells, described in VHDL and interconnected in the same way at the top level circuit. The router was synthesized using typical commercial EDA tools, designed for synchronous circuits,

where adaptations were necessary in the design flow, to generate a functional circuit. The netlist was placed and routed and validated through simulation after circuit extraction at physical layout level.

Hermes-AA [PON10b] is an extension of Hermes-A, where packets are routed through an adaptive routing algorithm. The router was implemented in STMicroelectronics 65nm CMOS technology with the same approach used in the design of Hermes-A.

However, the design of NoCs Hermes-A and Hermes-AA demonstrated to be very laborious handcraft, due to the required steps inferred by the use of synchronous EDA tools when designing asynchronous circuits. Therefore, once ASCEnD was integrated with the Balsa synthesis processes, an asynchronous NoC router was described in Balsa language, reducing design complexity. The router was called Balsa-Based Router (or BaBaRouter) [MOR12b]. The router is based on the original Hermes NoC router [MOR04] a very simple router that uses handshake communication. BaBaRouter has exactly the same functionalities and structure as the Hermes handshake router. It was implemented in the STMicroelectronics 65nm CMOS technology and mapped to the cells of ASCEnD and of the foundry-provided standard cell library. The BaBaRouter was validated through simulation after extraction at physical layout level. The obtained results are quite promising. The router proves to be faster and is less power- and area-consuming than Hermes-A and Hermes-AA. Moreover, the design effort is drastically reduced when using Balsa.

### 1.3 Objectives

The objective of this work is to present a set of contributions aimed mostly at the development of automation methods for the design of asynchronous circuits and GALS systems. These contributions encompass the development of a parameterizable and automated design flow for typical asynchronous standard cells, as well as a standard cell library containing over five hundred components dedicated to asynchronous design. This library was integrated with automated tools for implementing asynchronous circuits and validated at the physical layout abstraction level. Furthermore, three asynchronous and two GALS network on chip (NoC) routers were designed and validated. Some of these targeted FPGA implementations and other ASIC versions up to the layout level. The conducted works indicate that the development of EDA tools for supporting the asynchronous paradigm can help overcoming difficulties imposed by current and future silicon technologies. This last observation points to a future PhD theme the Author intends to follow starting in 2012. The results obtained through the development of these activities were already published in seven international conference articles.

## 2 CONCEPTS

This Chapter presents basic concepts of asynchronous circuits and addresses the Balsa and Teak systems, which comprise a language and a framework for describing and implementing such circuits in ASIC and FPGA technologies, as well as two asynchronous circuit synthesis methods.

#### 2.1 Asynchronous Circuits

A digital circuit is (fully) asynchronous when no clock signal is used to control any sequencing of events. Instead, modules use local handshaking among them to synchronize, communicate and operate [SPA01] [MYE01]. In "synchronous terms", the resulting behavior is registers being enabled to store new values only when and where this is needed [BAR98] [SPA01]. Such characteristic presents advantages over the use of a global clock signal in modern technologies.

Asynchronous circuits can be classified according to several criteria. One important criterion is based on the delays of wires and gates. The most robust and restrictive delay model is the delayinsensitive (DI) model, which operates correctly regardless of gate and wire delay values. Unfortunately, this class is too restrictive. The addition of an assumption on wire delays in some carefully selected forks enables to define the quasi-delay-insensitive (QDI) circuit class. Here, signal transitions must occur at the same time only at each end point of the mentioned forks. QDI circuits are quite common, although other models, such as bundled-data [SPA01] are still used in specific contexts.

There are different ways to encode data to adequately support delay models. The use of regular binary encoding of data implies the use of separate request-acknowledge control signals. While this makes design straightforward for those used to synchronous techniques, the timing relationship between control and data signals needs to be guaranteed at every handshake point, making design of large asynchronous modules difficult and hardly scalable. As an alternative, DI encodings are robust to wire delay variations, because request signals are embedded within data signals. An example is the dual-rail encoding, that uses two wires to represent each bit, and can represent bit values as well as the absence of data. The request signal is computed from the data and therefore demands extra hardware. More efficient DI encodings exist and are discussed in detail in several publications e.g. in [AGY10].

#### 2.1.1 The Muller C-Element

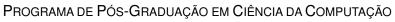

Most of the asynchronous design techniques proposed to date require devices other than the ordinary logic gates and flip-flops available in current standard cell sets. These include e.g. metastability filters, event fork, join and merge devices. Although most of these may be built from logic gates, in general this is inefficient. A fundamental part that enables to build such devices more effectively is the Muller C-element, also called just C-element [SPA01]. Its importance comes from the fact that C-elements operate as an event synchronizers. Figure 1 depicts the truth table and state diagram for a C-element with symmetric behavior. Its output may switch only when all

its inputs assume a same logical value. When inputs A and B are equal, the output Q assumes this same value. However, when these inputs are different, the output keeps the previous logic value. It is possible to build and use several alternative similar behaviors, by individually negating the inputs or the output, increasing the number of inputs and associating differentiated logic behavior to distinct inputs. This last characteristic produces the asymmetric C-elements, which are discussed for example in [TOM06].

Figure 1 – A basic 2-input C-Element truth table and its state diagram, assuming a symmetric behavior with regard to all inputs.

#### 2.1.2 Metastability

Metastability Filters are crucial components to implement asynchronous circuits. This is due to the fact that they guarantee a robust implementation of control elements, like arbiters. These elements are essential to compute data and take decisions for the correct operation of the circuit [SPA01]. The role of this component is to decide which of two concurrent events is to be served first. In ASCEnD, metastability filters have two request inputs (RA and RB), that receive requests, which can be concurrent, and two acknowledge outputs (AA and AB), that signal which event is to be served at the moment. The logical function of this component is showed in Equation (1). In the case of two events taking place in the exact same instant of time, e.g. simultaneous low-to-high transitions in RA and RB, the filter will eventually decide for one, eliminating the possibility of metastable states. This scenario, which is not covered by the logical function, is decided through an electric race, where the request with best potential is served first. Because AA and AB are mutually exclusive, the request with lower potential will only be served after the first finishes its communication.

$$AA = \overline{RB} \wedge RA$$

Equation (1)

$$AB = \overline{RA} \wedge RB$$

Equation (2)

## 2.2 Asynchronous EDA

With the growing interest for asynchronous circuits, different tools have been proposed, in order to automate asynchronous design. Among these, Balsa [SPA01] [BAR98] stands as a comprehensive open source environment. The tool was designed and is maintained by the Advanced Processor Technologies Group of the University of Manchester.

Balsa is both a language to describe asynchronous circuits and a framework to simulate and synthesize them. The compilation of a Balsa description is transparent, since language constructs

are directly mapped into handshake components [SPA01]. In this way, it is relatively easy for the designer to visualize the circuit-level architecture of a Balsa description, contrary to what happens in ordinary hardware description languages (HDLs) like VHDL and Verilog. Moreover, Balsa description changes reflect in predictable changes in the resulting circuit, which means that the designer has a clear control of the generated hardware.

Balsa requires the designer to give, through language operators, the order of handshake events, where these events mean communication between handshake components (data exchange or pure control) and can be sequential or concurrent. Moreover, handshake components are transparent and are given through higher abstraction language constructs. Therefore, one of the main advantages of using Balsa to describe and implement asynchronous circuits is that communication control between handshake components is abstracted. Due to the fact that all the complexity of describing control signals is transparent, the designer just needs to describe the data flow and implement its logic. The tool automatically generates the handshake components and the required control.

Different technologies can be used to synthesize Balsa circuit descriptions, from FPGA to ASICs. This work uses the previously mentioned ASCEnD, an in-house standard-cell library designed to support asynchronous circuits, fully compatible with the Balsa framework. In this way, netlists generated by Balsa can be imported into back-end commercial tools for physical implementation. Finally, Balsa allows the designer to choose the design style/encoding type used by the target circuit. The available choices are bundled-data/binary, QDI/dual-rail and QDI/1-of-4.

Another option to synthesize Balsa descriptions into a netlist of asynchronous devices is the open source system designed at the University of Manchester: Teak [BAR09]. It consists in a new target parameterizable component set and a synthesis scheme that aims at the improvement of circuits described in the Balsa language. The tool optimizes Balsa descriptions synthesis by replacing data-less activation channels with separate control channels. Albeit the Balsa System allows different data encodings over two- or four-phase protocols, Teak implementations are typically restricted to QDI, four-phase, dual rail implementations. Hence, circuits synthesized through this tool are limited to that choice of design style, protocol and data encoding.

## 3 ASYNCHRONOUS EDA CONTRIBUTIONS

The interest in non-synchronous circuits is increasing. The International Technology Roadmap for Semiconductors (ITRS) in its 2008 edition [ITR08] describes a clear need for asynchronous communication protocols in integrated circuits (ICs) control and synchronization along the next decades. For example, the ITRS estimates that global clock-based ICs, which comprised 93% of the chips sold worldwide in 2007, will have only 55% of the market by 2022. The other 45% of the chips will be local handshaking circuits, including clockless or multi-clock ICs. However, the lack of adequate electronic design automation (EDA) tools imposes a barrier to the design of asynchronous circuits. Most commercial EDA tools focus currently on purely synchronous designs.

In order to help overcoming the difficulty of implementing efficient asynchronous circuits, a design flow for C-Elements was proposed by the Author and a library of over 500 cells was designed for a 65nm technology.

### 3.1 C-Element Design Flow

A standard cell is an elementary device, such as a logic gate, defined at the chip layout level, with some predefined characteristics that usually comprise cell height and current driving strength. Chip vendors and associated enterprises provide designers with libraries of standard cells and support to define design methods based on them. Cells are characterized in detail, and their standardization facilitates automation of IC design. Most current Application Specific Integrated Circuit (ASIC) SoC designs use standard cells extensively, e. g. to meet time to market constraints. Indeed, standard cells are the key to speed up the design of high performance ICs and are often referred as the main success factor for the rapid growth of integrated systems technologies [ERIO3].

The efficient implementation of asynchronous circuits often requires devices other than those available at current commercial standard cell sets. Moreover, asynchronous design is in fact not a single alternative to the synchronous paradigm, but a collection of methods, several assuming the existence of a specific set of basic devices. Thus, no single set of new cells may be useful for every asynchronous design technique. In [MOR11a] a set of cells is proposed, along with an automated novel design and characterization flow. This enables the construction of asynchronous standard cell based ASICs. The cell set is integrated with the Teak System [BAR09], a synthesis tool for high level asynchronous circuit descriptions. Teak netlists are quasi delay insensitive (QDI) and employ 4-phase dual rail protocols. They can be placed and routed with commercial tools.

Some works propose methods to design asynchronous circuits with conventional IC design tools and standard cell libraries. For example, Chong et al. [CHO07] suggest a method that enables creating latch-based pipelines and an asynchronous latch controller for stage synchronization. As example design the work proposes an asynchronous FIR filter in a  $0.35\mu m$  CMOS process.

Cortadella et al. present the desynchronization paradigm [COR06] for automating the design of asynchronous circuits from synchronous specifications using synchronous tools. The design flow consists in exchanging each pipeline edge-triggered register by two level-sensitive latches with local handshake units for local synchronization, eliminating the need for a global clock. Combinational logic delays need to be matched in control lines. Validation occurs through desynchronized versions of a DES cryptography core and a DLX processor. None of these works exploit the asynchronous paradigm capabilities, limiting themselves to bundled-data protocols, which prevent the use of more robust and performing DI approaches [SPA01]. Moreover, the need to adjust combinational logic delays by hand results in circuits that are hard to reuse in other contexts. Additionally, both works assume the use of conventional standard cell libraries, which may lead to designs that spend more area and/or power.

The asynchronous literature proposes a few standard cell libraries. Ferretti and Beerel suggest the single-track full-buffer (STFB) template library, designed to support high-speed areaefficient asynchronous nonlinear pipeline designs [FER06]. It employs the TSMC 0.25µm technology and contains cells to support dual-rail and 1-of-3 data encoding circuits, being available through the MOSIS prototyping service. Ozdag and Beerel propose the QDI pre-charged half-buffer (PCHB) template library for asynchronous low-power high performance circuits [OZD06]. This library also uses TSMC 0.25µm and is equally available through MOSIS. It counts 40 dynamic cells to implement function blocks and 10 cells to implement control logic. Gulati and Brunvand describe a specific macro cell library to support the design of asynchronous microengines [GUL05]. The library employs the AMI 0.5μm technology, contains 66 cells and was validated through a test chip that implements a differential equation solver microengine. Most cells in the three discussed libraries display a short range of output load capacitance, due to the fact that they are deemed to validate a template-based design technique or support specific applications. Consequently, no fine grain optimization is proposed in the design of the libraries themselves. Besides, they limit the design of asynchronous circuits to specific templates. Other asynchronous design styles may require different sets of devices.

To overcome specificity issues, the French laboratories TIMA and LETI developed a library with cells to support more generic QDI circuit design. Maurine et al. present an STMicroelectronics 130nm technology version of this library [MAU03]. A private communication to the Author informs that this library is currently available in the STMicroelectronics 65nm CMOS process and several chip designs use it at the LETI laboratory.

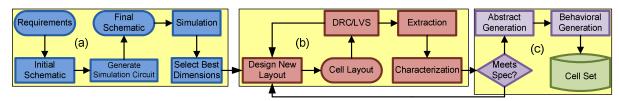

The work proposed in [MOR11a] is fully integrated with back-end commercial EDA tools and some front-end asynchronous tools. The cell subset this work addresses enables automatic generation of circuits from high level descriptions and allows designers to experiment with different asynchronous templates and styles like bundled-data and dual-rail DI. The cell design flow is fully automated, except for the physical cell layout generation and technology specific requirements.

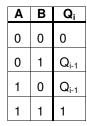

To enable implementing netlists generated by Teak in real processes, a very small specific set of standard cells is required. TABLE I shows this cell set. All cells are variations of the basic C-

element. The proposed flow for each cell appears in Figure 2 and comprises three main steps: specification, design and validation. To synthesize Balsa descriptions, Teak also needs conventional standard cells like ANDs, ORs and AND-OR-INVERTERs. These components are available in most conventional standard cell libraries.

TABLE I – Proposed cell set logic functions [MOR11a]. Q is the cell single output. RST is a reset signal. Note the last cell displays an asymmetric behavior.

| Cell | Logic Function                                                                           |

|------|------------------------------------------------------------------------------------------|

| C2   | $Q_{i+1} = (A \wedge Q_i) \vee (A \wedge B) \vee (Q_i \wedge B)$                         |

| C3   | $Q_{i+1} = (A \land B \land C) \lor (A \land Q_i) \lor (B \land Q_i) \lor (C \land Q_i)$ |

| C2R1 | $Q_{i+1} = RST \wedge ((A \wedge Q_i) \vee (A \wedge B) \vee (Q_i \wedge B))$            |

| C1U1 | $Q_{i+1} = B \wedge ((A \wedge B) \vee (Q_i \wedge B))$                                  |

Functionality is given as an expression defining the output(s) as a function of the circuit input(s), as in TABLE I. The electrical requirements consist in the cell speed for charging or discharging its output(s). The electrical specification of a standard cell is a tradeoff between area, power and speed. High performance gates require larger transistors and consequently consume more power and demand more silicon area. Usually, different cells with a same logical function support different output driving strengths. In the proposed flow, the designer defines the required cell speed to meet constraints or for compatibility with another gate set.

Figure 2 – Standard cell proposed design flow. The three main steps are: (a) Specification, (b) Design and (c) Validation. Actions are represented by boxes, decisions by diamonds, descriptions as rounded corner boxes and the repository as a cylinder.

The next step is to design an initial schematic of the cell. Figure 3 presents this schematic implementation for the logic function of the C2 cell from TABLE I, a 2-input C-element.

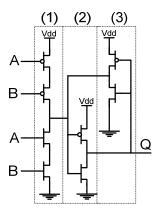

The schematic is then exported to a SPICE description. The basic structure of the example C-element (in fact, of any similar cell) can be represented by blocks (1), (2) and (3) of Figure 3. In [SHA98] a similar approach is used to implement C-elements in CMOS technologies. Here, (3) represents the state keeper, (2) is the output driving inverter and (1) is the inverted logic function. The first (state keeper) is usually set to minimum transistor sizes, since it does not influence the switching performance of the output and is used only to statically keep the cell state. Block (2) is responsible for driving (charging/discharging) the output load of the cell. Its transistors size is obtained by simulating an inverter with varying transistor sizing until the required output driving strength is obtained (as de-fined by the electrical specification).

Figure 3 – Examples of schematic for the C2 cell, a 2-input C-Element.

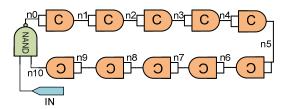

Once the dimensions of the driving inverter are fixed, a specifically tool designed in the context of this work, called Ring Oscillator Generator (ROGen) automatically produces a circuit that can be simulated to define the size of the transistors that compose block (1). This tool is implemented in C language. Its input is a configuration file and the schematic of a NAND cell of the target technology and the cell to be designed, which transistors are not yet dimensioned. The output is an oscillator ring, as presented in Figure 4, and its simulation environment, described in SPICE language.

The circuit generated by ROGen is the ring oscillator represented in Figure 4, composed by a NAND and 10 of the cells to be sized. The NAND controls the oscillation.

Figure 4 – Example of the gate level view of a simulation circuit generated by ROGen.

Next, extensive simulation defines the number of cell instances in the ring (10) as an amount sufficient to normalize the effect of the NAND in the circuit and allow correct evaluation of the C-element. The circuit is described in SPICE and variations on the size of the transis-tors are achieved through the use of the SPICE .alter function from minimum size to three-finger transistors with maximum size. A finger is the maximum transistor size that can be drawn without using layout folding.

Simulating the SPICE circuit description, information about electrical behavior of each transistor size is obtained through the SPICE .measure function. This information comprises: dynamic and leakage power of the whole ring, rise and fall propagation times and transition delay of each cell, and operating frequency of the whole ring. Leakage power is the average power consumed from the power source while the circuit is in a static state (IN=0) and the dynamic power is the average power consumption from the source when the ring is oscillating (IN=1). A second tool designed in the context of this work is the Cell Specifier (CeS). It is used to analyze the results obtained through simulation and choose the PMOS transistors size that best drives the cell

for each NMOS transistor size variation. Its input is the results generated by the simulation of the file generated by RoGen. The result is the set of the best PMOS-NMOS combination for each NMOS size variation. The output is a set of charts, showing all simulations and pointing the fastest combination.

Once the size of the transistors is defined, step (b) of Figure 2 flow may occur. From the circuit schematic, physical characteristics of the standard cell can be designed with the use of a layout editor. The layout must respect layout design rules, verified through a Design Rule Check (DRC) tool and Design for Manufacturability (DFM) rules along with a layout versus schematic (LVS) check. Once the layout is designed and fully verified, the parasitic effects must be extracted and electrically characterized for the specific process. The electrical characterization is a crucial step in the generation of standard cells, since it defines the behavior of the circuit for different operating conditions and generates information required by EDA tools. After characterization, a cell must be properly verified.

The last flow step consists in the validation of the cell by checking if the information generated during characterization is equivalent to that defined in the specification. Moreover, timing simulation must be carried out for a design composed by a single cell to check if the delay obtained during characterization is correctly annotated and the behavioral description is followed. If the cell passes this verification step, it can be used in a design.