# PONTIFÍCIA UNIVERSIDADE CATÓLICA DO RIO GRANDE DO SUL FACULDADE DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

## EVALUATION OF SYSTEM-LEVEL IMPACTS OF A PERSISTENT MAIN MEMORY ARCHITECTURE

TACIANO PEREZ

Dissertação apresentada como requisito parcial à obtenção do grau de Mestre em Ciência da Computação na Pontifícia Universidade Católica do Rio Grande do Sul.

Orientador: CÉSAR A. F. DE ROSE

Porto Alegre 2012

| ] | <ul> <li>438e Perez, Taciano<br/>Evaluation of system-level impacts of a persistent main<br/>memory architecture / Taciano Perez. – Porto Alegre, 2012.<br/>105 f.</li> </ul> |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Diss. (Mestrado) – Fac. de Informática, PUCRS.<br>Orientador: Prof. Dr. César A. F. De Rose.                                                                                  |

|   | 1. Informática. 2. Arquitetura de Computador. 3. Memória de<br>Computador. I. De Rose, César A. F. II. Título.                                                                |

|   | CDD 004.22                                                                                                                                                                    |

|   |                                                                                                                                                                               |

Ficha Catalográfica elaborada pelo Setor de Tratamento da Informação da BC-PUCRS

## TERMO DE APRESENTAÇÃO DE DISSERTAÇÃO DE MESTRADO

Dissertação intitulada "*Evaluation of System-Level Impacts of a Persistent Main Memory Architecture"*, apresentada por Taciano Dreckmann Perez como parte dos requisitos para obtenção do grau de Mestre em Ciência da Computação, Processamento Paralelo e Distribuído, aprovada em 15/03/2012 pela Comissão Examinadora:

Prof. Dr. César Augusto Fonticielha De Rose - Orientador

Prof. Dr. Ney Laert Vilar Calazans -

PPGCC/PUCRS

PPGCC/PUCRS

Prof. Dr. Rodolfo Jardim de Azevedo -

UNICAMP

Prof. Dr. Paulo Henrique Lemelle Fernandes Coordenador.

**Campus Central** Av. Ipiranga, 6681 – P32– sala 507 – CEP: 90619-900 Fone: (51) 3320-3611 – Fax (51) 3320–3621 E-mail: <u>ppgcc@pucrs.br</u> www.pucrs.br/facin/pos

"Disks are a hack, not a design feature.

The time and complexity penalty for using disks is so severe that nothing short of enormous cost-differential could compel us to rely on them. Disks do not make computers better, more powerful, faster, or easier to use. Instead, they make computers weaker, slower, and more complex. They are a compromise, a dilution of the solid-state architecture of digital computers. (...)

Wherever disk technology has left its mark on the design of our software, it has done so for implementation purposes only, and not in the service of users or any goal-directed design rationale."

Alan Cooper, About Face 2.0 [18]

### ACKNOWLEDGEMENTS

This work was crafted along 4 years across two organizations: Hewlett-Packard, where I've been working during the last decade, and PUCRS, where this research took place. I have received the gifts of a creative environment, financial support, and computing infrastructure from both these organizations, and without any of them, this work would have never been possible.

The idea for this research was inspired by a presentation on Memristor made by Greg Astfalk in 2008, who has since then been very supportive of this work, discussing ideas, reviewing reports and articles, and helping me connect to people who contributed to the final result. I cannot find words to thank him enough for his support.

César A. F. De Rose, my advisor, encouraged me to come up with an original research theme, and led me wisely and patiently through the challenge that is conducting such an endeavour. He taught me how to successfully navigate in an academic environment, and whenever I faced an obstacle, he was there to help me remove it.

Ney Laert Vilar Calazans acted as a co-advisor, and enlightened me on several discussions regarding hardware modeling and simulation, particularly concerning the energy model employed in this experiment. He also contributed with thorough and detailed reviews of early texts.

Several people on Hewlett-Packard supported this work in different forms. Eduardo Arioli, my manager, always made efforts to provide me basic means to craft this research. Marcelo Thielo believed in this work before I did, and encouraged me to move forward towards this particular theme. Katia Saikoski, Karin Becker and Luis Saraiva provided assistance for me to make the first moves towards an academic research.

The team of the PUCRS high-performance computing lab (LAD - Laboratório de Alto Desempenho) provided critical help for the experiment, particularly Raquel Dias who set up the whole environment. The staff of PPGCC office, especially Thiago Lingener and Régis Escobal da Silva, were of great assistance during the 4 years that this work was developed.

There are several important people in my life that contributed directly or indirectly to this work: friends, family, colleagues. I won't cite any names, for they know who they are. I thank you very much for being there.

This work is dedicated, in loving memory, to my grandmother Iris Vezzani Perez.

## EVALUATION OF SYSTEM-LEVEL IMPACTS OF A PERSISTENT MAIN MEMORY ARCHITECTURE

### ABSTRACT

For almost 30 years, computer memory systems have been essentially the same: volatile, high speed memory technologies like SRAM and DRAM used for cache and main memory; magnetic disks for high-end data storage; and persistent, low speed flash memory for storage with low capacity/low energy consumption requirements such as embedded/mobile devices. Today we watch the emergence of new non-volatile memory (NVM) technologies that promise to radically change the landscape of memory systems. In this work we assess system-level latency and energy impacts of a computer with persistent main memory using PCRAM and Memristor. The experimental results support the feasibility of employing emerging non-volatile memory technologies as persistent main memory, indicating that energy improvements over DRAM should be significant. This study has also compared the development and execution of applications using both a traditional filesystem design and a framework specific of in-memory persistence (Mnemosyne). It concludes that in order to reap the major rewards potentially offered by persistent main memory, it is necessary to take new programming approaches that do not separate volatile memory from persistent secondary storage.

Keywords: Non-Volatile Memory; Persistent Main Memory; PCRAM; RRAM; Memristor.

## AVALIAÇÃO DE IMPACTOS EM NIVEL DE SISTEMA DE UMA ARQUITETURA DE MEMÓRIA PRINCIPAL PERSISTENTE

## RESUMO

Por cerca de 30 anos, os sistemas de memória computacional têm sido essencialmente os mesmos: tecnologias de memória volátil de alta velocidade como SRAM e DRAM utilizadas para caches e memória principal; discos magnéticos para armazenamento persistente; e memória flash, persistente e de baixa velocidade, para armazenamento com características de baixa capacidade e baixo consumo de energia, tais como dispositivos móveis e embarcados. Hoje estão emergindo novas tecnologias de memória não-volátil, que prometem mudar radicalmente o cenário de sistemas de memória. Neste trabalho são avaliados impactos (em nível de sistema) de latência e energia supondo um computador com memória principal persistente usando PCRAM e Memristor. Os resultados experimentais suportam a viabilidade de se empregar tecnologias emergentes de memória não-volátil como memória principal persistente, indicando que as vantagens de consumo de energia com relação a DRAM devem ser significativas. Esse estudo também compara o desenvolvimento de aplicações usando tanto uma abordagem tradicional usando sistema de arquivos quanto utilizando um framework específico para persistência em memória. Conclui-se que, para colher os principais benefícios potencialmente oferecidos por memória principal persistente, é necessário utilizar novas abordagens de programação que não estabelecem uma separação entre memória volátil e armazenamento secundário.

Palavras-chave: Memória não-volátil; Memória principal persistente; PCRAM; RRAM; Memristor.

# LIST OF FIGURES

| Figure 2.1 | Concept of memory hierarchy                              | 28 |

|------------|----------------------------------------------------------|----|

| Figure 2.2 | Processor caches: logical organization.                  | 29 |

| Figure 2.3 | 6-T SRAM cell.                                           | 29 |

| Figure 2.4 | DRAM cell and array organization.                        | 31 |

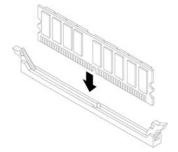

| Figure 2.5 | DIMM Module                                              | 31 |

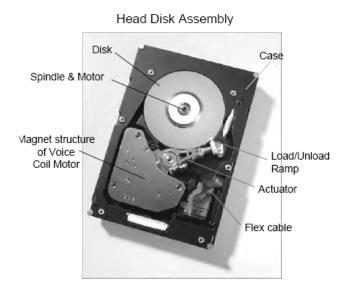

| Figure 2.6 | HDD internals overview                                   | 33 |

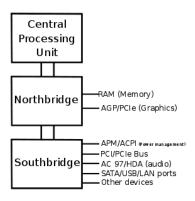

| Figure 2.7 | Typical north/southbridge layout                         | 34 |

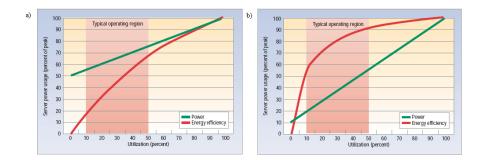

| Figure 2.8 | Relationship between power and energy-efficiency.        | 37 |

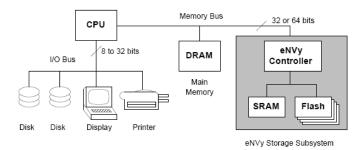

| Figure 3.1 | Typical PC organization                                  | 39 |

| Figure 3.2 | Organization of a SRAM processor cache                   | 41 |

| Figure 3.3 | Basic organization of DRAM internals                     | 42 |

| Figure 3.4 | Logical organization of wide-out DRAMs                   | 42 |

| Figure 3.5 | DIMMs, ranks, banks and arrays in a DRAM system          | 43 |

| Figure 3.6 | JEDEC-style memory bus organization.                     | 44 |

| Figure 3.7 | Steps of a DRAM read.                                    | 46 |

| Figure 3.8 | Model of a HDD attached to a host via an interface       | 47 |

| Figure 4.1 | Phase-change memory cell                                 | 50 |

| Figure 4.2 | I-V relationship in a memristor (hysteresis loop)        | 51 |

| Figure 4.3 | How memristance works                                    | 52 |

| Figure 4.4 | MTJ conceptual view                                      | 53 |

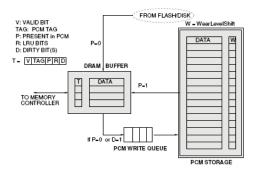

| Figure 5.1 | High-level eNVy architecture                             | 58 |

| Figure 5.2 | Hybrid DRAM-PCRAM main memory system.                    | 61 |

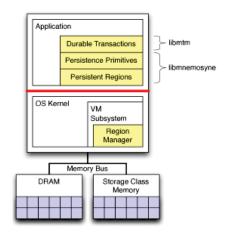

| Figure 5.3 | Mnemosyne architecture                                   | 65 |

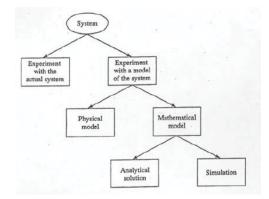

| Figure 6.1 | Taxonomy of the ways to study a system                   | 71 |

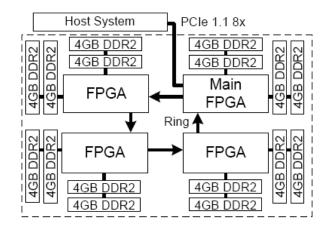

| Figure 6.2 | HASTE system.                                            | 76 |

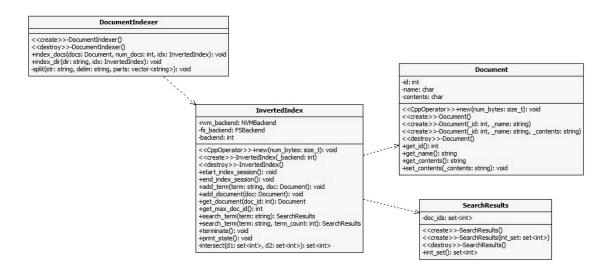

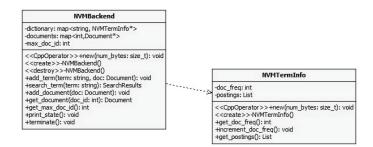

| Figure 7.1 | UML class diagram of index and search subsystem          | 81 |

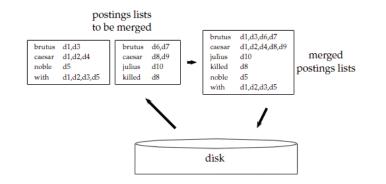

| Figure 7.2 | Merging in blocked sort-based indexing                   | 82 |

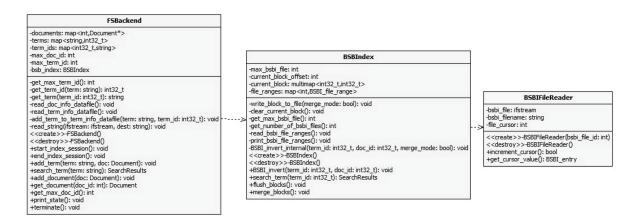

| Figure 7.3 | UML class diagram of file-based storage subsystem.       | 82 |

| Figure 7.4 | UML class diagram of persistent memory storage subsystem | 83 |

| Figure 8.1 | Napier88 architecture                                    | 94 |

# LIST OF TABLES

| Table 2.1 | Comparison of current memory/storage technologies   | 35 |

|-----------|-----------------------------------------------------|----|

| Table 4.1 | DRAM x RRAM comparison                              | 53 |

| Table 4.2 | Comparison of memory technologies.                  | 55 |

| Table 5.1 | Mnemosyne programming interface                     | 66 |

| Table 7.1 | Experimental target configuration setup.            | 78 |

| Table 7.2 | Technology parameters for DRAM, Memristor and PCRAM | 78 |

| Table 7.3 | Workload Development Environment                    | 84 |

| Table 7.4 | Workload development: size and effort metrics       | 85 |

| Table 7.5 | Execution times for experimental workloads.         | 86 |

| Table 7.6 | Cache hits during experimental workloads.           | 86 |

| Table 7.7 | Energy consumption of experimental workloads, in J  | 87 |

# LIST OF ABBREVIATIONS

| API     | Application Programming Interface          |

|---------|--------------------------------------------|

| АТА     | Advanced Technology Attachment             |

| BSBI    | Blocked Sort-Based Index                   |

| CAS     | Column Address Strobe                      |

| CB      | Copy Buffer                                |

| CPU     | Central Processing Unit                    |

| DIMM    | Dual In-line Memory Module                 |

| DRAM    | Dynamic Random-Access Memory               |

| ETTNW   | Estimated Time To Next Write               |

| FC      | Fibre Channel                              |

| HDD     | Hard Disk Drive                            |

| JEDEC   | Joint Electron Devices Engineering Council |

| LOC     | Lines Of Code                              |

| MRAM    | Magnetoresistive Random-Access Memory      |

| NVM     | Non-Volatile Memory                        |

| OS      | Operating System                           |

| PCRAM   | Phase-Change Random-Access Memory          |

| PCM     | Phase-Change Memory                        |

| PRAM    | Phase-change Random-Access Memory          |

| RAM     | Random-Access Memory                       |

| RAS     | Row Address Strobe                         |

| RBT     | Red-Black Tree                             |

| RRAM    | Resistive Random-Access Memory             |

| SAS     | Serial Attached SCSI                       |

| SATA    | Serial Advanced Technology Attachment      |

| SCSI    | Small Computer Systems Interface           |

| SRAM    | Static Random-Access Memory                |

| STL     | Standard Template Library                  |

| STT-RAM | Spin-Torque Transfer Random-Access Memory  |

| TML     | Tunelling Magneto-Resistance               |

| UML     | Unified Modeling Language                  |

|         |                                            |

# TABLE OF CONTENTS

## 1. INTRODUCTION

| 2. | CUR  | RENT N  | IEMORY TECHNOLOGIES                   | 27       |

|----|------|---------|---------------------------------------|----------|

|    | 2.1  | Memor   | ry Hierarchy                          | 27       |

|    | 2.2  | Proces  | sor Cache: SRAM                       | 28       |

|    | 2.3  | Main M  | Memory: DRAM                          | 30       |

|    | 2.4  | Persist | ent Storage: Disk, Flash              | 32       |

|    |      | 2.4.1   | Disk                                  | 32       |

|    |      | 2.4.2   | Flash                                 | 33       |

|    | 2.5  | Limitat | tions of Current Memory Technologies  | 34       |

| 3. | MEM  | IORY S  | YSTEM ORGANIZATION                    | 39       |

|    | 3.1  | Overvie | ew                                    | 39       |

|    | 3.2  | Cache   |                                       | 40       |

|    | 3.3  | Main M  | Memory                                | 42       |

|    | 3.4  |         |                                       | 45       |

| Л  |      |         | MEMORY TECHNOLOGIES                   | 49       |

| 4. | 4.1  |         |                                       | 49<br>49 |

|    |      |         | Change RAM (PCRAM)                    | -        |

|    | 4.2  |         | ve RAM (RRAM)                         |          |

|    | 1 2  | 4.2.1   | Memristor                             | 51<br>53 |

|    | 4.3  |         | toresistive RAM (MRAM)                |          |

|    | A A  |         | STT-RAM                               | 54       |

|    | 4.4  | Compa   | rison Between Memory Technologies     | 54       |

| 5. | PERS | SISTEN  | T MAIN MEMORY                         | 57       |

|    | 5.1  | Persist | ent Main Memory Architectures         | 57       |

|    |      | 5.1.1   | Pioneer Work: Flash-based Main Memory | 57       |

|    |      | 5.1.2   | PCRAM As Main Memory                  | 58       |

|    |      | 5.1.3   | Hybrid PCRAM-DRAM Main Memory         | 60       |

|    | 5.2  | Hardwa  | are Impacts                           | 62       |

|    | 5.3  | Softwa  | re Impacts                            | 64       |

|    |      | 5.3.1   | Mnemosyne                             | 65       |

|    |      | 5.3.2   | NV-heaps                              | 67       |

|    |      | 5.3.3   | CDDS                                      | . 69 |

|----|------|---------|-------------------------------------------|------|

| 6. | MEM  | ORY S   | SYSTEM MODELING                           | 71   |

|    | 6.1  | Overvi  | iew                                       | . 71 |

|    | 6.2  | Analyt  | tical Models                              | . 72 |

|    |      | 6.2.1   | CACTI                                     | . 72 |

|    |      | 6.2.2   | Memristor Analytical Model                | . 72 |

|    |      | 6.2.3   | SPICE                                     | . 73 |

|    |      | 6.2.4   | NVSim                                     | . 73 |

|    | 6.3  | Microa  | architectural Simulators                  | . 73 |

|    |      | 6.3.1   | DRAMSim                                   | . 73 |

|    |      | 6.3.2   | ΜϲΡΑΤ                                     | . 73 |

|    |      | 6.3.3   | SESC                                      | . 74 |

|    |      | 6.3.4   | SimpleScalar                              | . 74 |

|    | 6.4  | Full-Sy | ystem Simulators                          | . 74 |

|    |      | 6.4.1   | COTSon                                    | . 75 |

|    |      | 6.4.2   | GEMS                                      | . 75 |

|    |      | 6.4.3   | Simics                                    | . 75 |

|    |      | 6.4.4   | M5                                        | . 75 |

|    | 6.5  | Hardw   | vare Simulators                           | . 76 |

|    |      | 6.5.1   | HASTE                                     | . 76 |

| 7. | EXPE | RIMEN   | NTAL EVALUATION OF PERSISTENT MAIN MEMORY | 77   |

|    | 7.1  | Experi  | imental Setup                             | . 77 |

|    |      | 7.1.1   | Simulation Target System                  | . 77 |

|    |      | 7.1.2   | Memory Technology Scenarios               | . 77 |

|    |      | 7.1.3   | Energy Model                              | . 79 |

|    | 7.2  | Experi  | imental Workloads                         | . 79 |

|    |      | 7.2.1   | Workload Task                             | . 79 |

|    |      | 7.2.2   | Corpus                                    | . 80 |

|    |      | 7.2.3   | Workload Design and Implementation        | . 80 |

|    |      | 7.2.4   | Development Metrics                       | . 83 |

|    |      | 7.2.5   | Development Challenges                    | . 84 |

|    | 7.3  | Execut  | tion Results and Analysis                 | . 85 |

| 8. | FUTU | JRE RE  | ESEARCH PERSPECTIVES                      | 89   |

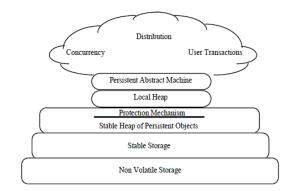

|    | 8.1  | Orthog  | gonal Persistence                         | . 90 |

| 8.1.1        | Orthogonal Persistence and Programming Languages | 91 |

|--------------|--------------------------------------------------|----|

| 8.1.2        | Limitations of Orthogonal Persistence            | 95 |

|              |                                                  |    |

| 9. CONCLUSIC | N                                                | 97 |

| Bibliography |                                                  | 99 |

Bibliography

### **1. INTRODUCTION**

For almost 30 years the memory hierarchy used in computer design has been essentially the same: volatile, high speed memory technologies like SRAM and DRAM used for cache and main memory; magnetic disks for high-end data storage; and persistent, low speed flash memory for storage with low capacity/low energy consumption requirements, such as embedded/mobile devices [31].

Today we watch the emergence of new memory technologies under research that promise to change significantly the landscape of memory systems. Non-Volatile Memory (NVM) technologies such as Phase-Change RAM (PCRAM), Magnetic RAM (MRAM) and Resistive RAM (RRAM) will possibly enable memory chips that are non-volatile, require low-energy and have density and latency closer to current DRAM chips [13].

Even though most of these technologies are still in early prototyping stages, their expected properties in terms of area, latency, energy and endurance are already estimated. Based on these estimations, several papers have been published proposing practical applications for these new NVM technologies. These papers provide initial insight on what the impacts on memory systems should be if such technologies evolve to be competitive in the market. A survey of these studies was presented in a previous work [52].

The memory system is one of the most critical components of modern computers. It has attained a high level of complexity due to the many layers involved in memory hierarchy: application software, operating system, cache, main memory and disk. Any relevant change in one level of the memory hierarchy (such as the introduction of the aforementioned NVM technologies) can potentially impact several other layers and overall system behavior. For this reason, it is essential to consider the different possible scenarios for using these new memory technologies from a broad perspective.

The are several research projects in motion to create "Universal Memory" [52], a single memory technology that could replace all different memory technologies of today (SRAM, DRAM, disk and flash). It is not yet clear if the Universal Memory vision can be realized by NVM technologies under research, but the creation of a byte-addressable, non-volatile solid state memory could make a significant amount of persistent main memory available to computer systems, allowing to consolidate these two different levels of the storage hierarchy - main memory and persistent storage - into a single level, something that has never been possible before (at least not in mass scale). The advent of main memory as the primary persistent storage can affect deeply the complete computing stack, including application software, operating system, busses, memory system and its interaction with other devices, such as processors and I/O adapters [58, 68]. In order to fully assess system-wide impacts in latency, energy, heat, space and cost, it is required to take into account all these different layers when modeling or simulating a hypotethical computer system with persistent main memory.

In this work we evaluate the impacts on latency and energy of a computer system with persistent main memory, through the use of simulation. We simulate scenarios of systems using different technologies for main memory (DRAM, PCRAM and Memristor) using a full-system architectural

simulator (Virtutech Simics [42]), and compare the execution of worloads using both a typical scenario using the filesystem as storage backend and an API specific for in-memory persistence (Mnemosyne [69]).

Preliminary results were published in [51].

This work is organized in the following way:

- Chapter 2 presents the current technologies used in memory and storage hierarchy.

- Chapter 3 discusses the current organization of computer memory.

- Chapter 4 presents some of the emerging non-volatile memory technologies.

- Chapter 5 discusses the impacts of these emerging memory technologies concerning how they can contribute to create computers with **persistent main memory**.

- Chapter 6 surveys **tools for modeling/simulating** systems with hypothetical new architectures, especially where memory subsystem is concerned.

- Chapter 7 describes the **evaluation methodology**, **results** and **analysis** concerning the execution of workloads in a simulated persistent main memory computer.

- Chapter 8 discusses potential **perspectives for future research** towards computation with persistent main memory.

- Chapter 9 concludes this study summarizing the main findings of this research.

### 2. CURRENT MEMORY TECHNOLOGIES

In order to discuss the emergent NVM technologies, it is necessary to start by summarizing the current state of memory systems. This is a well-known subject, and we have extracted most of the information present in this section from the comprehensive textbook *Memory Systems: Cache, DRAM, Disk* by Bruce Jacob, Spencer W. Ng and David T. Wang [31] and Ulrich Drepper's online paper *What Every Programmer Should Know About Memory* [25].

#### 2.1 Memory Hierarchy

An ideal memory system would be fast, cheap, persistent and big (highly dense). Until now, all known memory/storage technologies address only some of these characteristics. Static RAM (SRAM) is very fast, but it's expensive, has low density and is not persistent. Dynamic RAM (DRAM) has better densities and is cheaper (but still expensive) at the cost of being a little slower, and it's not persistent as well. Disks are cheap, highly dense and persistent, but very slow. Flash memory is between DRAM and disk; it is a persistent solid-state memory with higher densities than DRAM, but its write latency is much higher than the latter.

Fortunately, it is possible to design a memory system that incorporates all these different technologies in a single **memory hierarchy**. Such hierarchy allows the creation of a system that approaches the performance of the fastest component, the cost of the cheapest component and energy consumption of the most power-efficient component. This is possible due to a phenomenon known as **locality of reference**, so named because memory references tend to be localized in time and space. This can be so summarized:

- If you use something once, you are likely to use it again (temporal locality).

- If you use something once, you are likely to use its neighbor (spatial locality) [31].

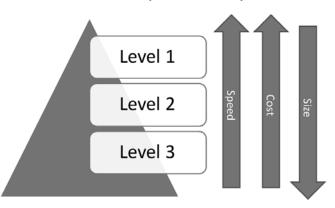

This phenomenon can be exploited by creating different memory levels; the first levels are smaller and more expensive, but have fastest access, and the other layers are progressively bigger and cheaper, but have larger access times. Appropriate heuristics are then applied to decide which data will be accessed more often and place them at the first levels, and move the data down on the hierarchy as it ceases to be used frequently. Figure 2.1 depicts the concept of memory hierarchy.

For at least the last 30 years, we have been building memory hierarchies that rely on SRAM for caches, DRAM for main memory and disk or flash as persistent storage. In the next sections we will describe these technologies in more detail.

## Memory Hierarchy

Figure 2.1: Diagram illustrating the concept of memory hierarchy.

### 2.2 Processor Cache: SRAM

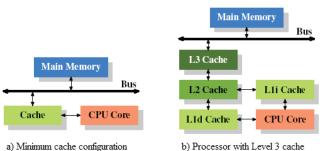

**Caches** are used to store frequently used information close to who needs it. They are used at several layers of computer architecture, but probably the most important are processor caches. In order to explore locality of reference, we need to place memory with very fast access close to the processor. The result is that processor caches reside between the processor and main memory, as depicted in Figure 2.2a.

Processor caches usually are **transparent caches**, meaning that the same addressing space is shared between the cache and the backing storage. When the processor asks for the contents of a specific memory address, these contents are first searched in the cache. If they are found (a **cache hit**), they are immediately returned. If they are not found (a **cache miss**), the memory system goes on to the next hierarchy level (e.g., main memory) and fetches the result. If there is a high probability that the returned result will be used again in the future, it is stored in the cache as well. Diverse heuristics can be used to manage cache content [31].

The speed of a cache is typically in inverse proportion to its size. This happens because the more addresses a cache can contain, more search needs to be done in order to determine whether there is a cache hit or miss. For this reason, modern computers have more than one cache level, frequently up to 3 levels. It is also common to have a separate Level 1 cache for instructions and another for data. Figure 2.2b shows a processor with such an organization. Since the same data can reside in different cache levels (as well as in the backing storage), transparent caches use techniques to ensure consistency between copies in these different levels.

Finally, it is important to mention that modern computers frequently have multi-processor, multi-core and multi-thread architectures. Usually each core has its own Level 1 instruction and data cache, and all cores in the same processor share Level 2 and 3 caches. Such organization is depicted in Figure 2.2c. Please notice that this is not a rule: several architectures can explore different organizations. This example is provided just as an illustration of an architecture commonly found today [25].

a) Minimum cache configuration

c) Multi-processor, multi-core, multi-thread

Figure 2.2: Processor caches: logical organization. Extracted from Drepper, 2007 [25].

Figure 2.3: 6-T SRAM cell. Extracted from Drepper 2007 [25].

As we can see, processor caches have some distinctive requirements:

- 1. They need to be very fast.

- 2. They can be small (in fact, to a certain extent, they need to be small to save search time).

- 3. Since they are small, it is acceptable if their cost/bit is expensive when compared to other components of memory hierarchy.

Today, the technology that best matches this set of requirements is Static Random Access Memory (SRAM).

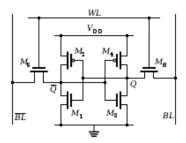

The most common SRAM cell design uses 6 transistors as shown in Figure 2.3. The cell core is comprised of the four transistors M1 to M4 which form two cross-coupled inverters. They have two stable states, representing 0 and 1. The state is stable as long as power on Vdd is available. If access to the state of the cell is needed the word access line WL is raised. This makes the state of the cell immediately available for reading on BL and BL. If the cell state must be overwritten the BL and BL lines are first set to the desired values and then WL is raised [25].

SRAM has some properties that are important for our discussion:

- The cell state is available for reading almost immediately once the word access line WL is raised, making its access very fast.

- The SRAM cell is complex, requiring six transistors in the most common design. This takes up space, and for this reason SRAM has lower densities than other technologies (such as DRAM).

- SRAM is more expensive in a cost/bit comparison.

- Maintaining the state of the cell requires constant power.

Essentially, SRAM is currently preferred for caches because it is very fast; the fact that it is less dense and more expensive is not as relevant for processor caches as access speed.

#### 2.3 Main Memory: DRAM

A computer program is comprised of a set of instructions, and it manipulates data while it is being executed. The place where both instructions and data are loaded during program execution is **main memory**. We have already seen that some of the most frequently used data are kept in cache to lower access time, but most of the memory addressing space used by a program usually is stored in main memory.

Almost every computer uses **virtual memory**, a technique that allows for an addressing space greater than the actual main memory capacity. When there is a request for memory allocation beyond main memory's boundaries, **page swapping** is used to temporarily send to the backing storage (usually disk or flash) a set of memory pages that is not immediately needed and reclaim their space. When those pages are needed again, they are fetched from the backing storage in exchange of another set of pages, and so on. Since this is an expensive process, page swapping is avoided whenever possible.

Based on this understanding, we can devise some requirements for main memories:

- 1. They need to be big enough to hold most of the data needed by a program to execute (to avoid paying too often the performance price of page swapping).

- 2. They can be slower than caches, since the most frequently used data are already being cached.

- 3. Their cost/bit needs to be lower than caches, since they need more capacity.

The technology that best fits into this description today is **Dynamic Random Access Memory (DRAM)**.

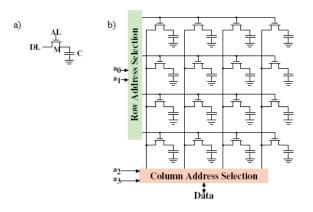

A typical DRAM cell has one transistor and one capacitor, as shown is Figure 2.4a. It keeps its state in capacitor C. The transistor M is used to provide access to the state. To read the state of the cell the access line AL is raised; this either causes a current to flow on the data line DL or not, depending on the charge in the capacitor. To write to the cell the data line DL is appropriately set and then AL is raised for a time long enough to charge or drain the capacitor. A DRAM cell

Figure 2.4: a) DRAM cell and b) DRAM array organization. Extracted from Drepper 2007 [25].

Figure 2.5: A dual in-line memory module (DIMM) with two ranks of nine banks each.

is much simpler than a SRAM cell, allowing for greater memory density (being a smaller cell) and lower manufacturing cost [25].

Despite these advantages, DRAM has a number of drawbacks when compared to SRAM. In order to allow huge numbers of cells, the capacity of the capacitor must be low. It only takes a short time for the capacity to dissipate, which is known as "charge leakage". In order to address this problem, DRAM cells must be refreshed frequently (every 64ms in most current DRAM devices). This tiny charge also creates another issue: the information read from the cell is not immediately usable, since the data line must be connected to a sense amplifier which can distinguish between a stored 0 or 1. Finally, the capacitor is discharged by read operations, so every read operation must be followed by an operation to recharge the capacitor. This requires time and energy [25].

DRAM cells are grouped together in **arrays**, as shown in Figure 2.4b. Each cell is at a cross-point of a row and a column. Both a row and a column need to be selected in order to read the content of that particular cell. Several arrays are read at the same time to provide the contents of a memory word. This group of arrays ganged together are called **banks**. Banks are aggregated in hardware modules called **Dual In-line Memory Modules (DIMMs)**. Each DIMM has one or two **ranks** of banks. Figure 2.5 shows a DIMM with two ranks of nine banks each [31].

The essential characteristics of DRAM can be thus summarized:

DRAM cells are simple, allowing high densities at a low cost/bit (when compared to SRAM).

- DRAM is slower than SRAM, yet still fast.

- Constant refreshes due to current leakage make DRAM power-consuming.

These properties make DRAM the best match for the main memory technology requirements previously listed.

#### 2.4 Persistent Storage: Disk, Flash

Beyond using data during computations, there is need to store data even when computers are turned off. The requirements for persistent storage can be so described:

- 1. It must be permanent, retaining data for several years without energy supply.

- 2. It must be very dense, allowing the storage of huge amounts of data in a tiny space.

- 3. Its cost/bit must be very low.

- 4. It is acceptable for persistent storage to be slower than main memory (given that it is the last memory/storage hierarchy level).

It is important to notice that, in an ideal world, there would be no distinction between main memory and persistent storage. If there was a single memory technology that could satisfy both the requirements for main memory and for persistent storage (requirements 1-3 above), there wouldn't be a separation between these two layers. Since there is still no such technology, we consider acceptable the 4th requirement mentioned above.

There are two main technologies which match these characteristics today: disk and flash.

#### 2.4.1 Disk

The most common storage technology today is the **Hard Disk Drive (HDD, or simply "disk")**. Magnetic disks have been around since the 50s, and they have been for a long time the preponderant storage media. Most personal and enterprise computers employ disks as their persistent storage.

HDDs exploit the properties of ferromagnetic materials to retain magnetic fields. A typical HDD (depicted in Figure 2.6) has one or more **disk platters** with a magnetic coat. Data is read/written by a **head** device, that can induce or sense magnetism in the disk. A central axis, called spindle, rotates the disk. Together with the **actuator**, which moves the head between the center and the border of the disk, all disk surface can be reached by the head. HDDs also have circuitry to convert disk data to electronic form and communicate with the computer's I/O subsystem.

Disks have great areal density (bits/square inch) and a very low cost/bit, and for this reason have been the most used persistent storage for a long time. Their drawbacks are related to the fact that disks are mechanical devices with moving parts. Every time a block is accessed, the HDD needs to rotate the spindle and move the actuator in order to place the head at the appropriate place. This

Figure 2.6: Hard disk internals overview. Reproduced from [31].

takes significantly more time than for doing the same operation in a solid-state memory technology such as SRAM or DRAM. In order to keep response times high, disks are kept continually spinning, which consumes additional energy.

These are the main steps that contribute to the time needed to complete a random disk I/O:

- 1. **Command overhead** the time needed by the disk drive's microprocessor and electronics to process and handle an I/O request. It can be sped up by disk caches.

- Seek time the time to move the read/write head from its current cylinder to the target cylinder of the next command. Because it is mechanical time, it is one of the largest contributors to I/O time.

- Rotational latency the time it takes for the disk rotation to bring the start of the target sector to the head. It is also mechanical time, being another major contributor for overall I/O time.

- 4. Data transfer time the time it takes to transfer data to/from the disk drive. It depends on data rate and transfer size. There are two distinct relevant data rates: *media data rate*, associated with how fast data can be transfered to and from the magnetic media, and *interface data rate*, associated with how fast can data be transferred between the disk drive and the host over the interface.

### 2.4.2 Flash

**Flash** memories, a type of non-volatile solid-state memory, have been built since the beginning of the 80s and dominate some niche markets today. Flash is more limited than disk regarding capacity

Figure 2.7: A typical north/southbridge layout. Extracted from http://en.wikipedia.org/wiki/Southbridge\_(computing).

and endurance, but has much lower power consumption and thus are very suitable for mobile and embedded devices.

Flash cells are floating-gate devices that can be erased electrically. There are two major kinds of flash memories: NOR and NAND. In NOR memory, each cell in a memory array is directly connected to the wordlines and bitlines of the memory array. NAND memory devices are arranged in series within small blocks. Thus, while NAND flash can inherently be packed more densely than NOR flash, NOR flash offers significantly faster random access [13]. Due to cell density, NAND flash is the preferred type for persistent storage.

Flash is faster than disk and consumes less energy. However, it has some drawbacks that prevent it from replacing disks except for some niche applications: less density, higher cost/bit and lower endurance [13].

Both disks and NAND flash are **block devices**. Typically they are not directly addressed by the processor, like main memory, but their contents must be moved from persistent storage to memory so the processor is able to manipulate them, and must be moved from memory to persistent storage at the end of processing. This process is not transparent to the processor, and is usually managed at Operating System (OS) level. Traffic between the processor and main memory (including off-chip caches) is made through a high-speed memory controller bus, also known as **northbridge**. Access to block devices is made through the slower I/O controller hub known as **southbridge**. Figure 2.7 shows the typical relationship between the processor, the northbridge and the southbridge.

#### 2.5 Limitations of Current Memory Technologies

The memory subsystem has become one of the most important topics in computer design. As Bruce Jacob [31] put it,

"The increasing gap between processor and memory speeds (...) is so severe we are now one of those down-cycles where the processor is so good at number-crunching it has completely sidelined itself; it is too fast for its own good, in a sense. (...) memory

|                       | SRAM                | DRAM               | Disk                 | NAND Flash         |

|-----------------------|---------------------|--------------------|----------------------|--------------------|

| Density               | >100 F <sup>2</sup> | 6-8 F <sup>2</sup> | (2/3) F <sup>2</sup> | 4-5 F <sup>2</sup> |

| Read Latency          | <10 ns              | 10-60 ns           | 8.5 ms               | 25 µs              |

| Write Latency         | <10 ns              | 10-60 ns           | 9.5 ms               | 200 µs             |

| Energy per bit access | >1 pJ               | 2 рЈ               | 100-1000 mJ          | 10 nJ              |

| Static Power          | Yes                 | Yes                | Yes                  | No                 |

| Endurance             | >1015               | >1015              | >1015                | 10 <sup>4</sup>    |

| Non-volatility        | No                  | No                 | Yes                  | Yes                |

Table 2.1: Comparison of current memory/storage technologies: SRAM, DRAM, disk and NAND flash. Cell size uses standard feature size ( $F^2$ )

subsystems design is now and has been for several years the *only* important design issue for microprocessors and systems. Memory-hierarchy parameters affect system performance *significantly* more than processor parameters (e.g., they are responsible for 2-10x changes in execution time, as opposed to 2-10%)"

The high level of sophistication attained by modern memory systems is largely derived from the process predicted by Gordon Moore in 1965 [47], known as Moore's Law. It states that the number of devices that can be integrated on a chip of fixed area would double every 12 months (later amended to doubling every 18–24 months). Moore's law was the driving force behind dramatic reductions in unit cost for memory, enabling products of higher density and putting huge amounts of memory in the hands of the consumer at much reduced cost. This behavior has made the prediction of near-future product developments extremely reliable because the underlying device physics, materials, and fabrication processes have all been scalable, at least until now [13]. Figure 2.1 summarizes the main characteristics of current memory/storage technologies.

An important issue for the near future concerns DRAM approaching physical limits that might limit its growth in the next decade, creating a "power wall". DRAM must not only place charge in a storage capacitor but must also mitigate sub-threshold charge leakage through the access device. Capacitors must be suficiently large to store charge for reliable sensing and transistors must be suficiently large to exert effective control over the channel. Given these challenges, manufacturable solutions for scaling DRAM far beyond current limits is a challenge [36]. This fuels a concern with the growing power demands of DRAM:

"For several decades, DRAM has been the building block of the main memories of computer systems. However, with the increasing size of the memory system, a significant portion of the total system power and the total system cost is spent in the memory system. For example, (...) as much as 40% of the total system energy is consumed by the main memory subsystem in a mid-range IBM eServer machine." [53]

Disk density (and consequently capacity) is unlikely to face a similar scaling problem in the near future, but the latency gap between DRAM and disk is an issue that would be worth to solve. As Burr et al. put it,

"The best-case access time of a magnetic HDD has remained fairly constant over the past decade at approximately 3-5 milliseconds (...). A 3-GHz microprocessor will execute nine million instructions while waiting for this data. In fact, an enormous part of a modern computing system is designed expressly to hide or finesse this unpleasant discrepancy in performance." [13]

Flash also has its limitations as persistent storage:

"(...) the cost per gigabyte (GB) for flash memories is nearly 10x that of magnetic storage. Moreover, flash memories face significant scaling challenges due to their dependence upon reductions in lithographic resolution as well as fundamental physical limitations beyond the 22 nm process node, such as severe floating gate interference, lower coupling ratio, short channel effects, and low electron charge in the floating gate. Thus, to replace HDDs, alternative NVM technologies that can overcome the shortcomings of NAND flash memories and compete on a cost per TB basis with HDDs must be found." [34]

...and as main memory:

"NAND flash has very limited number of write/erase cycles:  $10^5$  rewrites as opposed to  $10^{16}$  for DRAM. NAND flash also requires a block to be erased before writing into that block, which introduces considerably extra delay and energy. Moreover, NAND flash is not byte-addressable." [79]

In a 2007 article, Barroso and Hölzle [6] proposed the notion of **energy-proportional** computing and maintained that it should be a primary design goal for computer design. They argue that datacenters are designed to keep server workload between 10-50% of their maximum utilization levels. This is done to ensure that throughput and latency service-level agreements will be met and that there will be room for handling component failures and planned maintenance. The problem is that the region under 50% utilization is the lowest energy-efficient region of servers, due to static power consumption (depicted in Figure 2.8a). As seen, memory/storage components consume both dynamic power (used to change memory contents) and static power (used for data retention and component availability). Static power used by SRAM and DRAM is used mostly for refreshes due to power leakage; in disks, most static power is used to keep the disk spinning and ready to answer requests with low latencies. As Barroso and Hölzle put it, "essentially, even an energy-efficient server still consumes about half of its full power when doing virtually no work" [6]. This problem is aggravated by the fact that the costs are not reflected only in the server electricity bill, but also in energy for cooling the datacenter and infrastructure provisioning costs, that increase proportionally to the server energy budget.

The authors of the article also mention that CPUs are the components that exhibit most energyproportional behavior today, and that the components that most contribute to less server energy efficiency are, in this order, DRAM (50%), disk drives (25%) and networking switches (15%). A

Figure 2.8: Relationship between power and energy-efficiency for a) current server behavior; b) theoretical energy-proportional server behavior. Reproduced from Barroso and Hölzle 2007 [6].

machine with a dynamic power range of 90% could cut by one-half the energy used in datacenter operations, due to its better energy efficiency in low-utilization regions, shown in figure 2.8b [6].

Due to all these limitations, there is intense research to create new alternatives of memory technology that can address these problems and prevent a "power wall" from being reached. In chapter 4 some of the most promising emerging technologies are presented. The next chapter describes how current technologies are applied in today's memory system organization.

# 3. MEMORY SYSTEM ORGANIZATION

The previous chapter presented the main technologies used today for memory and storage. This chapter describes how these technologies are employed in today's memory system organization. This is an important topic to understand, since the emerging technologies presented in chapter 4 will also potentially impact memory system design and organization.

# 3.1 Overview

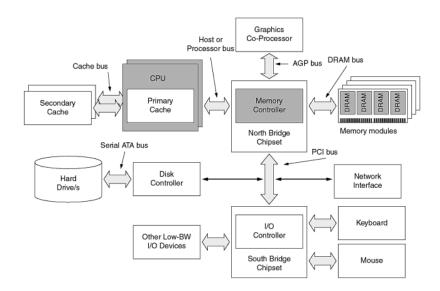

A typical PC organization is displayed in Figure 3.1, illustrating a two-way multiprocessor. This system has the most common characteristics usually found in modern computers, and will be used as a reference during the rest of this section.

Figure 3.1: A typical PC organization, showing a two-way multiprocessor, with each processor having its own secondary cache. Extracted from [31].

Each of the two **CPUs** (Central Processing Units) has its own on-chip primary cache, also known as **L1 cache**. In addition, each CPU also has access to an off-chip secondary cache (**L2 cache**) using a dedicated cache bus. Access to **main memory** is made through the **memory controller** residing inside the **north-bridge** chipset. The north-bridge mediates the communication between the processors and the DRAM **memory modules** through a DRAM bus. It also mediates communication with the **graphics co-processor** through an AGP bus and I/O devices (such as the **disk controller** and **network interfaces**) through a PCI bus. The north-bridge also is connected to the **south-bridge** chipset, which has an I/O controller responsible for communicating with **low bandwidth I/O devices** such as keyboard, mouse, etc. The disk controller communicates with **disks** through a Serial ATA (SATA) bus.

In the next section we will examine in more depth the main components of the memory system: caches, main memory and disks.

# 3.2 Cache

Processor **caches** enhance overall system performance providing very fast access to small subsets of memory data, expected to be accessed much more frequently than others. This is effective due to a phenomenon known as **locality of reference**, so named because memory references tend to be localized in time and space. This can be so summarized:

- If you use something once, you are likely to use it again (temporal locality);

- If you use something once, you are likely to use its neighbor (spatial locality).

Usually a processor cache is divided in three distinct areas: a **data** cache, an **instruction** cache and a **Translation Lookaside Buffer (TLB)**, used to speed up virtual-to-physical address translation for both executable instructions and data. They usually are **transparent caches**, meaning that the same addressing space is shared between the cache and the backing storage.

The data cache stores chunks of data that come from main memory, called **cache blocks** or **cache lines**. Each cache line contains:

- a cache tag indicating the index of the cached data in main memory

- the **status** of the cache line, indicating if its data are **clean** (consistent with the value stored in main memory) or **dirty** (recently written in cache but not in main memory)

- the cache data.

When the processor asks for the contents of a specific memory address, these contents are first searched in the cache. If they are found (a **cache hit**), they are immediately returned. If they are not found (a **cache miss**), the memory system goes on to the next hierarchy level (main memory) and fetches the result. The proportion of accesses that result in a cache hit is known as the **hit rate**. The time needed to discover whether a datum is cached or not is called the **hit time**.

Cache blocks can be grouped in **sets** of memory locations, and the number of blocks per set is called **cache associativity**. Associativity is a trade-off. If there are x places to which the replacement policy could have mapped a memory location, then to check if that location is in the cache, x entries must be searched. Checking more places takes more power, chip area, and potentially time. On the other hand, caches with more associativity suffer fewer misses, so that the CPU wastes less time reading from the slow main memory. The following associativity schemes exist:

Direct-mapped - each set contains only one cache block. It has the best hit times but the worst hit rates.

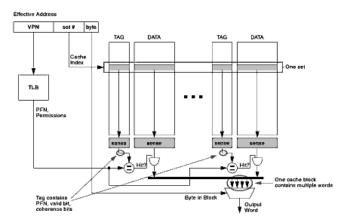

Figure 3.2: Organization of a Static RAM (SRAM) processor cache using set-associative mapping. Extracted from [31].

- **Fully-associative mapping** there is a single set for all lines, i.e., any line can store the contents of any memory location. This option has the best hit rates but the worst hit times.

- Set-associative mapping this is a compromise between the direct-mapped and fullyassociative approaches. Each set contains *n* check blocks, usually 2, 4 or 8.

Figure 3.2 shows the organization of a Static RAM (SRAM) processor cache using set-associative mapping.

In order to be efficient, caches must store memory locations that are frequently used. The responsibility to decide what will be stored in the cache and what will not is called **cache content-management**. Several distinct content-management heuristics exist; one of the most known is Least Recent Usage (LRU), that keeps in the cache data most frequently used in the past.

Caches also need **consistency-management**, to ensure that the overall memory space, as viewed by different processors and levels of the hierarchy, is consistent. This comprises three main charges:

- Keep the cache consistent with itself ensure that a specific memory address has the same value in the cache. This can be done by keeping just one copy of a given address or use some coherency mechanism to update all copies of the same address whenever a change happens.

- 2. Keep the cache consistent with the backing store make sure that all values changed in the cache get persisted in the backing store. Two policies can be employed: write-through, where all changes in the cache are immediately applied to the backing store, and write-back, where changes are applied initially only to the cache, and are written to the backing store at some future point in time, usually when there is a block replacement.

Figure 3.3: Basic organization of DRAM internals. Extracted from [31].

3. Keep the cache consistent with other caches - this is similar to the first charge, but applies to different caches and cache levels. It is also handled in a similar way.

# 3.3 Main Memory

The description below, except when indicated, was obtained from [31].

A **memory module** is typically connected indirectly to a CPU through a **memory controller**. In PC systems, the memory controller is part of the **north-bridge** chipset.

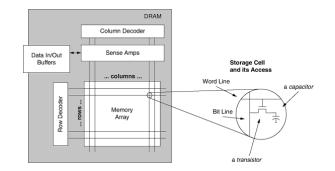

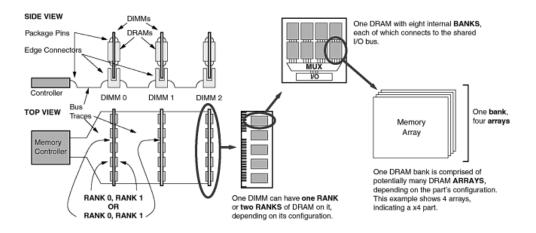

**Memory cells** are disposed on a grid called a **memory array**. Each cell stores a bit in the intersection of a row and a column. Figure 3.3 shows a DRAM array. A set of memory arrays that operate together are grouped in memory **banks**. The number of arrays in a bank determines the **data width** of the memory device (e.g., 4 arrays indicate a *x*4 data width). Data widths range from x2, x4 and x8 up to wider outputs of x16 and x32.

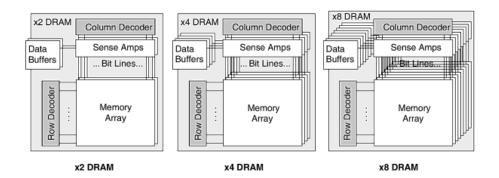

A **memory chip**, as represented in Figure 3.4, may contain several banks. Each memory chip contains a **row decoder** and a **column decoder** which are used to select a particular bit of each memory array. For each array there is a differential **sense amplifier** that senses the electrical properties of the cell (e.g., voltage, charge) and converts it to a digital value (0 or 1). The output of the sense amplifier is stored in a data buffer before it can be sent over the bus to the memory controller.

Figure 3.4: Logical organization of wide-out DRAMs. Extracted from [31].

The most common form factor for memory modules is called **DIMM** (dual-inline memory module), where multiple memory chips are placed in a single PCB (printed circuit board) with one or two **ranks** of memory chips, each one in one side of the PCB. At the bottom of the DIMM there are sets of **pins** used to communicate with the **memory bus**. A system can usually support several DIMMs, and all of them are connected to the memory controller by a common memory bus. Figure 3.5 displays the relationship between memory arrays, banks, ranks, DIMMs and the memory controller in a DRAM-based system.

Figure 3.5: DIMMs, ranks, banks and arrays in a DRAM system. Extracted from [31].

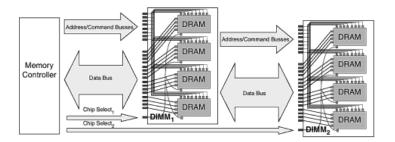

DRAM memory modules today are a commodity; any DRAM DIMM should be equivalent to any other with similar specifications (width, capacity, speed, interface, etc.). The organization that defines standards for DRAM memory modules is the **JEDEC** (Joint Electron Device Engineering Council). The most common memory modules today follow the JEDEC standard for **DDR** (Double Data Rate) **SDRAM** (Synchronous DRAM). This standard mandates the memory bus to be split in 4 separate busses, each one with their own traces:

- Data moves data words between the memory modules and the memory controller;

- Address specifies the address to be read/written from/to the memory module;

- Control sends commands from the memory controller to the memory module;

- Chip-Select selects which memory module a command is being directed to.

Figure 3.6 shows a JEDEC-style memory bus organization. Each set of traces connecting a memory controller to memory modules is called a **channel**. A memory controller can connect to modules through one or more channels. Organizations with more channels provide more parallelism at the expense of higher cost and complexity. Organizations with less channels are simpler and less expensive, but can be a bottleneck for communication between the memory controller and the memory modules. Synchronous DRAM (SDRAM) is so called because it uses the system clock to control timing in the memory busses, exchanging data between a memory controller and a memory module

in every system clock **tick**. Double Data Rate (DDR) SDRAMs are so named use a dual-edged clock, transmitting data in both the rising and the falling edge of a clock tick. So for every clock tick there is a memory bus **beat**.

The memory controller is responsible for receiving memory read/write requests from CPUs. These memory transactions are persisted in one or more **queues** inside the memory controller before being sent to the memory modules, and can be reordered by the memory controller to increase overall efficiency. One common reordering strategy is **write caching**: read requests are typically critical in terms of latency, but write requests are not; for this reason, read requests are usually prioritized over write requests, as long as the functional correctness of programs is not violated.

Another main responsibility of the memory controller is translating the addressing scheme used by the CPU (**physical address**) to the actual row/column address in a DRAM bank (**DRAM address**). There are usually three distinct levels of memory addressing in a typical PC:

- Virtual Addresses used by software applications and managed by the operating system, and potentially larger than the physical memory available;

- Physical Addresses a continuous representation of the physical memory available this is how the CPU addresses memory. The mapping from virtual to physical addresses is made by the Operating System with help from the Translation Lookaside Buffer (TLB) contained in the processor L1 cache;

- DRAM Addresses the actual location of memory data in the memory modules, including channel, rank, bank, row and column. The expansible nature of JEDEC-style memory makes it possible for memory modules to be added/subtracted from the system. Since the memory controller manages the current physical organization of memory modules, it is responsible for the translation between physical addresses and DRAM addresses.

The memory controller is also responsible for **refresh management** of DRAM memories. DRAM cells must be frequently refreshed due to capacitor power leakage. Memory controllers usually send periodical refresh commands to the memory modules to avoid losing memory contents.

Figure 3.6: JEDEC-style memory bus organization, consisting of a memory controller and two memory modules with a 16-bit data bus and an 8-bit address and command bus. Extracted from [31].

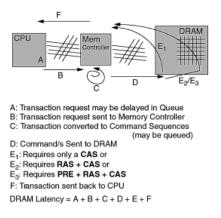

In order to do a memory read transaction, the following steps are typically followed:

- 1. A CPU requests a memory read transaction to a memory controller.

- 2. The memory controller converts the transaction in to a sequence of memory commands (translating the physical address to a DRAM address) and queues them.

- 3. When the command is unqueued, the memory controller sends to the appropriate memory module a **Precharge** (**PRE**) command. This sets the bitlines to a voltage level halfway between 0 and 1, which is needed for the sense amplifier to detect the value in each capacitor of a row.

- The memory controller sends to the memory module a Row Address Strobe (RAS) command, which causes the contents of an entire row to be activated and placed at the sense amplifier.

- 5. The memory controller sends to the memory module a **Column Address Strobe** (**CAS**) command, which specifies which specific column from the row currently at the sense amplifier should be moved to the data bus where it can be transferred to the memory controller.

- 6. Most of the current DRAM implementations don't transfer just a single column, but a predefined number of sequential columns. It saves bandwidth avoiding the need for the memory controller to send several of CAS commands to fetch the value of a series of contiguous columns. This is called a **burst**, and is a form of prefetching based on locality principles. Memory modules can have a **Programmable Burst Length** set by the memory controller.

- 7. The memory controller sends back to the CPU the memory contents of the requested physical address.

It is important to notice that some memory controllers reset the contents of the sense amplifier after a CAS command, making it faster to read contents from a different row. This is called an **open-page row-buffer-management policy**, and it is used more frequently in systems with more processors and less temporal and spatial locality. Other memory controllers keep the sense amplifier open after a CAS command, saving time and bandwidth if a new CAS command is issued against the same row. This is called a **closed-page row-buffer-management policy**, and it is used in systems with less processors and more temporal and spatial locality.

In open-page memory systems, when reading new column in a row already open, steps 3 and 4 (described above) are not needed. In both open-page and closed-page systems step 3 is not needed if the memory bank is already precharged. A summary of these steps can be seen at Figure 3.7.

### 3.4 I/O

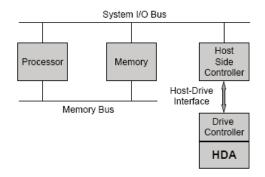

The I/O subsystem is responsible for communicating with persistent storage devices, including disk drives and/or flash memory. As previously mentioned in section 3.1, this interaction occurs via

Figure 3.7: Steps of a DRAM read. Extracted from [31].

the south-bridge chipset. Most of the communication essentially involves reading from or writing to these devices through I/O commands. The most typical I/O commands have this basic structure:

- 1. Whether the command is a read or write operation;

- 2. The starting address for the command;

- 3. the number of sectors of data to be read or written.

The communication channel over which I/O requests are from the processor to the storage devices and through which data transfers for reading/writing happen is called the **storage interface**. A basic model for attaching an storage device to a computer system (also called "host") is depicted in Figure 3.8. The **I/O bus** has a higher latency compared to the memory bus. The **host side controller** may have different names, depending on the system and interface (Host Bus Adapter, Storage Controller, Disk Drive Adapter, etc.), but is always responsible for interfacing the host communication with the storage devices. Each storage device (drive) has its own **drive controller**, that directly controls the storage media (either disk or flash).

The communication between the host side controller and the drive controller is made through a specific storage interface. Such interfaces usually are comprised of two layers: a **lower layer**, that defines cables, connectors, electrical or optical signals and other transport procedures; and a **higher layer**, that defines the protocol and set of commands that can be exchanged between the host and the drive. This separation of layers allows different interfaces to share the same higher or lower level layer. For instance, the ATA and SATA interfaces have the same higher layer, but the lower layer of the first is parallel (in the sense that multiple signals are sent in parallel over multiple wires), and the second is serial. The most usual interfaces in use today are the following:

- ATA one of the first standardized interfaces, is still very common for being a low-cost option. It is a parallel interface that allows up to 4 drives in a host controller.

- **SATA** as the name implies, Serial ATA is the serial version of the ATA interface. It has better performance than its parallel version.

Figure 3.8: Model of a storage device (disk drive) attached to a host system via an interface. Extracted from [31].

- **SCSI** the Small Computer Systems Interface is a more advanced interface with functionalities and features not available in ATA, and consequently higher cost. It is a parallel interface.

- **SAS** stands for Serial Attached SCSI, and essentially is a serial interface based on the SCSI protocol, for enhanced performance.

- **FC** Fibre Channel is a high-end, feature-rich, serial interface. It is the most complex and expensive of all, but presents far more performance and flexibility.

Caches play an important role in increasing storage device performance. Typically both the host side controller and the drive controller have built-in caches. Main memory is also used to buffer data read from storage devices, and can sometimes act as a cache, as the data being read is already available in DRAM. Since storage devices are more efficient manipulating sequential data, the drive cache is very important to amortize access time through prefetching mechanisms.

The next chapter will present the emerging non-volatile memory technologies being researched, and chapter 5 discusses the impacts of these emerging memory technologies concerning how they can contribute to create computers with **persistent main memory**.

# 4. EMERGING MEMORY TECHNOLOGIES

Chapter 2 presented the current technologies used in memory hierarchy, discussed their limitations and the arguments for the research of more efficient memory technologies. This chapter presents the emerging memory technologies that can be an answer to these issues.

There are several new Non-Volatile Memory (NVM) technologies under research. One study [34] lists 13 of such technologies: FRAM, MRAM, STTRAM, PCRAM, NRAM, RRAM, CBRAM, SEM, Polymer, Molecular, Racetrack, Holographic and Probe. Most these technologies are in different stages of maturity. Some of them are still in early research stages, others have working prototypes, and some of them are already entering into commercial manufacturing.

In the present work, we will limit our study to three of these technologies: Phase-Change RAM, Resistive RAM (including Memristors) and Magnetoresistive RAM (including Spin-Torque Transfer RAM). All these fall into the category of the most actively researched today, are backed by solid companies of the technology industry, and considered most promising of being commercially feasible.

For those who are interested in a more broad analysis of all different kinds of NVM under research, the works of Burr et al. [13], and Kryder and Kim [34] can be consulted.

### 4.1 Phase-Change RAM (PCRAM)

Phase-Change Random Access Memory (also called PCRAM, PRAM or PCM) is currently the most mature of the new memory technologies under research. It relies on some materials, called **phase-change materials**, that exist in two different phases with distinct properties:

- 1. An amorphous phase, characterized by high electrical resistivity;

- 2. A crystalline phase, characterized by low electrical resistivity [56].

These two phases can be repeatedly and rapidly cycled by applying heat to the material. To make it amorphous, it is melt-quenched using a high-power electrical pulse that is abruptly cut off. To crystallize the material, it is heated above its crystallization temperature using a moderate power pulse with a longer duration. Since the duration of this pulse varies according to the crystallization speed of the material being used, this operation tends to dictate the writing speed of PCRAM. Reflectivity can vary up to 30%, but resistivity changes can be as large as five orders of magnitude. [13, 56]

The principle of phase-change memory is known since the 1960s, but only recent discoveries of phase-change materials with faster crystallization speeds led to the possibility of commercially feasible memory technology. The most important materials are chalcogenides such as  $Ge_2Sb_2Te_5$  (GST), that can crystallize in less than 100 ns [56].

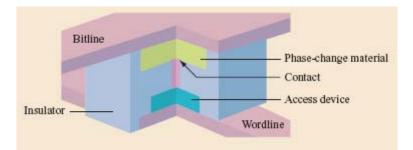

Figure 4.1: Example of a phase-change memory cell. The current is forced to pass through the phase-change material. Image obtained from [56].

Figure 4.1 shows a memory cell based on phase-change principles. The SET operation is achieved by crystallizing the material and RESET by making it amorphous. Unlike Flash memory, PCRAM can be switched from 0 to 1 and vice-versa without an ERASE operation.

Given the great difference in resistance, phase-change materials can be easily used to store binary states per cell (single-level cell) and even more states (multi-level cell) [13, 36].

PCRAM is argued to be a scalable technology. As the feature density increases, phase-change material layers become thinner and need less current for the programming operations. It has been demonstrated to work in 20nm device prototype and is projected to scale down to 9nm. DRAM presents challenges to scale down beyond 40nm [36, 56].

As previously mentioned, the SET latency is the longest and determines the write performance. Latencies of 150 ns for SET and 40 ns for RESET operations have been demonstrated. Write energy is determined by the RESET operation, which dissipates 480  $\mu W$ , while SET dissipates 90  $\mu W$ . The read latency is 48 ns and dissipates 40  $\mu W$ . Both read and write latencies are several times slower than DRAM, although only by tens of nanoseconds [36].

Endurance is bound to the number of writes. This happens because when current is injected into a phase-change material, thermal expansion and contraction degrade the contacts, so that currents are no more reliably injected into the cell. The current write endurance varies between  $10^4$  and  $10^9$  writes, but we can conservatively assume  $10^8$  as a reasonable reference value [36, 79].

Today PCRAM is positioned as a Flash replacement. It offers great advantages over Flash, but given the current limitations of access latency, energy consumption and endurance, further development is required in order to employ it as a replacement for DRAM [36, 37].

#### 4.2 Resistive RAM (RRAM)

Despite the fact that PCRAM also uses resistance variances to store bit values, the term **Resistive RAM** (RRAM) has been applied to a distinct set of technologies that explore the same phenomenon. Essentially these technologies fall into one of two categories [13]:

1. Insulator resistive memories: based on bipolar resistance switching properties of some metal oxides. The most important example is the memristor memory device, which will be further

Figure 4.2: Relationship between current and voltage in a memristor, known as a "hysteresis loop". Extracted from Wang, 2008 [71].

described in more detail.

Solid-electrolyte memories: based on solid-electrolyte containing mobile metal ions sandwiched between a cathode and an anode. Also known as Programmable Metallization Cell (PMC) or Conductive Bridge RAM (CBRAM).

There is a long list of RRAM technologies [11, 13, 34, 77]. In this paper we will concentrate our attention on the **memristor**, which is currently the most promising RRAM technology under research [77].

### 4.2.1 Memristor

Since the 19th century, we have known three fundamental passive circuit elements: the resistor, the inductor and the capacitor. In 1971, Leon Chua theorized the existence of a fourth passive circuit element, which he called the **memristor** [15], but no actual physical device with memristive properties could be constructed. In 2008, a group of scientists reported the invention of a device that behaved as predicted for a memristor [62]. Later the same year, an article detailed how that device could be used to create nonvolatile memories [77].

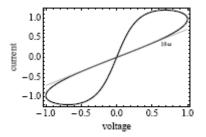

The property of memristors particularly relevant to memory devices is the nonlinear relationship between current (I) and voltage (V), depicted on Figure 4.2. In the words of R. Stanley Williams, the leader of the research team that invented the first memristor device:

"Memristor is a contraction of 'memory resistor', because that is exactly its function: to remember its history. A memristor is a two-terminal device whose resistance depends on the magnitude and polarity of the voltage applied to it and the length of time that voltage has been applied. When you turn off the voltage, the memristor remembers its most recent resistance until the next time you turn it on, whether that happens a day later or a year later. (...) The ability to indefinitely store resistance values means that a memristor can be used as a nonvolatile memory." [72]

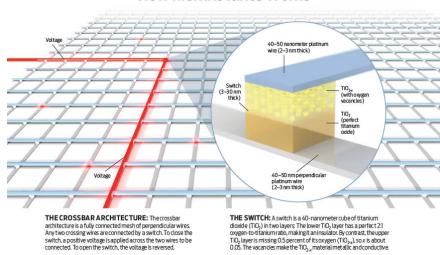

This memristor device consisted of a crossbar of platinum wires with titanium dioxide  $(TiO_2)$  switches, as shown in Figure 4.3. Each switch consists of a lower layer of perfect titanium dioxide

# How Memristance Works

Figure 4.3: How memristance works [72].

$(TiO_2)$ , which is electrically insulating, and an upper layer of oxygen-deficient titanium dioxide  $(TiO_{2-x})$ , which is conductive. The size of each layer can be changed by applying voltage to the top electrode. If a positive voltage is applied, the  $TiO_{2-x}$  layer thickness increases and the switch becomes conductive (ON state). A negative voltage has the opposite effect (OFF state). This behavior matches the hysteresis loop previously shown in Figure 4.2. [62, 72, 77].

Titanium dioxide was used in the mentioned prototype, but several other oxides are known to present similar bipolar resistive switching, and there are multiple research projects in motion to explore these other materials for similar memory device implementations [11, 13].

Memristive memory technology is less mature than PCRAM, and DIMM prototypes aren't available yet, but there are already a few papers that predict some fundamental characteristics of such memories [29, 38].

Scalability is one aspect where memristor is most efficient. A cell density of 10 nm has been achieved and a density between 4-5 nm is predicted for the next few years [38, 72]. Beyond that, memristor memory devices can benefit from multi-level cell (MLC) storage and 3D die stacking, which can greatly improve the overall density [11, 29, 38, 72].

We haven't found any report of actual read speeds, but they are expected to be faster than DRAM speeds, which are around 10 ns. The write speed is 10 ns for a single cell; not as fast as DRAM, which can do round-trip writes (including bus latency, addressing, transaction and data return) in the same time [38].

The switching power consumption of memristor can be 20 times smaller than flash [29].

Another property of memristors is that they are made from common semiconductors that are CMOS-compatible, and can easily be produced in existing semiconductor factories [13, 72].

The Achilles heel of memristor is endurance. The existing memristor prototypes have shown so far an endurance of  $10^5$  write cycles, and main memory devices need an endurance in the order of

Table 4.1: Comparison between DRAM and RRAM (Memristor) metrics. Extracted from Lewis and Lee [38].

| Metric                         | DRAM              | RRAM                         | Advantage |

|--------------------------------|-------------------|------------------------------|-----------|

| Capacity (GB/cm <sup>2</sup> ) | 46                | 466                          | RRAM      |

| Area Efficiency                | Less              | More                         | RRAM      |

| Write Speed (ns)               | 10, round trip    | 10, just one cell            | DRAM      |

| Read Speed (ns)                | 10, round trip    | Uncertain, likely better     | RRAM      |

| Yield                          | 90%               | 80-95%                       | tie       |

| Retention Time                 | 16ms              | ¿ 2yr                        | RRAM      |

| Readability                    | 10-1              | 10 <sup>5</sup>              | RRAM      |

| Endurance                      | 21010 write cyles | 10 <sup>5</sup> write cycles | DRAM      |

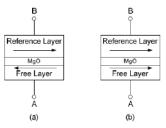

Figure 4.4: A conceptual view of MTJ structure. (a) Anti-parallel (high resistance), which indicates "1" state; (b) Parallel (low resistance), which indicates "0" state. Reproduced from Dong, 2008 [24].