## ESCOLA POLITÉCNICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO DOUTORADO EM CIÊNCIA DA COMPUTAÇÃO

## MARCOS LUIGGI LEMOS SARTORI

# CURBING THE DESIGN COMPLEXITY OF ASYNCHRONOUS CIRCUITS

Porto Alegre 2023

### PÓS-GRADUAÇÃO - STRICTO SENSU

Pontifícia Universidade Católica do Rio Grande do Sul

# CURBING THE DESIGN COMPLEXITY OF ASYNCHRONOUS CIRCUITS

## MARCOS LUIGGI LEMOS SARTORI

Doctoral Thesis submitted to the Pontifical Catholic University of Rio Grande do Sul in partial fulfillment of the requirements for the degree of Ph. D. in Computer Science.

Advisor: Prof. Fernando Gehm Moraes

| \$251c | Sartori, Marcos Luiggi Lemos                                                                                                                                                                 |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | Curbing the Design Complexity of Asynchronous Circuits / Marcos<br>Luiggi Lemos Sartori. – 2023.<br>139.<br>Tese (Doutorado) – Programa de Pós-Graduação em Ciência da<br>Computação, PUCRS. |

|        | Orientador: Prof. Dr. Fernando Gehm Moraes.                                                                                                                                                  |

|        | 1. Asynchronous circuits. 2. EDA. 3. Self-timed. 4. QDI. I. Moraes,<br>Fernando Gehm. II. Título.                                                                                            |

Elaborada pelo Sistema de Geração Automática de Ficha Catalográfica da PUCRS com os dados fornecidos pelo(a) autor(a). Bibliotecária responsável: Clarissa Jesinska Selbach CRB-10/2051

#### MARCOS LUIGGI LEMOS SARTORI

# CURBING THE DESIGN COMPLEXITY OF ASYNCHRONOUS CIRCUITS

This Doctoral Thesis has been submitted in partial fulfillment of the requirements for the degree of Ph. D. in Computer Science, of the Computer Science Graduate Program, School of Technology of the Pontifical Catholic University of Rio Grande do Sul

Sanctioned on 5<sup>th</sup> September, 2023.

# **COMMITTEE MEMBERS:**

Milos Krstic (Universität Potsdam/IHP)

Renato Peres Ribas (PGMICRO/UFRGS)

Prof. César Augusto Missio Marcon (PPGCC/PUCRS)

Prof. Fernando Gehm Moraes (PPGCC/PUCRS - Advisor)

To all humankind,

"The acquisition of wealth is no longer the driving force of our lives. We work to better ourselves and the rest of humanity." (Jean-Luc Picard)

#### AGRADECIMENTOS

Meus mestres, amigos, família e companheiros, com carinho.

This study was financed in part by the Coordenação de Aperfeiçoamento de Pessoal de Nível Superior – Brasil (CAPES) – Finance Codes: 88887.498562/2020-00, 88887.658570/2021-00 and 88887.683231/2022-00.

This thesis was partially supported by the Ministry of Science, Technology, and Innovations, with resources from Law No. 8.248, dated 23 October 1991, within the scope of PPI-SOFTEX, coordinated by Softex.

# REDUZINDO A COMPLEXIDADE DE PROJETO DE CIRCUITOS ASSINCRONOS

#### RESUMO

O projeto de circuitos assíncronos auto-temporizados (ST) oferece robustez a variações de atraso, mas enfrenta desafios que exigem soluções inovadoras. Esta Tese aprimora de forma abrangente o Pulsar, uma contribuição anterior do Autor, focada no projeto de circuitos assíncronos com ferramentas comerciais de automação de projeto eletrônico. Pulsar originalmente endereçava tão-somente o modelo pseudo-síncrono ST de lógica de convenção nula usando espaçadores duplos espacialmente distribuídos (em inglês, pseudosynchronous distributed dual spacer null convention logic or PS-SDDS-NCL). A Tese propõe dois novos modelos ST e estende Pulsar para dar suporte a estes.

O primeiro modelo denomina-se espaçador duplo de indicação fraca (em inglês, weak-indicating dual spacer ou WInDS), um aprimoramento de indicação fraca para o modelo PS-SDDS-NCL. O segundo é o modelo ST organização assíncrona com histerese limitada (em inglês, asynchronous limited hysteresis organisation ou ALHO), que emprega sobretudo portas lógicas convencionais não-histeréticas. Estes modelos são propostos e integrados na estrutura Pulsar. Eles abordam alguns dos desafios na implementação de circuitos ST, refletindo a motivação da Tese para superar obstáculos no projeto de circuitos assíncronos e, ao mesmo tempo, lidar com excessivos área, potência e desempenho algumas vezes produzidos por circuitos ST. Ao estender a ferramenta Pulsar, a Tese propõe melhorias para apoiar ações de escolha, oferecendo maior flexibilidade ao projeto, e demonstra o uso de Pulsar para elaborar circuitos simples, bem como e uma implementação funcional completa de uma versão da arquitetura RISC-V de processador programável com os modelos introduzidos.

Contribuições adicionais são a proposta de uma classificação alternativa para circuitos assíncronos, partindo da necessidade de diferenciar circuitos Quasi-Delay-Insensitive (QDI) de circuitos ST apartir dos seus pressupostos de temporização. A Tese também formaliza os requisitos para construir circuitos ST funcionais, propondo princípios fundamentais para o projeto e implementação eficientes destes. As contribuições fornecem uma abordagem estruturada para projetar circuitos assíncronos, com foco no modelo ST ALHO e na extensão do Pulsar para lhe dar suporte. O trabalho traz uma base para a exploração, pesquisa e desenvolvimento continuados no campo de projeto de circuitos assíncronos, empregando a ferramenta Pulsar e oferecendo novas perspectivas para o processamento deste paradigma.

Palavras-Chave: Circuitos Assíncronos, ST, QDI, Automação de projeto eletrônico.

## **CURBING THE DESIGN COMPLEXITY OF ASYNCHRONOUS CIRCUITS**

### ABSTRACT

The design of self-timed (ST) asynchronous circuits offers robustness to delay variations but faces challenges that require innovative solutions. This Thesis comprehensively enhances Pulsar, a previous contribution of the Author, focused on designing asynchronous circuits with the help of commercial electronic design automation tools. Pulsar originally targeted the pseudo-synchronous spatially distributed dual spacer null convention logic (PS-SDDS-NCL) ST template. The Thesis introduces two new asynchronous ST templates and extends Pulsar to support these.

The first is the weakly-indicating dual spacer (WInDS), a weakly-indicating enhancement to PS-SDDS-NCL. The second is the asynchronous limited hysteresis organisation (ALHO) ST template, which employs non-hysteretic gates. These are proposed and integrated within the Pulsar framework. They address some challenges in ST circuit implementation, reflecting the Thesis motivation to overcome hurdles in designing asynchronous circuits whilst tackling area, power and performance overheads. This Thesis also extends Pulsar to support choice, offering more design flexibility. It demonstrates the use of Pulsar to design simple circuits and a fully functional RISC-V processor architecture implementation with the introduced templates.

Additional contributions include the formalisation of requirements to build functional ST circuits, providing foundational principles for their effective design and implementation. This formalisation enabled the construction of more relaxed ST circuits compared to the conservative quasi-delay-insensitive (QDI) paradigm. The need to differentiate QDI and more relaxed ST circuits in terms of timing assumptions resulted in the proposal of a classification system for asynchronous circuits.

These contributions collectively provide a new structured approach to asynchronous circuit design, culminating in the non-hysteretic ALHO ST template and the extensions of Pulsar. The work lays a foundation for the continued exploration, research, and development in the field of asynchronous circuit design, building on the capabilities of Pulsar and offering new insights into the design process of ST circuits.

Keywords: Asynchronous Circuits, ST, QDI, Electronic design automation.

## LIST OF ACRONYMS

- ALHO Asynchronous Limited Hysteresis Organisation

- ASCEND Asynchronous Standard Cells Enabling n-Designs

- ASIC Application-Specific Integrated Circuits

BD - Bundled-data

- DI Delay-Insensitive

- EDA Electronic Design Automation

- DCDT Digital Circuit Design Template

- FBCN Full-buffer Channel Network

- HBCN Half-buffer Channel Network

- IC Integrated Circuit

- MG Marked Graph

- NCL Null Convention Logic

- PDMG Place-Delayed Marked Graph

- PN Petri Net

- PS Pseudo-Synchronous

- PVT Process, Voltage and Temperature

- PS-SDDS-NCL Pseudo-Synchronous Spatially Distributed Dual Spacer Null Convention Logic

- QDI Quasi Delay-Insensitive

- RTL Register Transfer Level

- SDDS Spatially Distributed Dual Spacer

- $\mathsf{ST}-\mathsf{Self}\text{-}\mathsf{Timed}$

- STA Static Timing Analysis

- WCHB Weak Conditioning Half Buffer

- WINDS Weakly-Indicating Dual Spacer

# CONTENTS

| 1     |                                                 | 11 |

|-------|-------------------------------------------------|----|

| 1.1   | ASYNCHRONOUS CIRCUITS AS AN ALTERNATIVE         | 12 |

| 1.2   | CHALLENGES TO ST ADOPTION                       | 13 |

| 1.3   | THESIS CONTRIBUTIONS                            | 14 |

| 1.4   | STRUCTURE OF THE THESIS TEXT                    | 16 |

| 2     | DEFINITIONS                                     | 17 |

| 2.1   | BOOLEAN EXPRESSION AND FUNCTIONS                | 17 |

| 2.1.1 | PROPERTIES OF BOOLEAN EXPRESSIONS AND FUNCTIONS | 19 |

| 2.2   | GATES, NETLISTS AND PRODUCTION RULES            | 22 |

| 2.2.1 | LOGIC GATES PROPERTIES                          | 25 |

| 2.3   | GRAPHS AND PETRI NETS                           | 27 |

| 2.3.1 | PETRI NETS                                      | 27 |

| 2.3.2 | PETRI NET PROPERTIES                            | 29 |

| 2.3.3 | MARKED GRAPHS                                   | 30 |

| 3     | ASYNCHRONOUS CIRCUIT DESIGN                     | 32 |

| 3.1   | PRINCIPLES OF ASYNCHRONOUS DESIGN               | 35 |

| 3.2   | ASYNCHRONOUS SELF-TIMED DESIGN                  | 37 |

| 3.2.1 | GATE AND WIRE ORPHANS                           | 41 |

| 3.3   | CLASSIFICATION OF ASYNCHRONOUS CIRCUITS         | 43 |

| 3.4   | SELF-TIMED SEQUENTIAL CIRCUITS                  | 44 |

| 3.5   | SELF-TIMED COMBINATIONAL LOGIC                  | 46 |

| 3.6   | NCL: A MORE EFFICIENT HYSTERETIC GATE           | 48 |

| 3.7   | SDDS-NCL: SPATIALLY DISTRIBUTED DUAL SPACER NCL | 51 |

| 3.8   | A CRITIQUE OF SDDS-NCL                          | 53 |

| 4     |                                                 | 56 |

| 4.1   | PSEUDO SYNCHRONOUS WCHB                         | 56 |

| 4.2   | THE HALF-BUFFER CHANNEL NETWORK                 | 58 |

| 4.3   | TIMING ANALYSIS                                 | 61 |

| 4.4   | CYCLE TIME CONSTRAINING                         | 63 |

| 4.4.1 | PROPORTIONAL CYCLE TIME CONSTRAINTS             | 64 |

| 5                                               | PULSAR AND ITS TEMPLATES                                          | 67                                                                                      |

|-------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 5.1                                             | DESIGN CAPTURE                                                    | 68                                                                                      |

| 5.2                                             | VIRTUAL NETLIST AND COMPONENTS                                    | 73                                                                                      |

| 5.2.1                                           | A CASE STUDY                                                      | 75                                                                                      |

| 5.2.2                                           | SEQUENTIAL COMPONENTS                                             | 77                                                                                      |

| 5.2.3                                           | THE DECISION-MAKING COMPONENTS                                    | 81                                                                                      |

| 5.2.4                                           | THE TOKEN STEERING COMPONENTS                                     | 83                                                                                      |

| 5.3                                             | PS-SDDS-NCL - THE PSEUDO-SYNCHRONOUS SDDS-NCL TEMPLATE            | 85                                                                                      |

| 5.4                                             | WINDS - THE WEAKLY INDICATING DUAL SPACER LOGIC TEMPLATE $\ldots$ | 88                                                                                      |

| 5.5                                             | ALHO - THE ASYNCHRONOUS LIMITED HYSTERESIS ORGANISATION TEM-      |                                                                                         |

|                                                 | PLATE                                                             | 92                                                                                      |

|                                                 |                                                                   |                                                                                         |

| 6                                               | EXPERIMENTAL RESULTS AND CONCLUSION                               | 99                                                                                      |

| -                                               | EXPERIMENTAL RESULTS AND CONCLUSION                               |                                                                                         |

| 6.1                                             |                                                                   | 99                                                                                      |

| 6.1<br>6.1.1                                    | EXPERIMENTAL SETUP                                                | 99                                                                                      |

| 6.1<br>6.1.1                                    | EXPERIMENTAL SETUP                                                | 99<br>100                                                                               |

| 6.1<br>6.1.1<br>6.1.2                           | EXPERIMENTAL SETUP                                                | 99<br>100<br>101                                                                        |

| <b>6</b><br>6.1<br>6.1.1<br>6.1.2<br>6.2<br>6.3 | EXPERIMENTAL SETUP<br>LOW COMPLEXITY BENCHMARKS                   | 99<br>100<br>101<br>104                                                                 |

| 6.1<br>6.1.1<br>6.1.2<br>6.2                    | EXPERIMENTAL SETUP<br>LOW COMPLEXITY BENCHMARKS                   | 99<br>100<br>101<br>104<br>116                                                          |

| 6.1<br>6.1.1<br>6.1.2<br>6.2                    | EXPERIMENTAL SETUP<br>LOW COMPLEXITY BENCHMARKS                   | <ul> <li>99</li> <li>100</li> <li>101</li> <li>104</li> <li>116</li> <li>118</li> </ul> |

### 1. INTRODUCTION AND MOTIVATION

Advances in semiconductor fabrication technologies allow higher integration, energy savings and better performance but impose design challenges. Some of the challenges faced in newer technologies are: (i) higher sensitivity to process variations; (ii) higher static power; and (iii) longer wire delays. Process variations result from imperfections in the fabrication process and manifest themselves as changes in the circuit's electrical properties. Static power is the power dissipated by the circuit when idle that is when no switching activity is taking place. Higher static power can be attributed to higher leakage current due, e.g. to thinner oxide layers between the transistor channel and the transistor gate. It is roughly proportional to the number of transistors in the die, each contributing to the overall leakage power. Larger wire delays are attributable to smaller wire cross sections and relatively longer wire lengths, which cause reduced wire current capacity, higher parasitic capacitance and (relatively) increased coupling effects with neighbour wires. Wire delays in recent technologies make it unfeasible to route global signals in large circuits without using buffers to "repeat" the signal during its propagation. This imposes challenges on synchronous circuits, as they employ a global "clock" signal to provide a discrete-time reference for synchronisation.

The clock signal distribution must present a controlled, ideally null *skew*, i.e. it must present sufficiently close (or at least predictable) delays from the clock source to all registers controlled by that clock signal. Meeting this clock distribution criterion requires a clock distribution network composed by buffers and other signal distribution components. This clock distribution network can have a high cost in area and power. The power consumption associated with the clock distribution can comprise a significant percentage of the overall power dissipated especially in complex circuits. It is not unusual for the clock distribution circuit to take 40% or more of the total integrated circuit (IC) power consumption [DMM04]. Also, as ideal clock distribution networks with no skew are challenging to achieve or even impossible to obtain, it becomes necessary to compensate for the skew. Due to timing uncertainties arising from process variation affecting the clock distribution delay predictability, it becomes important to introduce margins in the clock period. This, of course, impacts the overall circuit performance.

Modern designs mitigate these issues by dividing the circuit into clock domains and using synchronisers to transfer signals between clock domain boundaries; this approach only helps solve the problem locally. However, logic spread across a large area (e.g. interconnects) still suffers from clock distribution problems. Furthermore, using multiple clock domains can result in significant synchronisation overheads, as different clock domains have their specific clock distribution network, possibly operating at different phases. Traversing clock domains can become even more challenging when dealing with modern designs employing multiple operation frequencies and voltages. A possible solution is the overall elimination of global or semi-global clock signals. Digital circuits without any global or semi-global clock signals are known as *asynchronous circuits*.

#### 1.1 Asynchronous Circuits as an Alternative

Synchronous designs assume that the value on the inputs of all its registers will only be sampled at the rising (and/or falling) edge of the clock signal. This assumption enables designers to define timing constraints for the maximum delay in logic paths, which must always be lower than the clock period. This allows ignoring gate and wire delays, as long as timing constraints are respected. In other words, combinational logic is allowed to switch as it computes data during, say, the interval between two consecutive rising clock edges. Still, it must be stable and correct before the clock edge. Having such a simple model for circuit design is possible only because the clock is a periodic signal, *i.e.* its edges only occur at specific and known points in time. Hence, in synchronous circuits, events will only occur at specific moments; time can thus be treated as a discrete variable.

However, in asynchronous circuits, there is no such thing as a single clock to signal data validity on the inputs of all registers. In these, events can happen at any moment, and time must be regarded as a continuous variable. Thus, asynchronous designers rely on local handshake protocols for communication and synchronisation and on different design templates to build circuits, each with its own specific assumptions about gate and wire delays [BOF10]. These templates can be classified into two main families: bundleddata (BD) [Sut89] and Self-Timed (ST) [Mar90]. The design of a BD circuit is similar to a synchronous one; the difference is that BD relies on carefully designed delay elements for matching the timing of logic paths and controlling registers rather than having a clock signal. Communication and synchronisation are accomplished through handshake protocols. ST, on the other hand, uses special data encoding schemes and protocols that allow data to carry their own validity information. This enables data receivers to compute the presence or absence of complete data at its inputs/outputs and renders possible the local exchange of information. Because of this characteristic, ST circuits can adapt more gracefully to wire and gate delay variations. This is especially true for a subset of ST circuits, named quasi delay-insensitive (QDI), whose structure enables their correct operation with fewer timing assumptions, thus less sensibility to delay variability.

Common sources of delay variations are process, voltage and temperature (PVT) variations and ageing, all faced in recent sub-micron technologies. For example, intra-die process variations cause the same gate in different parts of the circuit to present different switching delays, which can possibly lead to faulty circuit behaviour and/or lower production yield. This problem affects interconnect circuits more acutely, as they span over a large sili-

con area. ST circuits are thus excellent candidates to tolerate the conditions imposed by intrinsic intra-die process variations. Circuits that use ST interconnects between synchronous components can take advantage of this aspect of ST circuits. Furthermore, the mixed-use of asynchronous circuits as interconnect for synchronous components solves some of the known synchronisation problems occurring in the frontier between clock domains.

#### 1.2 Challenges to ST Adoption

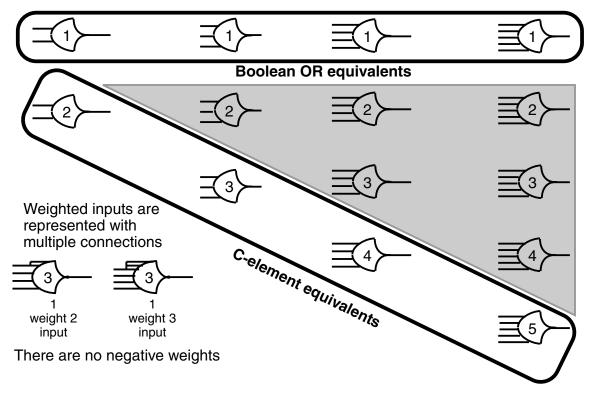

The design of ST circuits often relies on specialised infrastructures, which can frequently hinder the adoption of ST circuit design. This infrastructure often includes (i) specific gate libraries, containing, e.g. C-Elements, NCL [FB96] gates or PCHB logic cells; (ii) specific synthesis tools; and (iii) specific design capture languages. ST circuits normally require gates with hysteretic behaviour to facilitate or enable handshake synchronisation; a hysteretic gate holds the output stable until specific criteria are met. These special gates are not usually available in conventional cell libraries designed for synchronous semicustom application-specific IC (ASIC) flows, nor are they readily usable by commercial EDA tools. Specialised tools like Uncle [RST12] and Balsa [EB02] can be used to produce asynchronous circuits with these gates. However, these specialised tools do not integrate well with semi-custom ASIC flows; they also lack the power and flexibility provided by advanced commercial EDA tools.

Beyond the hysteretic gates' availability and compatibility with EDA tools, these specialised gates can be a hurdle themselves. They require additional logic to implement hysteresis; this makes them bulkier compared to non-hysteretic *conventional gates*. Their widespread use to implement random logic in templates like NCL or DIMS [Sin81] produces circuits with potentially huge area overheads; of course, this overhead potentially also impacts static power. Hysteretic gates also tend to be slower to switch as they often present a greater logic depth and higher capacitance. These drawbacks are aggravated on QDI circuits which, to reduce timing assumptions to only some wire forks, are *strong indicating*, meaning that every transition in every intermediary signal must be acknowledged by at least another transition. Strong indicating circuits often require additional circuitry compared to their weak indicating counterparts.

Another challenge in designing asynchronous circuits is satisfying non-functional requirements such as performance, power and area targets. These are often conflicting among themselves, and balancing them requires employing constraints to guide the synthesis effort. The circuit's throughput is often the primary performance metric; it dictates how fast the circuit can accept new input and/or produce results. On asynchronous circuits, the throughput is bounded by the circuit's maximum cycle time. However, on complex concurrent asynchronous systems, cycle time is not trivial to capture. Synchronous circuits typically rely

on register transfer level (RTL) models, where the maximum throughput is limited by a clock period. This not only makes design capture simpler but also eases the task of optimising a netlist, as every timing path has the same fixed maximum delay constraint, the clock period. Synchronous RTL models drove decades of development on commercial EDA tools, which provide solid means for designers to explore power, performance and area optimisation in modern technologies. These means are nonetheless very specific, and efforts to abandon the synchronous paradigm in exchange for more powerful design techniques can easily make commercial tools not applicable. Accordingly, the support for asynchronous design lags; as technologies get less predictable and wire-dominated, there is a particular need for new solutions that allow asynchronous circuit optimisation after technology mapping and during physical design.

The lack of mature tools also affects the timing closure of ST circuit designs. Albeit resilient to delay variation, ST circuits must observe some timing assumptions to operate correctly. This is true even for QDI circuits, which must observe the isochronic fork assumption [Mar90], i.e. the delay difference between end-points of a wire fork must be negligible compared to gate delays; this requirement can become too restrictive in modern technologies, dominated by wire delay. The isochronic fork requirement is eased by the concept of *orphan paths* [Fan05]; these are paths that are not acknowledged by an output transition under certain conditions. If an orphan path is slower than the fastest propagation of a spacer, malfunction may occur. Both orphans paths and the isochronic fork assumption are ways of addressing the same issue, which is required to achieve timing closure in ST designs. Due to the lack of proper tooling, the design timing closure process is often manually crafted by specialised designers. Also, ST circuits are often implemented in an overly conservative fashion to isolate such timing issues. The availability of more sophisticated timing checks and design closure automated techniques can enable a less restricted synthesis process for ST templates, thus allowing further optimisation, which is the main motivation for this Thesis.

#### 1.3 Thesis Contributions

Some of the perceived hurdles to ST adoption have already been addressed in previous works. For instance, SDDS-NCL [MBSC18] proposes a method to allow conventional EDA tools to correctly employ hysteretic gates in the synthesis of ST circuits. Later, in the context of his MSc dissertation [Sar19], the Author has extended SDDS-NCL and proposed Pulsar, an automated synthesis flow capable of synthesising ST circuits using Cadence Genus. Pulsar employs the Half-buffer Channel Network (HBCN) timing model, an original contribution by the Author, and the pseudo-synchronous WCHB model [TBV12] to leverage static timing analysis (STA) and timing-driven synthesis capabilities of commercial EDA to design ST circuits with bounded cycle time, guaranteeing a performance floor. Pul-

sar also offers a design capture method based on register transfer level (RTL) descriptions, a paradigm familiar to most synchronous designers, here called RTL-like. Ultimately, at the end of the Author's MSc, Pulsar enabled the synthesis of performance-bound ST circuits from RTL-like descriptions.

This Thesis builds on and furthers Pulsar to explore and advance the capabilities of commercial EDA tools in the synthesis of ST circuits. The technique designed to enable the use of STA provides greater control over the timing of ST circuits. This ultimately allowed the exploration of more relaxed templates to overcome some of the issues arising from the widespread use of hysteretic gates and strong indication. This process leads to the proposal of two new templates:

- Weakly-Indicating Dual Spacer (WInDS)

- Asynchronous Limited Hysteresis Organisation (ALHO)

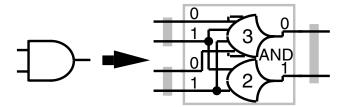

WInDS is an enhancement from SDDS-NCL, which replaces strongly-indicating combinational logic with a weakly-indicating version. ALHO is a more radical departure from SDDS-NCL in the sense that it eliminates the use of hysteretic gates in its implementation of combination logic. These templates do require other timing assumptions besides the aforementioned isochronic fork assumption.

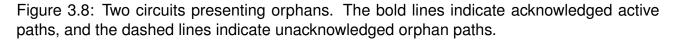

To correctly describe the new templates, this Thesis proposes a classification system for asynchronous circuits that distinguish templates based on their timing assumption and structure. This system proposes adopting the term ST as circuits that use DI encoding and completion detection to work correctly and QDI as a strict subset of ST circuits whose timing assumption is limited to wire forks. Within this context, this Thesis also proposes a formal framework to describe and analyse logic gates and netlists comprising them. This formal framework helps define the requirements for building functional ST circuits. When analysing previous works through this new lens, the Author has found issues in the synthesis technique for SDDS-NCL employed in Pulsar that result in circuits that violate the QDI criteria but still meet those for ST.

Furthermore, this Thesis also improved Pulsar to enable the construction of complex circuits. One of these improvements is the ability to implement circuits with choice. Originally Pulsar was limited to synthesise deterministic pipelines, i.e. circuits where all data must always pass through the same pipeline stages, always in the same order. "Choice" in this context is the ability to dynamically change data progression in a pipeline. This enables the efficient construction of dynamic pipelines, i.e. pipelines where data can be redirected through different paths on demand. The implementation of choice in Pulsar enables it to synthesise a RISC-V processor core. This RISC-V implementation serves as a challenging benchmark to evaluate the templates proposed in the Thesis.

To summarise, the contributions of this Thesis are:

- 1. The proposal of two new asynchronous design templates:

- (a) WInDS

- (b) ALHO

- 2. A classification system for asynchronous circuits.

- 3. The formalisation of the requirements to build functional ST circuits.

- 4. A critique of the SDDS-NCL template.

- 5. Enhancements on Pulsar to support choice.

- 6. The use of Pulsar to design a functional RISC-V processor in the three templates.

Contribution 1 is considered the main contribution of this Thesis.

#### 1.4 Structure of the Thesis Text

This Thesis' division into Chapters attempts to group related topics; the original contributions are not necessarily presented in the order they were introduced in this Chapter. The Thesis does not include a dedicated chapter about the related state of the art. Instead, comparisons to relevant related works appear within the context of the discussed topics.

Chapter 2 introduces some formal definitions required to understand the Thesis. Chapter 3 elaborates on the design of asynchronous circuits; this Chapter covers Contributions 2 to 4. Chapter 4 covers the HBCN timing model and some of its potential applications. Chapter 5 is the central Chapter of the Thesis; it provides a comprehensive portrayal of the current state of Pulsar and approaches the new templates. Contributions 1 and 5 are covered in this Chapter. Finally, Chapter 6 presents a set of experiments and evaluates the proposed templates; this final Chapter covers Contribution 6.

### 2. **DEFINITIONS**

This Chapter provides formal definitions that are used in this work. Section 2.1 formally defines Boolean expressions and functions, providing a formal framework to define gates and their properties in Section 2.2. In the end, Section 2.3 provides a formal definition of graphs and Petri nets employed in the dynamic analysis of asynchronous circuits.

### 2.1 Boolean Expression and Functions

This section provides a precise definition of Boolean expressions and some related applicable definitions; these are thoroughly used in this thesis. The definitions here aim at being comprehensive but not exhaustive. A Boolean expression draws variable names from an arbitrary set V.

**Definition 1** (Boolean Expression).  $E_V$  is the set of Boolean expressions over the set of variables V, defined recursively:

$$E_V = \{e+f : e \in E_V, f \in F_V\} \cup F_V$$

(2.1)

$$F_V = \{f \cdot t : f \in F_V, t \in T_V\} \cup T_V \tag{2.2}$$

$$T_V = \{ !t : t \in T_V \} \cup \{ (e) : e \in E_V \} \cup \{ 0, 1 \} \cup V$$

(2.3)

Where  $\{\cdot, +, (,), !, 0, 1\}$  is the set of reserved symbols,  $F_V$  is the constructor set for factors,  $T_V$  is the constructor set for terms, and V is an arbitrary variable set.

The use of multiple sets of constructor forces operator precedence and associativity. It is helpful to interpret each constructor set separately:

- 2.1 defines the left-associative OR (+) operator constructor; in its absence, it accepts any of the constructors defined in F<sub>V</sub>.

- 2.2 defines the left-associative AND (·) operator constructor; in its absence, it accepts any of the constructors defined in  $T_V$ .

- 2.3 defines the highest precedence operator and leaf constructors; it defines the constant true (1), false (0), and variable leaf constructors, the negation (!) and the parenthesis operator constructors. The parenthesis subverts the operator precedence.

An example of a Boolean expression over the variable set  $V = \{A, B, C, D\}$  is  $A + B \cdot (C + !D)$ .

From the definition of a Boolean expression, it is helpful defining a function to count references to a variable in an expression.

**Definition 2** (Reference Count Function). *The function*  $v \in e : V \times E_V \mapsto \mathbb{N}$  counts references of *v* in *e*. It is recursively defined as:

$$v \in (e) = v \in e \tag{2.4}$$

$$v \in e = v \in e \tag{2.5}$$

$$\mathbf{v} \in \mathbf{e} + \mathbf{e}' = \mathbf{v} \in \mathbf{e} + \mathbf{v} \in \mathbf{e}' \tag{2.6}$$

$$\mathbf{v} \in \mathbf{e} \cdot \mathbf{e}' = \mathbf{v} \in \mathbf{e} + \mathbf{v} \in \mathbf{e}' \tag{2.7}$$

$$v \in 0 = 0 \tag{2.8}$$

$$v \in 1 = 0 \tag{2.9}$$

$$v \in v' = \begin{cases} 1, \text{ if } v' \in V, v = v' \\ 0, \text{ otherwise} \end{cases}$$

(2.10)

As an example, consider the expression  $x = A \cdot B + !A \cdot B$ , it references the variable *A* two times and *B* one time; therefore  $A \in x = 2$  and  $B \in x = 1$

Definition 1 describes the structure of Boolean expressions, which alone are not sufficient. Their semantics arise when the Boolean expressions are *evaluated* with respect to the variable values.

**Definition 3** (State Function). The state function *s* for Boolean variables *V* is defined as:

$$\boldsymbol{s}: \boldsymbol{V} \mapsto \{\boldsymbol{0}, \boldsymbol{1}\} \tag{2.11}$$

**Definition 4** (Evaluation Function). *The* **evaluation function**  $eval_s(e) : s \times E_V \mapsto \{0, 1\}$  *exists if and only if:*

$$\forall v \in V : v \in e \ge 1 \implies s(v) \in \{0, 1\}$$

$$(2.12)$$

$$eval_s(v \in V) = s(v)$$

(2.13)

$$eval_s((e)) = eval_s(e)$$

(2.14)

$$eval_{s}(1) = 1$$

(2.15)

$$eval_s(0) = 0 \tag{2.16}$$

$$eval_{s}(!e) = \begin{cases} 1, \text{ if } eval_{s}(e) = 0\\ 0, \text{ if } eval_{s}(e) = 1 \end{cases}$$

(2.17)

$$eval_{s}(a \cdot b) = \begin{cases} 1, \text{ if } eval_{s}(a) = eval_{s}(b) = 1\\ 0, \text{ otherwise} \end{cases}$$

(2.18)

$$eval_{s}(a+b) = \begin{cases} 1, \text{ if } eval_{s}(a) = 1 \text{ or } eval_{s}(b) = 1\\ 0, \text{ otherwise} \end{cases}$$

(2.19)

The Boolean expression provides a formal method to express Boolean functions with named variables. This is useful when working with switching networks. Nonetheless, every Boolean expression is equivalent to a Boolean function.

**Definition 5** (Boolean Function). An *n*-input **Boolean function** f(x) is a function from a combination of binary values to a binary value:

$$f: \{0,1\}^n \to \{0,1\}$$

(2.20)

**Definition 6** (Boolean Expression and Function Equivalency). A Boolean expression  $e \in E_V$  is equivalent to a Boolean function  $f(x_1 ... x_n)$ , if:

$$\forall x_i, \exists s(v_i) = x_i, eval_s(e) = f(x_1 \dots x_n)$$

(2.21)

This fact is exploited in the next section to formally define some properties for both Boolean expressions and functions.

#### 2.1.1 Properties of Boolean expressions and functions

This section defines a comprehensible, but not exhaustive, set of properties of Boolean expressions and functions. These properties are used extensively in this thesis.

First, it is helpful to define *distributive normal form* (DNF) expressions as a more restrictive set of Boolean expressions. They comprise Boolean expressions without parenthesis or constants where only variables can be negated.

**Definition 7** (Disjunctive Normal Form).  $D_V$  is the set of disjunctive normal form (DNF) expressions on variables V, defined recursively:

$$D_{V} = \{ d + c : d \in D_{V}, c \in C_{V} \} \cup C_{V}$$

(2.22)

$$C_V = \{ \boldsymbol{c} \cdot \boldsymbol{n} : \boldsymbol{c} \in C_V, \boldsymbol{n} \in N_V \} \cup N_V$$

(2.23)

$$N_V = \{ | v : v \in V \} \cup V \tag{2.24}$$

Where  $C_V$  is the set of clauses and  $N_V$  is the set of strict terms without constants or parenthesis. A Boolean expression  $e \in E_V$  is said to be **in DNF** if and only if  $e \in D_V$ ; e is said to be a **clause** if  $e \in C_V$ .

As an example, the Boolean expression  $A + B \cdot (C + !D)$  is not in DNF, but the equivalent expression  $A + B \cdot C + B \cdot !D$  is in DNF.

An expression in DNF can be decomposed into a set of clauses using the clause decomposition operator.

**Definition 8** (Clause Decomposition). Let  $e \in D_V$  be a Boolean expression in DNF, for which the decomposition operator  $\tilde{a}(e)$  is recursively defined:

$$\eth(c) = \{c\}, \text{ if } c \in C_V \tag{2.25}$$

$$\eth(\mathbf{CS} + \mathbf{C}) = \{\mathbf{C}\} \cup \eth(\mathbf{CS}) \tag{2.26}$$

As an example of decomposition, regard  $\eth(A + B \cdot C + B \cdot !D) = \{A, B \cdot C, B \cdot !D\}$ .

An important concept when constructing glitch-less asynchronous circuits is unateness, formally defined as:

**Definition 9** (Boolean Function Unateness). A Boolean function  $f(x_1, x_2, ..., x_n)$  is said to be positive unate in  $x_i$  ( $1 \le i \le n$ ), if:

$$\forall x_{j}, i \neq j, f(x_{1}, \dots, x_{i-1}, 1, x_{i+1}, \dots, x_{n}) \geq f(x_{1}, \dots, x_{i-1}, 0, x_{i+1}, \dots, x_{n})$$

(2.27)

Similarly, f is called **negative unate** in  $x_i$  if:

$$\forall x_{j}, i \neq j, f(x_{1}, \dots, x_{i-1}, 0, \dots, x_{n}) \geq f(x_{1}, \dots, x_{i-1}, 1, x_{i+1}, \dots, x_{n})$$

(2.28)

If a function is neither positive unate nor negative unate in  $x_i$ , it is said to be **binate** in  $x_i$ . Moreover, if a function is positive or negative unate in all its variables, it is called a **unate** function. An unate function that is positive (negative) unate in all its variables is called a **positive** (negative) unate function.

Unateness is similarly defined for Boolean expressions:

**Definition 10** (Boolean Expression Unateness). A Boolean expression  $e \in E_V$  is **positive** unate in  $x \in V$ , if:

$$\forall (s, s') : s(x) = 1, s'(x) = 0 \implies eval_s(e) \ge eval_{s'}(e) \tag{2.29}$$

Similarly, e is negative unate in x, if:

$$\forall (s, s') : s(x) = 0, s'(x) = 1 \implies eval_s(e) \ge eval_{s'}(e) \tag{2.30}$$

If an expression is neither positive unate nor negative unate in x, it is said to be **binate** in x. Furthermore, if an expression is positive or negative unate in all its variables, it is called an **unate expression**. An unate expression that is positive (negative) unate in all its variables is called a **positive (negative) unate expression**. If an expression is binate in all its variables, it is called a **binate expression**.

An example of a positive unate expression is  $A \cdot B$ , of a negative unate expression is !A+!B, and of a binate expression is  $A \cdot !B+!A \cdot B$  (aka,  $A \operatorname{xor} B$ ).

Also, it is good to formalise the concept of complements for both Boolean functions and expressions.

**Definition 11** (Boolean Function Complement). Let *f* and *g* be Boolean functions. *f* **com**-**plements** *g if*:

$$\forall x : f(x) \neq g(x) \tag{2.31}$$

**Definition 12** (Boolean Expression Complement). *Let e and e' be Boolean expressions. e* **complements** *e' if:*

$$\forall s : eval_s(e) \neq eval_s(e') \tag{2.32}$$

Finally, relevant to the definition of logical gates in this thesis is the definitions of orthogonality:

**Definition 13** (Orthogonal Boolean Function). *Two Boolean functions f and g are* **orthogonal** *if:*

$$\forall x : f(x) = g(x) \implies f(x) = g(x) \neq 1$$

(2.33)

By extension, a set of Boolean functions F is orthogonal if:

$$\forall f, g \in F : f \neq g \implies f \text{ and } g \text{ are orthogonal}$$

(2.34)

The two orthogonal Boolean functions can never be true for the same input. Orthogonality is similarly defined for Boolean expressions:

**Definition 14** (Orthogonal Boolean Expression). *Two Boolean expressions e and e' are* **orthogonal** *if:*

$$\forall s : eval_s(e) = eval_s(e') \implies eval_s(e) = eval_s(e') \neq 1$$

(2.35)

By extension, a set of Boolean expressions  $\mathcal{C}_V$  is orthogonal if:

$$\forall e, e' \in C\!\!E_V : e \neq e' \implies e \text{ and } e' \text{ are orthogonal}$$

(2.36)

For the same state, the two orthogonal expressions should never evaluate both to true, e.g.  $A \cdot B$  and  $|A \cdot |B|$  are orthogonal, but  $A \cdot B$  and A + B are not.

#### 2.2 Gates, Netlists and Production Rules

This Section provides the formal definitions of gates and netlists used in this thesis. They are loosely based on the analytical framework introduced by Martin [Mar90] and extended by Keller et al. [KKM09]. However, they define a framework capable of analysing the correct operation of asynchronous circuits at a transistor level, whilst this thesis is concerned only with the correct operation of asynchronous circuits at a discreet logical gate level. These gates are assumed to be adequately verified and sound, with any internal fork not affecting the overall correctness of the circuit. This layered "divide-and-conquer" approach enables scaling the analysis to more extensive circuits.

Firstly, the basic definition for constructing the analytical framework in this section is the production rule:

**Definition 15** (Production Rule). *A* **production rule** (*PR*) *is a triple:*

$$(g, v, d): D_V \times V \times \{\uparrow, \downarrow\}$$

(2.37)

Where  $g \in D_V$  is a guard expression in DNF,  $v \in V$  is the target variable, and d is the direction of change. A production rule is typically denoted  $g \rightarrow vd$ .

A PR describes a sufficient condition to pull a circuit node up or down. Each variable  $v \in V$  represents a node in the circuit. A state function captures the state of the circuit at any given moment. When the guard expression g evaluates to 1, the variable v is set to be pulled up or down according to the direction d, possibly changing a future state function. The basic intuition for the PR  $g \rightarrow v \uparrow$  is that the condition g is sufficient to enable the pull-up

network driving the circuit node v. It is possible to describe a netlist comprising wires and logic gates using PRs.

Definition 16 (Netlist). A netlist is a quadruple

$$\mathcal{N} = \langle V p, V g, V w, \mathcal{P} \rangle \tag{2.38}$$

Where  $Vp \subset V$  is the set of port variables,  $Vg \subset V$  is the set of gate output variables,  $Vw \subset V$  is the set of wire termination variables, and P is a finite set of production rules.

Definition 17 (Wire). A wire is a PR pair:

$$\langle x \mapsto y \uparrow, \ !x \mapsto y \downarrow \rangle \subset \mathcal{P}$$

(2.39)

Which satisfies the predicates:

$$x \in Vg \cup Vp$$

(2.40)

$$y \in Vw \cup Vp \tag{2.41}$$

Where x is the wire origin variable, and y is the wire termination variable.

Definition 18 (Logic Gate). A logic gate is a PR pair:

$$\langle g_{\uparrow} \rightarrowtail y \uparrow, g_{\downarrow} \rightarrowtail y \downarrow \rangle \subset \mathcal{P}$$

(2.42)

Which satisfies the predicates:

$$g_{\uparrow}$$

and  $g_{\downarrow}$  are orthogonal (2.43)

$$g_{\uparrow}, g_{\downarrow} \in E_{Vw}$$

(2.44)

$$y \in Vg$$

(2.45)

Where y is the gate output,  $g_{\uparrow}$  is the gate activation expression, and  $g_{\downarrow}$  is the gate deactivation expression. Collectively, the activation and deactivation expressions are called the guard expressions.

The intuition for Definition 18 is that one PR models the pull-up network, and the other models the pull-down network of a logic gate. Similarly, Definition 17 models wires as "non-inverted" buffers. Also, notice that the logic gate definition limits the guard expressions to be orthogonal. Since it is assumed that logic gates are sound by design, short-circuiting conditions are assumed not to occur, or at least not to affect the output value. The orthogonality of the guard expressions guarantees that short-circuiting never occurs, thus simplifying the model.

The definitions presented in this Section are structured to disallow gate-to-gate connections. Predicate 2.41 dictates that wires can only drive wire termination or port variables. Similarly, Predicate 2.45 dictates that a gate can only drive gate output variables. Predicates 2.40 and 2.44 complement the aforementioned predicates; the former dictates that wires can only be driven by gates' outputs or ports, and the latter dictates that gates' inputs can only be connected to wires. However, limiting gate-to-gate connections is not sufficient to avoid implicit forking. for that, any wire can only be referenced by a single gate. This is important later when using this construction to analyse timing issues. Furthermore, no circuit node should be driven by more than one single gate or wire. Here, additional predicates are defined to enforce the netlist correctness.

**Definition 19** (Netlist Corectness). A netlist  $\mathcal{N} = \langle Vg, Vw, \mathcal{P} \rangle$  is correct, if:

$$\forall v \in Vg \exists ! \{g \rightarrowtail yd, g' \rightarrowtail y'd'\} \subset \mathcal{P} : y = y' = v, d \neq d'$$

(2.46)

$$\forall v \in Vw \exists ! \{g \rightarrowtail yd, g' \rightarrowtail y'd'\} \subset \mathcal{P} : y = y' = v, d \neq d'$$

(2.47)

$$\forall v \in Vw \exists ! \{g \rightarrowtail y \uparrow, g' \rightarrowtail y \downarrow\} \subset \mathcal{P} : (v \in g) + (v \in g') \ge 1$$

(2.48)

Predicate 2.46 and 2.47 state that each wire termination and gate output variables should be driven by a single PR pair with opposing directions, a gate or a wire respectively. Whereas, Predicate 2.48 states that every wire termination variable should only be referenced by the guards in single production rule pair, i.e. referenced by a single gate. Notice that these restrictions also limit the netlist to be fully connected.

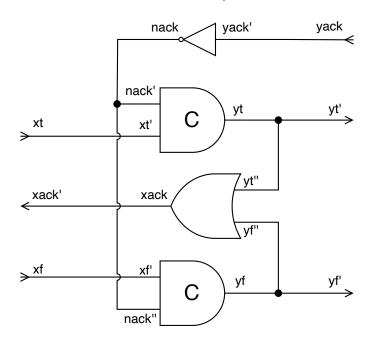

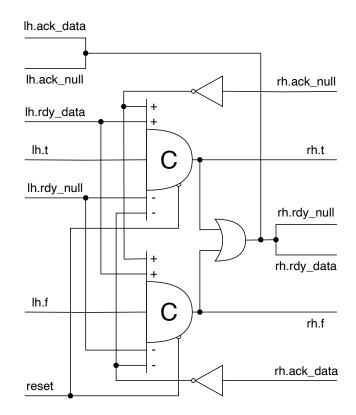

Figure 2.1: WCHB register with explicit forks. The variable names are marked on the corresponding circuit nodes.

As an example, consider the WCHB register depicted in Figure 2.1. This is a netlist with explicit wire forks. Every gate output and every wire termination is marked with a vari-

able name. The forks are explicit, as each wire termination has its own variable name. The variable sets for this netlist are:

$$Vp = \{xt, xack', xf, yack, yt', yf'\}$$

(2.49)

$$Vg = \{nack, yt, xack, yf\}$$

(2.50)

$$Vw = \{nack', xt', xf', nack'', yack', yt', yt'', yf'', yf''\}$$

(2.51)

Its wires are defined by PR pairs:

$$\langle xt \rightarrow xt' \uparrow, !xt \rightarrow xt' \downarrow \rangle$$

(2.52)

$$\langle xf \rightarrow xf' \uparrow, !xf \rightarrow xf' \downarrow \rangle$$

(2.53)

$$\langle xack \rightarrow xack' \uparrow, !xack \rightarrow xack' \downarrow \rangle$$

(2.54)

$$\langle yt \rightarrow yt' \uparrow, !yt \rightarrow yt' \downarrow \rangle$$

(2.55)

$$\langle yt \rightarrow yt'' \uparrow, !yt \rightarrow yt'' \downarrow \rangle$$

(2.56)

$$\langle yf \rightarrow yf' \uparrow, !yf \rightarrow yf' \downarrow \rangle$$

(2.57)

$$\langle yf \rightarrow yf'' \uparrow, !yf \rightarrow yf'' \downarrow \rangle$$

(2.58)

$$\langle yack \rightarrow yack' \uparrow, ! yack \rightarrow yack' \downarrow \rangle$$

(2.59)

$$\langle nack \rightarrow nack' \uparrow, !nack \rightarrow nack' \downarrow \rangle$$

(2.60)

$$\langle nack \rightarrow nack'' \uparrow, !nack \rightarrow nack'' \downarrow \rangle$$

(2.61)

And its gates are defined by the PR pairs:

$$\langle yt'' + yf'' \rightarrow xack \uparrow, !yt'' \cdot !yf'' \rightarrow xack \downarrow \rangle$$

(2.62)

$$\langle !yack \rightarrow nack \uparrow, yack \rightarrow nack \downarrow \rangle$$

(2.63)

$$\langle nack' \cdot xt' \rightarrow yt \uparrow, !nack' \cdot !xt' \rightarrow yt \downarrow \rangle$$

(2.64)

$$\langle nack'' \cdot xf' \rightarrow yf \uparrow, !nack'' \cdot !xf' \rightarrow yf \downarrow \rangle$$

(2.65)

2.2.1 Logic Gates Properties

To further analyse a logic gate, consider the OR-gate driving *xack* defined by PR Pair 2.62. When s(yt'') = s(yf'') = 0, the activation expression for *xack* evaluates to 1, setting to pull *xack* down; but for every other input state, the deactivation expression for *xack* evaluates to 1, setting to pull *xack* up. This occurs because the guard expressions for the OR-gate complement each other.

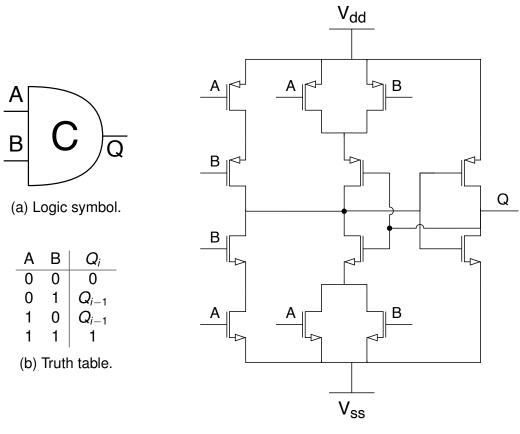

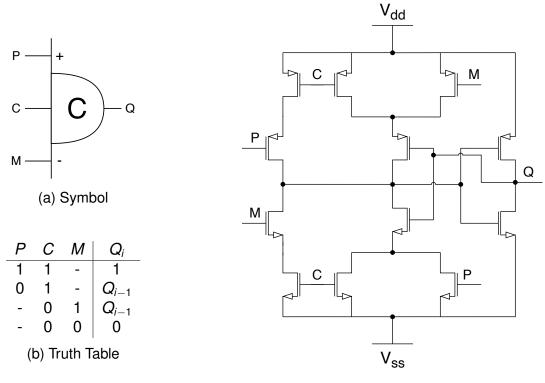

It is possible to have logic gates that, for some states, neither guard expression evaluates to 1. These are called *hysteretic gates*; they are logic gates whose guard expressions don't complement each other.

**Definition 20** (Gate Hysteresis). A gate  $\langle g_{\uparrow} \rightarrow y \uparrow$ ,  $g_{\downarrow} \rightarrow y \downarrow \rangle$  is said to be hysteretic if

$$\exists s : eval_s(g_{\uparrow}) = eval_s(g_{\downarrow}) = 0 \tag{2.66}$$

#### Otherwise, it is said to be **conventional**.

For simplicity, if no change is set to occur on the output variable of a gate, it holds its value indefinitely. This behaviour, in fact, is often implemented using an internal feedback mechanism in the logic gate. The full behaviour of any gate can be expressed by a single characteristic function that references a delayed output value:

**Definition 21.** Let  $\langle g_{\uparrow} \rightarrow q \uparrow$ ,  $g_{\downarrow} \rightarrow q \downarrow \rangle$  be a gate with output q,  $q_i$  is its current value and  $q_{i-1}$  is its previous value. The gate characteristic function is defined by the expression:

$$q_i = g_{\uparrow} + q_{i-1} \cdot !(g_{\downarrow}) \tag{2.67}$$

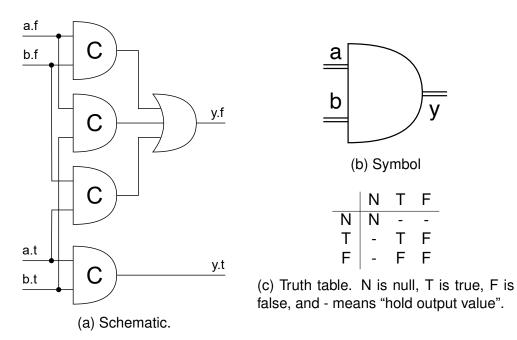

As an example, consider the C-element defined by PR Pair 2.64. When s(nack') = s(xt') = 1, the activation expressions for *yt* evaluates to 1, setting to pull *yt* up; similarly, when s(nack') = s(xt') = 0, the deactivation expression for *yt* evaluates to 1, setting to pull *yt* down. However, when  $s(nack') \neq s(xt')$ , neither guard expression evaluates to 1, then no change on *yt* is set to occur. Compare that to the OR-gate example where the two guard expressions complement each other; when one of the guards evaluates to 0, the other evaluates to 1. The OR-gate is an example of a *conventional gate*, whereas the C-Element is an example of a *hysteretic gate*

Logic gates can be further classified by their unateness, i.e. how the direction of change in an input variable affects the direction of change in the output variable.

**Definition 22** (Gate Unateness). A logic gate  $\langle g_{\uparrow} \rightarrow y \uparrow$ ,  $g_{\downarrow} \rightarrow y \downarrow \rangle$  is said to be **positive** unate *if*:

$$g_{\uparrow}$$

is positive unate and  $g_{\downarrow}$  is negative unate (2.68)

Similarly, a logic gate is said to be negative unate if:

$$g_{\uparrow}$$

is negative unate and  $g_{\downarrow}$  is positive unate (2.69)

If a logic gate is neither positive nor negative unate, it is said to be **non-unate**.

The OR-gate and C-Element are examples of positive unate gates, and as an example of a negative unate gate, consider the inverter defined by PR Pair 2.63. Compare the guard expressions in the inverter with the other gates. Notice that when s(yack) = 0, the activation expression for *nack* evaluates to 1, setting to pull *nack* up; conversely, when s(yack) = 1, the deactivation expression for *nack* evaluates to 1, setting to pull *nack* down.

This behaviour, where the output is set to rise when the inputs are at a logic low, is the opposite of what happens with the OR-gate or the C-element; this characterises the inverter as a negative unate gate and the C-element as a positive unate gate.

#### 2.3 Graphs and Petri Nets

The definitions related to timing modelling used in this work rely on or derive from the fundamental concept of *graphs*, or more specifically on *directed graphs*. Accordingly, a precise definition of this concept is provided here, based on classical definitions such as the one provided by Cormen et al. [CLRS09].

**Definition 23** (Directed Graph). A directed graph (or digraph) *G* is a pair G = (V, E), where *V* is a finite set and *E* is a binary relation on *V*. The set *V* is called the vertex set of *G*, and its elements are called vertices (singular: vertex). The set *E* is called the edge set of *G*, and its elements are called edges.

Given a vertex  $v \in V$  of a graph G = (V, E), the subset of V with the form  $\{w | w \in V \land (w, v) \in E\}$  is called the **preset** of vertex v. Accordingly, given a vertex  $v \in V$  of a graph G = (V, E), the subset of V with the form  $\{w | w \in V \land (v, w) \in E\}$  is called the **postset** of vertex v.

Unless otherwise noted, in this work all references to graphs refer to directed graphs and the word *directed* is omitted. Note that the previous definition includes describing the predecessor and successor vertex sets in graphs, a concept very important for more elaborate structures used herein. Graphs are generic structures that can be specialised to address more specific modelling needs. One such specialisation relevant here is that of *bipartite graphs*.

**Definition 24** (Bipartite Graph). A **bipartite graph** *is a directed graph* G = (V, E) *where the set V is in the union of two sets,*  $V = W \cup X$  *and where E is formed by edges having exactly one element from W and one element from X*, *i.e.*  $E \subseteq \{(a, b) | ((a \in W) \land (b \in X)) \lor ((a \in X) \land (b \in W))\}$ .

#### 2.3.1 Petri Nets

Often, the modelling of asynchronous circuits relies on Petri nets, whose static structure can be captured by graphs. The next definitions formalise the general concept of Petri nets and particularise it to more specific forms useful in asynchronous circuit modelling.

Note that a Petri net has a static structure, an initial marking and a marking evolution behaviour, the two later ones encompassing the dynamics of the net. The definition covers all parts of the concept and is based on [Mur89].

**Definition 25** (Petri Net (PN)). *A* **Petri net** *is a* 5-*tuple*  $PN = (P, T, F, W, M_0)$  *where:*  $P = \{p_1, p_2, ..., p_m\}$  *is a finite set of* **places**,  $T = \{t_1, t_2, ..., t_n\}$  *is a finite set of* **transitions**,  $F \subseteq (P \times T) \cup (T \times P)$  *is a set of* **arcs**, *collectively called the* **Petri net flow relation**,  $W : F \longrightarrow \mathbb{N}^*$  *is the* **weight** *function, and*  $M_0 : P \to \mathbb{N}$  *is the* **initial marking**, *with*  $P \cap T = \emptyset$  *and*  $P \cup T \neq \emptyset$ . *The* **Petri net structure** *is the* 4-*tuple* N = (P, T, F, W) *with no consideration of marking. A Petri net with a given initial marking can be alternatively denoted by*  $(N, M_0)$ .

The **behaviour** of a Petri net relies on a set of rules that dictate how a **marking** or **state** evolves into another state, according to the following set of **firing rules**:

- A transition t is said to be enabled if each input place p of t is marked with at least w(p, t) tokens, where w(p, t) is the weight of the arc from p to t;

- 2. An enabled transition may or may not fire, depending on whether or not the event actually takes place;

- 3. A firing of an enabled transition t removes w(p, t) tokens from each input place p of t, and adds w(t, p) tokens to each output place p of t, where w(t, p) is the weight of the arc from t to p.

A transition without any input place is called a **source transition**, and one without any output place is called a **sink transition**. Note that a source transition is unconditionally enabled and that the firing of a sink transition consumes tokens but does not produce any.

A pair of a place p and a transition t is called a **self-loop** if p is both an input and output place of t. A Petri net is said to be **pure** if it has no self-loops. A Petri net is said to be **ordinary** if all of its arc weights are 1.

It should be clear from the PN definition and from Definition 24 that the structure N of a PN can be represented by a bipartite graph where the vertex set V of the graph is the union of the set of places and of the set of transitions of the Petri net, i.e.  $V = P \cup T$ . Because of this, it is common and practical to informally state that PNs *are* bipartite graphs, ignoring the underlying marking and behaviour concepts. A big advantage of treating a PN as a graph is inheriting to PNs all graph concepts, e.g. vertex degrees, vertices (places or transitions) presets and postsets, etc. Where precision is not compromised, this document adopts this little abuse.

#### 2.3.2 Petri Net Properties

An extensive set of behavioural properties derives from the definition of a PN; Techniques to analyse PN instances for such properties abound in the literature. This Section explores PN properties specifically relevant to this work. The interested reader can refer to [Mur89] or to PN books such as [Rei13] for a more complete discussion of PN properties.

According to Murata [Mur89], there are two types of PN properties: those that depend on the initial marking  $M_0$ , called **behavioural properties**, and those independent of  $M_0$ , called **structural properties**. This works addresses only some of the behavioural properties.

The first important property is **reachability**. This is a fundamental property to study the dynamic properties of any system described by PNs. Reachability relies on the PN's *firing rules* and on the initial marking  $M_0$  of a PN. A marking  $M_n$  is said to be reachable from marking  $M_0$  if there exists a sequence of firings that transforms  $M_0$  into  $M_n$ . A firing or occurrence sequence is denoted by  $\sigma = M_0 t_1 M_1 t_1 M_2 \dots t_n M_n$ , or simply  $\sigma = t_1 t_1 t_2 \dots t_n$ . In this case,  $M_n$  is reachable from  $M_0$  by  $\sigma$  and we write  $M_0[\sigma > M_n]$ . The set of all possible markings reachable from  $M_0$  in a PN  $(N, M_0)$  is denoted by  $R(N, M_0)$ , or simply  $R(M_0)$ . The set of all possible firing sequences from  $M_0$  in a PN  $(N, M_0)$  is denoted by  $L(N, M_0)$ , or simply  $L(M_0)$ . The **reachability problem** for PNs is the problem of finding, for a given marking  $M_n$ , if  $M_n \in R(M_0)$  in a PN  $(N, M_0)$ . Sometimes it is interesting to define the **submarking reachability problem**, where instead of a PN marking  $M_n$  attentions is restricted to  $M'_n$ , a marking is limited to just some subset of places of P.

A second property worth defining here is **boundedness**, related to the maximum amount of tokens a place of some PN holds. A PN (N,  $M_0$ ) is said to be k-bounded or simply bounded if the number of tokens in each place does not exceed a finite number k for any marking reachable from  $M_0$ , i.e.  $M(p) \le k$  for every place p and every marking  $M \in R(Mo)$ . A PN (N,  $M_0$ ) is said to be **safe** if it is 1-bounded. In (asynchronous) hardware design, places of a PN are often used to represent buffers and registers for storing intermediate data. By verifying that the net is bounded or safe, it is guaranteed that there will be no overflows in buffers or registers, no matter what firing sequence is taken.

The last property needed to define in this work is **liveness**, associated with concepts in system design like the absence of deadlocks. A PN (N,  $M_0$ ) is said to be **live** (or equivalently  $M_0$  is said to be a live marking for N) if no matter what marking has been reached from  $M_0$ , it is possible to ultimately fire any transition of the PN by progressing through some firing sequence. This means that a live PN guarantees deadlock-free operation, no matter what firing sequence is chosen.

#### 2.3.3 Marked Graphs

Marked graphs constitute a limited class of PNs that allows modelling concurrency but not choice (to avoid, e.g. non-determinism). This enables capturing the behaviour of handshaking circuits. A timed marked graph can capture not only the inter-dependency and concurrency in asynchronous circuits but also the timing of certain events occurring within the circuit.

As a type of Petri net, marked graphs are bipartite graphs. Informally, a marked graph is a Petri net where each place has exactly one transition in its preset and exactly one transition in its postset. Also, a marked graph is guaranteed to be a safe Petri net, meaning that places can hold at most one token at any moment in time. These characteristics enable deriving a simple definition for a marked graph.

**Definition 26** (Marked Graph). A marked graph is a 3-tuple  $MG = (T, P, M_0)$ , where T is the set of transitions,  $P \subset \{(u, v) : u, v \in T\}$  is the set of edges connecting transitions, and  $M_0 \subset P$  is the subset of edges initially marked (the initial marking). The marking  $M_i \subseteq P$  corresponds to the subset of places holding tokens at some given instant  $i \in \mathbb{N}$ . Of course, i = 0 corresponds to the initial state of MG, where the initial marking  $M_0$  in in place.  $M_i$  represents the state of MG at instant i.

Compared to a regular PN, MGs suppress the representation of places but marks still occupy their position between transitions. In a marked graph, token movements (i.e. state changes) obey a deterministic causality relation formally defined in this work called *token flow*.

**Definition 27** (Token Flow). Let  $M_i$  be the marking of a marked graph MG at instant  $i \in \mathbb{N}$ . Let  $\bullet t = \{(u, v) \in P | v = t\}$  be the preset of transition t and let  $t \bullet = \{(u, v) \in P | u = t\}$  be the postset of transition t.

Then, it is true that  $\exists t \in T : \bullet t \subseteq M_i \implies \exists n \in \mathbb{N}_* : t \bullet \subseteq M_{i+n} \land \bullet t \nsubseteq M_{i+n}$ . This means that if all elements in the preset of a transition (•*t*) are marked, there is a moment in the future (*i* + *n*) where all elements in the postset of that transition (t•) will be marked and its preset •t will be unmarked.

Transitions control the flow of tokens in a network through the firing process. As defined for any PN (MGs obviously included), when a transition fires, it removes tokens from all places in its preset and deposits tokens to all places in its postset. Said otherwise, when a transition fires, it simultaneously marks its postset and unmarks its preset. An MG transition can only fire after all edges in its preset are marked. Further limitations can be imposed as to when a transition is allowed to fire (including time counting and other conditions).

A valuable extension of the MG concept is adding labels to account for time in either places and/or transitions, giving rise to the *timed marked graphs* or TMGs. The former is relevant to this work and is accordingly precisely defined.

**Definition 28** (Place-Delayed Marked Graph). Given a marked graph MG, it is possible to define a place-delayed marked graph as a 3-tuple  $PDMG = (T, P, M_0)$ , where T and  $M_0$  are defined as in the corresponding MG and  $P \subset \{(u, v, d) | u, v \in T, d \in \mathbb{R}+\}$ . The edges, as in an MG, connect transition u to transition v, with a label d, representing the delay assigned to each edge.

A token flowing into a PDMG edge (u, v, d) experiences a delay *d* before enabling the firing of a transition. That is, once receiving a token, an edge (u, v, d) must remain marked at least for the duration *d* before the token is removed. As in any PN, a transition can only fire in a PDMG after all its predecessor edges are holding tokens. When a transition fires it removes the tokens from its predecessor edges and deposits tokens in all of its succeeding edges.

### 3. ASYNCHRONOUS CIRCUIT DESIGN

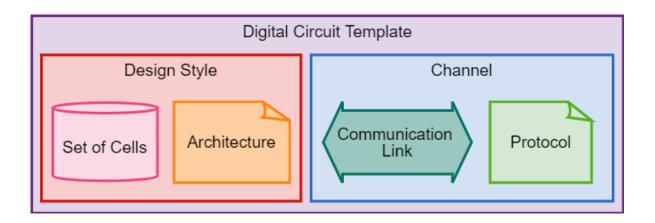

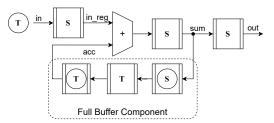

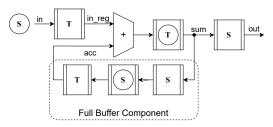

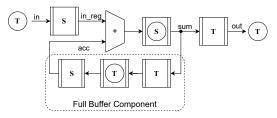

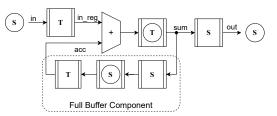

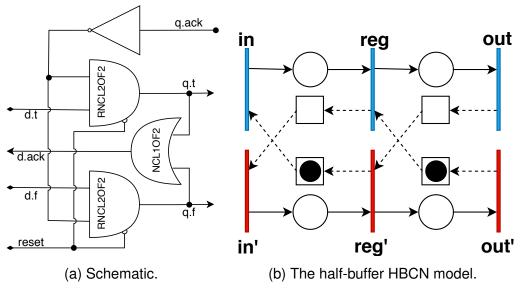

Digital design currently enables composing billions of logic gates into working circuits with a large set of functionalities to process information quickly and accurately. To handle the huge amount of gates and wires that finally implement a powerful circuit requires effective disciplines to manage the design process complexity. These disciplines involve devising efficient methods for combining very simple devices (e.g. logic gates) into basic modules, methods for abstracting these, methods for interfacing modules and methods to reuse components with a given complexity, to cite only a few of the techniques involved. It is useful to introduce the concept of a digital circuit design template to organise how a digital circuit is planned. The concept is an evolution of the *Asynchronous Circuit Template* definition, first proposed by Moreira in [Mor16]. It enables reasoning about how a digital circuit can be systematically implemented, organising the design process with a set of encompassing design abstractions that can be naturally mapped to any set of specific design techniques used for digital circuit design. The definition of the concept appears below and is illustrated by the diagram of Figure 3.1.

**Definition 29** (Digital Circuit Design Template (DCDT)). A **digital circuit design template** (DCDT) is a metamodel composed of two entities: a **design style** and a **channel**. The design style comprises two sub-entities, a **set of cells** and an **architecture**. The channel, in turn, is also a composition of two sub-entities, a **communication link** and a **protocol**. Cells in the set of cells are the basic blocks always available to build circuits, while the architecture is a set of rules for combining cells into valid circuit configurations. A communication link involves simple or structured patterns to interconnect cells in the architecture. A protocol establishes how information must flow in communication links and must be defined in accordance with the set of cells and the template architecture.

An example of a set of cells in a specific digital circuit template is the logic gates of a standard cell library in a semi-custom digital design approach. A communication link may be as simple as a wire connecting a pair of gates or a much more elaborate interconnection structure.

To enable readers to appreciate the usefulness of the DCDT metamodel, it is fitted below to the very well-known synchronous register-transfer level (RTL) digital design template. Next, this baseline modelling of a familiar template is compared to some asynchronous design templates, which enables a better grasp of the similarities and differences between synchronous and asynchronous digital design processes.

The basic way to model a known template using the DCDT metamodel consists simply of mapping the template characteristics to the metamodel four entities, which for the synchronous RTL template gives:

Figure 3.1: A diagram illustrating the digital circuit design template (DCDT) concept.

- The set of cells for synchronous RTL design can be mapped to the set of logic gates finally used to design a circuit. Even if the circuit behaviour and structure are often captured using hardware description languages (HDL) such as Verilog or VHDL, there is always an underlying library which, to support synchronous RTL design, is most often composed of combinational gates and sequential elementary components such as flip-flops. Of course, other design implementation options such as Field-Programmable Gate Arrays (FPGAs) may add to these a set of technology-dependent cells such as LUTs, carry-chains, etc.

- The architecture for synchronous RTL design implies three sets of rules: (i) rules to interconnect gates, forming functional combinational logic (CL) modules, able to transform data; (ii) rules to interconnect functional modules inputs and outputs to registers (or primary inputs/outputs); (iii) rules to connect registers to functional modules (or primary inputs/outputs).

- 3. The *communication link* for synchronous RTL relies on the assumption that: (i) wires encode information, being somehow ordered to represent digital numbers; (ii) besides, a special wire (or more generally a clock value distribution structure usually called *clock tree*) controls the flow of data everywhere in the circuit.

- 4. Finally, the *protocol* for synchronous RTL design is the widespread synchronous protocol, stating that when the clock ticks (i.e. transitions in one of two possible directions, from 0 to 1 or from 1 to 0, respectively defining either clock rising edge or falling edge sensitive synchronous templates), every register in the circuit potentially gets new data (exceptions can of course apply in specific designs).

The above modelling exercise shows that the DCDT metamodel modularity enables describing multiple templates, some very close to the popular synchronous RTL template or others very different. For example, if instead of acting on only one clock edge (as most

synchronous designs do), a circuit is defined to act on both clock edges, a new template arises (say synchronous, double edge sensitive) that requires at least a different set of cells and certainly a distinct set of architectural rules. Other templates from the literature can also be seen as possible to model with DCDT, e.g. synchronous two-phase design, latch-based (instead of flip-flop-based) design, or clock-skew tolerant design [Har01]. Exercising such metamodel mappings is left as an exercise to readers.

It is important to assess how to deal with the DCDT metamodel for describing asynchronous design templates. In fact, the variety of such templates is quite large, and none of them matches the popularity of the synchronous RTL template. The question arises regarding what can/must change in DCDT entities when these are used to model asynchronous design templates. The answer goes from *almost no change* to *basically everything*, depending on the template. The closer to synchronous an asynchronous design template is, the easier it is for synchronous designers to understand it, and the easier it is to use synchronous electronic design automation (EDA) tools in the process of designing such circuits, both of which are clear advantages. The other side of the coin reveals that the farther an asynchronous design template is from synchronous design, the better is the potential to achieve (i) power efficiency, (ii) robustness to variations, single event effects (SEEs) and technology migration, (iii) graceful circuit ageing and reduced electromagnetic interference and resistance to side-channel attacks (SCA).

It is worth exemplifying how each DCDT entity/sub-entity varies in asynchronous design templates. Summarising:

- 1. The set of cells for asynchronous design templates is often distinct from simple Boolean gates and simple flip-flops, frequently employing additional or simply different gates, such as C-elements and/or NCL gates [Fan05], multi-rail pseudo-dynamic gates [BDL11], etc.

- 2. The *architecture* for asynchronous design templates is often very different since a new set of rules applies to generate data transformations and synchronise operations. Fundamentally, the device interconnection rules are substituted to enable the implementation of local handshake operations (see the channel sub-entities description below).

- 3. The *communication link* for asynchronous design templates is usually defined based on two possible information encoding schemes, one identical to the one used in synchronous data representation and another based on encoding information with some form of delay-insensitivity property, more expensive but more robust than the former scheme.

- 4. The *protocol* for asynchronous design templates is again widely different from those in synchronous protocols, given the absence of global or semi-global control signals and depending on the encoding scheme choice.

#### 3.1 Principles of Asynchronous Design

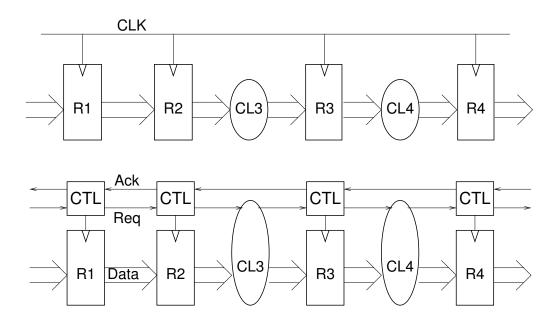

Most synchronous circuits rely on the assumption that the value on the inputs of all its registers will only be sampled at the rising (or/and falling) edge of the clock signal. Refer to Figure 3.2(a) to notice that in a classic linear pipeline, this enables to the definition of timing constraints for the maximum delay in combinational logic paths, which must be typically smaller than the clock period. Using synchronous design techniques allows ignoring gate and wire delays, as long as clock timing constraints are respected. In other words, combinational logic is allowed to switch as it computes data during, say, the interval between two consecutive rising clock edges, but the logic outputs must be stable and correct at each such edge. Having this simple model for circuit design is possible only because the clock is a global and periodic signal, *i.e.* its edges only occur at specific and known points in time and occur simultaneously (this is an assumption) at every point where required. Hence, in synchronous circuits, events will only take place at specific moments; time can thus be treated as a discrete variable.

Figure 3.2: Simplified linear pipeline circuit structure using (a) synchronous and (b) asynchronous designs. Blocks  $CL_i$  represent combinational logic, R represent registers, and *CTRL* indicates control logic. Adapted from [Spa20].

A look at the alternative, Figure 3.2(b) shows that in asynchronous circuits, there is no such thing as a single clock to signal data validity on the inputs of all registers simultaneously. Here, events can happen at any moment, and time must often be regarded as a continuous variable. Asynchronous designers rely on local handshake protocols for communication and synchronisation and on different design templates to build circuits, each with its own specific assumptions about gate and wire delays [BOF10].

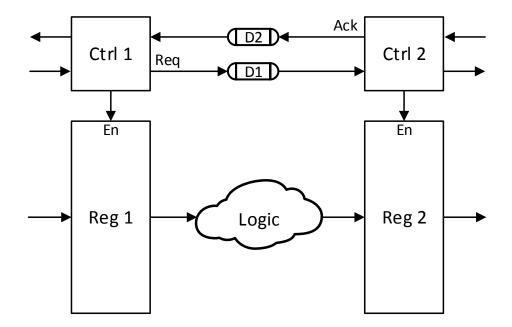

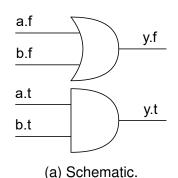

Asynchronous design templates can be broadly classified into two main families: bundled-data (BD) [Sut89] and self-timed [Mar90]. Using the DCDT metamodel, the main distinction leading to this classification relies upon the DCDT Channel entity, where communication links and protocols differ widely across BD and self-timed templates. Refer to Figure 3.3 to note that the design of a BD circuit is similar to a synchronous one; the difference is that BD relies on carefully matching the delay of data path combinational logic blocks and controlling registers to the delays in the control block that generates a local clock, rather than employ a single, global clock signal.

Figure 3.3: Example of a typical BD asynchronous pipeline fragment, with delay elements explicitly represented as *D*1 and *D*2 on request (*Req*) and acknowledge (*Ack*) paths on the control part of the circuit; blocks *Ctrli* represent the local stage controllers. Blocks *Regi* are data path registers and the *Logic* cloud represents combinational data processing between pipeline temporal barriers (the registers).

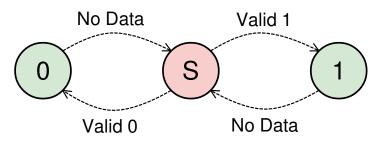

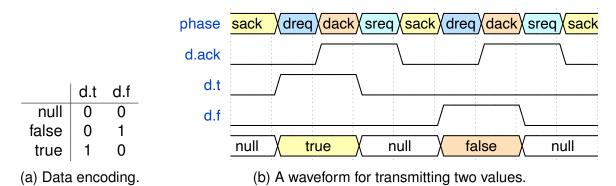

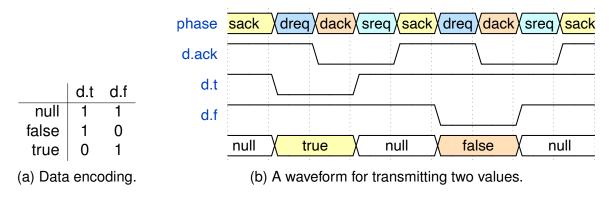

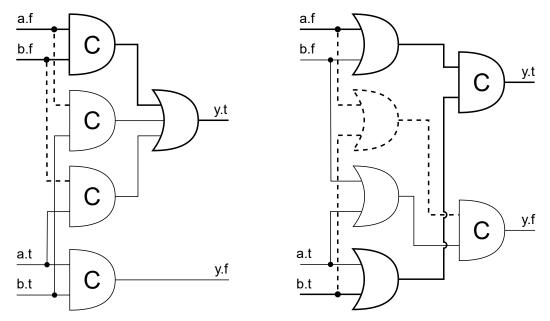

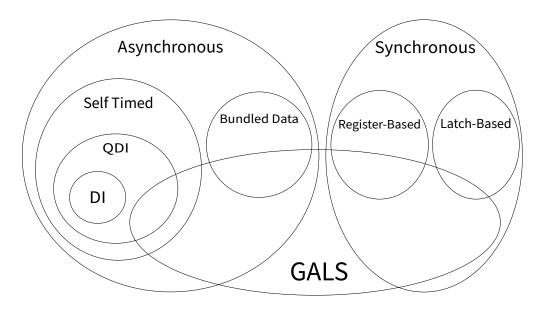

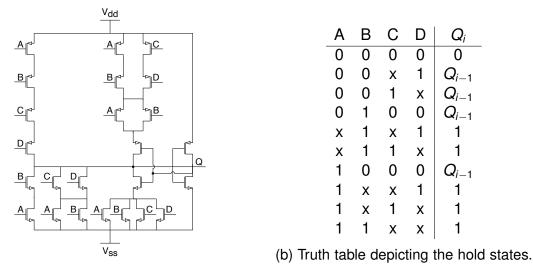

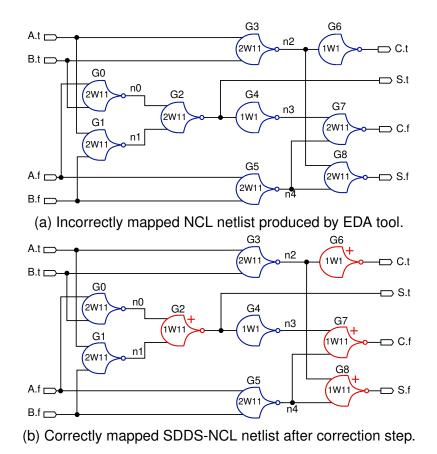

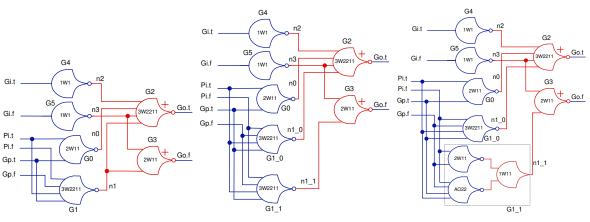

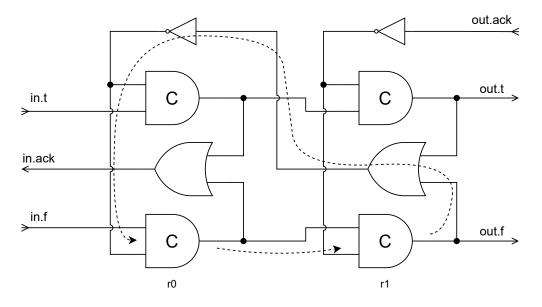

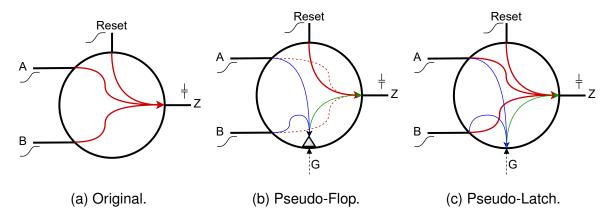

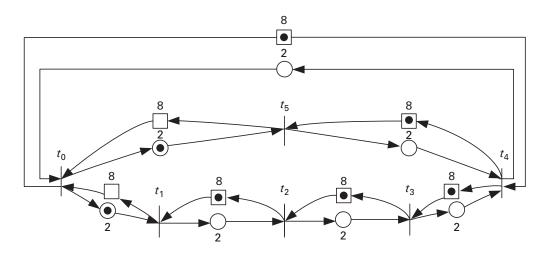

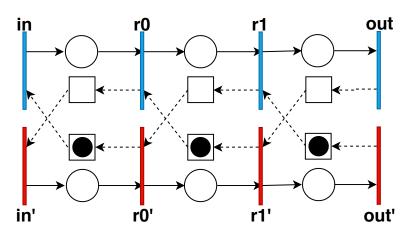

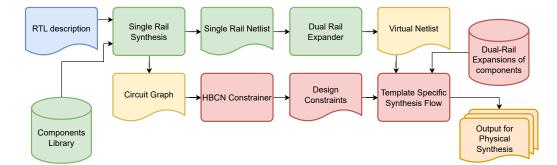

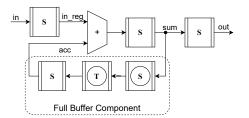

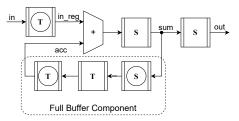

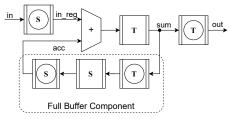

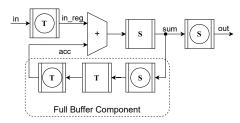

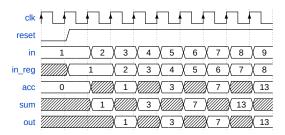

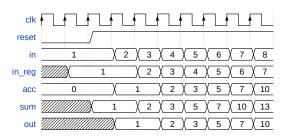

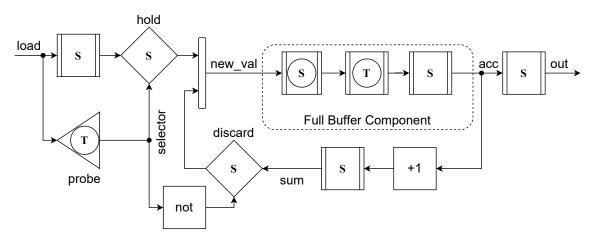

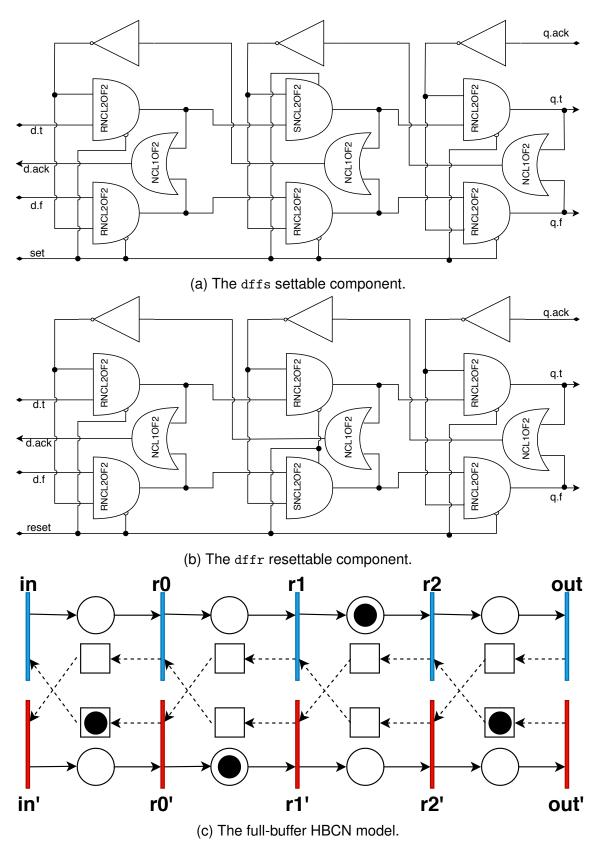

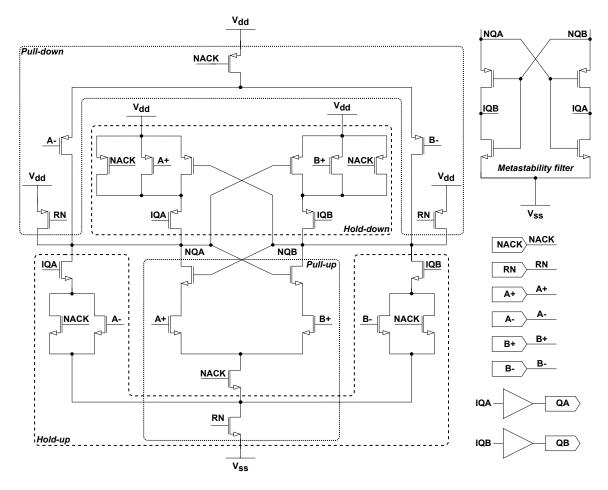

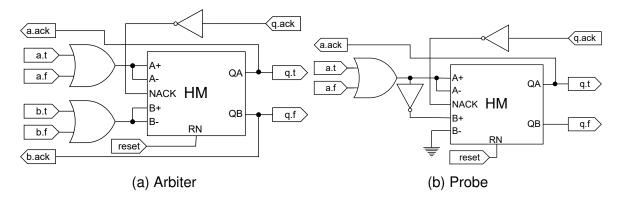

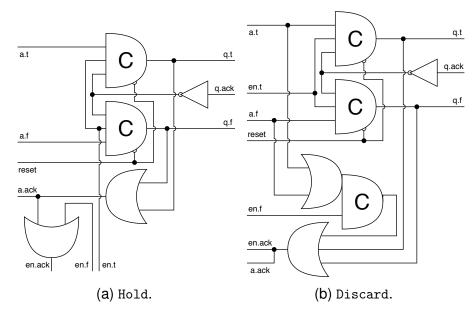

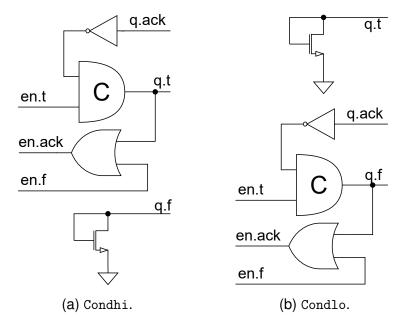

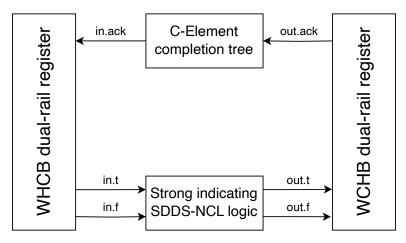

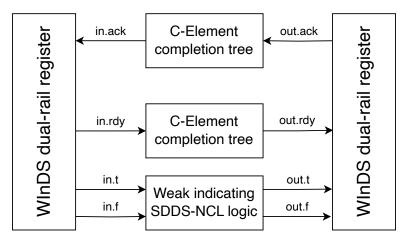

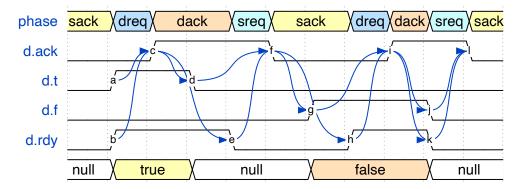

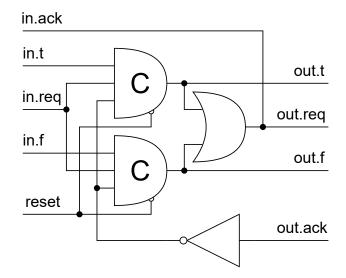

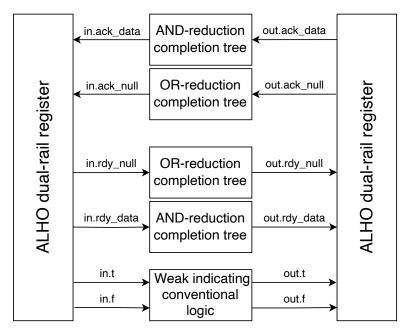

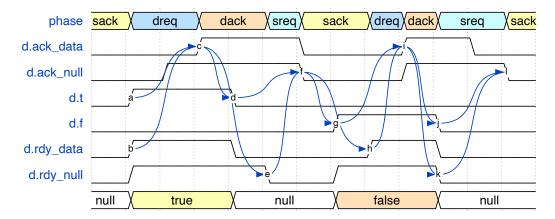

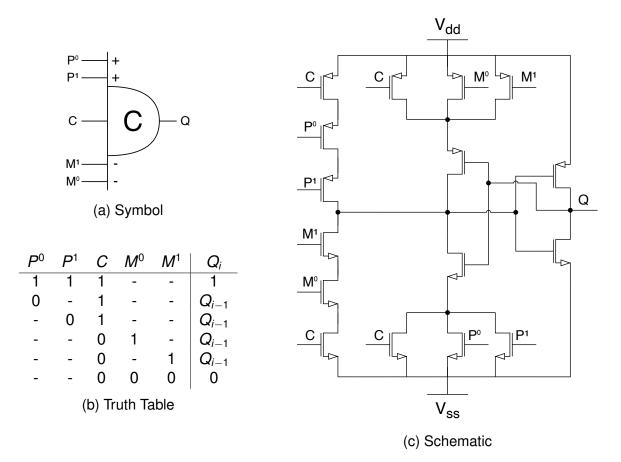

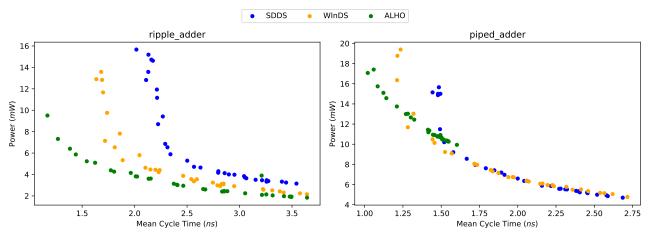

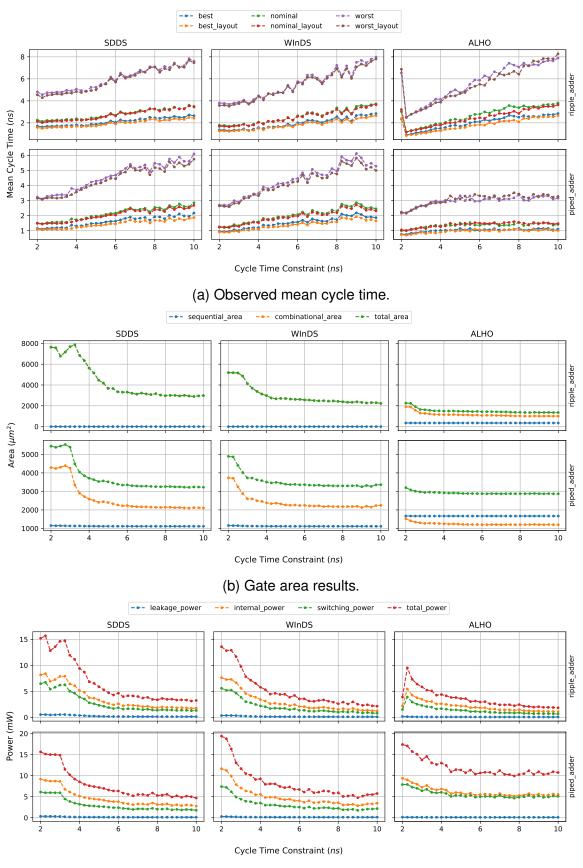

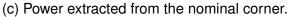

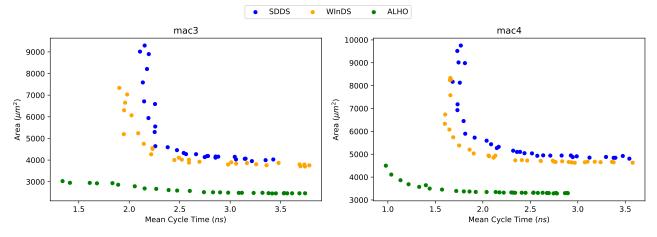

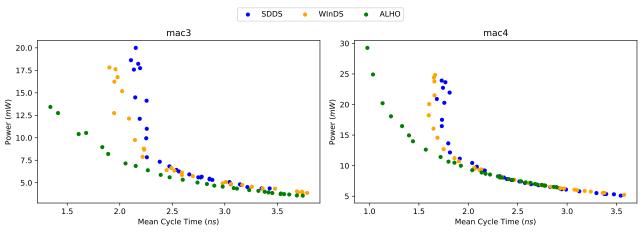

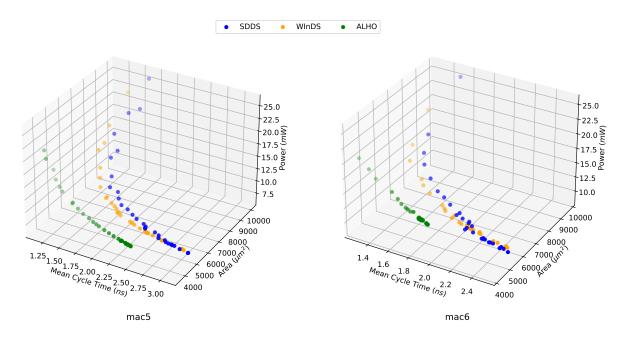

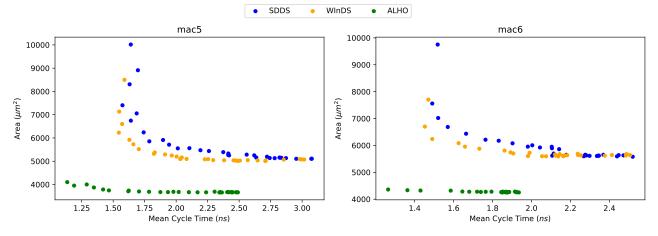

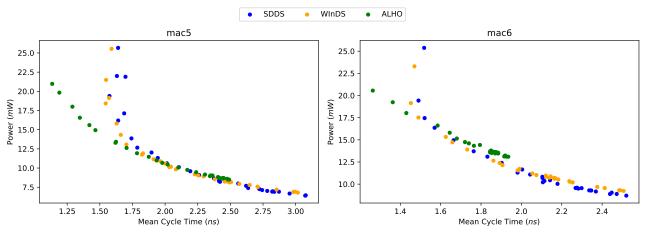

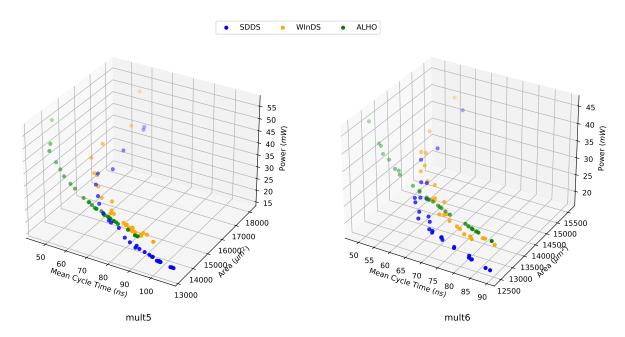

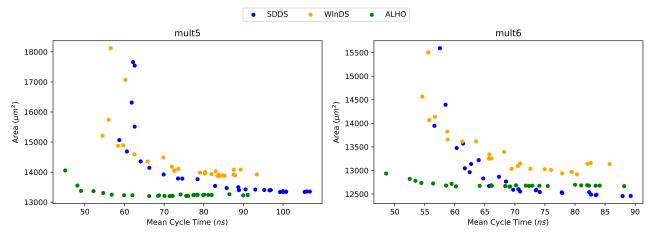

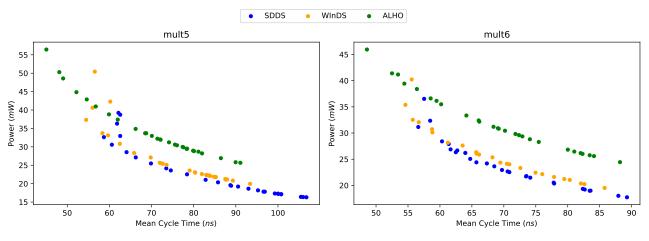

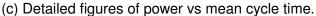

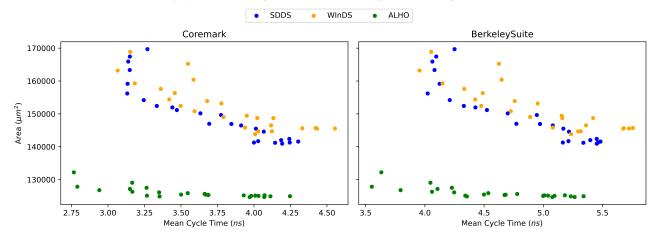

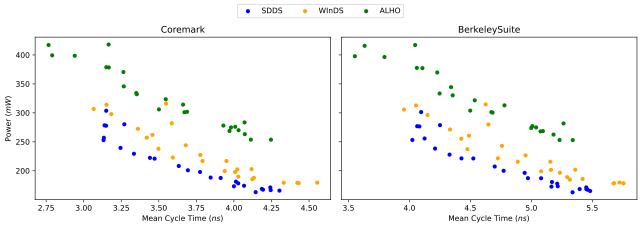

Communication and synchronisation in BD circuits are accomplished through some handshake protocol, the more common choices being 4-phase, return to zero (RTZ) protocols [BOF10]. Again using the DCDT concepts, the channel protocol characteristics provide a way to classify asynchronous design templates. Data representation in BD circuits follows the same Boolean encoding used in synchronous circuits<sup>1</sup>. This means that according to DCDT BD and synchronous design share a same channel communication link type. Also, unlike what happens in synchronous circuits, controllers are local and usually comprise just a few logic gates. An illustrative extreme example is the very efficient MOUSETRAP pipeline stage controller, which includes only an *XNOR* logic gate and a 1-bit latch [SN07]. This simplicity helps, since controllers are replicated at each and every stage of a circuit.