#### PONTIFÍCIA UNIVERSIDADE CATÓLICA DO RIO GRANDE DO SUL

#### FACULDADE DE INFORMÁTICA

### PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

# PROJETO E PROTOTIPAÇÃO DE INTERFACES E REDES INTRACHIP NÃO-SÍNCRONAS EM FPGAS

## **JULIAN JOSÉ HILGEMBERG PONTES**

Dissertação apresentada como requisito parcial à obtenção do grau de Mestre em Ciência da Computação.

Orientador: Prof. Dr. Ney Laert Vilar Calazans

Porto Alegre

Fevereiro de 2008

### Dados Internacionais de Catalogação na Publicação (CIP)

P813p

Pontes, Julian José Hilgemberg Projeto e prototipação de interfaces e redes intrachip nãosíncronas em FPGAS / Julian José Hilgemberg Pontes. – Porto Alegre, 2008. 116 f.

Diss. (Mestrado) - Fac. de Informática, PUCRS. Orientador: Prof. Dr. Ney Laert Vilar Calazans.

1. Informática. 2. Redes de Computadores. 3. Arquitetura de Redes. I. Calazans, Ney Laert Vilar. II. Título.

CDD 004.6

Ficha Catalográfica elaborada pelo Setor de Tratamento da Informação da BC-PUCRS

### TERMO DE APRESENTAÇÃO DE DISSERTAÇÃO DE MESTRADO

Dissertação intitulada "Projeto e Prototipação de Interfaces e Redes Intrachip Não-Síncronas em FPGAs", apresentada por Julian José Hilgemberg Pontes, como parte dos requisitos para obtenção do grau de Mestre em Ciência da Computação, Sistemas Embarcados e Sistemas Digitais, aprovada em 19/02/08 pela Comissão Examinadora:

| Prof. Dr. Ney Laert Vilar Calazans–<br>Orientador | PPGCC/PUCRS   |

|---------------------------------------------------|---------------|

| franch de litera                                  |               |

| Prof. Dr. Fernando Gehm Moraes–                   | PPGCC/PUCRS   |

| z (-                                              |               |

| Prof. Dr. Sérgio Bampi–                           | UFRGS         |

| Prof. D. A. E.                                    | CEITEC        |

| Prof. Dr. João Leonardo Fragoso-                  | CEITEC        |

| Homologada em (1                                  | pela Comissão |

| Prof. Dr. Fernando Gehm Moraes                    |               |

| Coordenador.                                      |               |

PUC

**Campus Central**

Av. Ipiranga, 6681 – P32 – sala 507 – CEP: 90619-900 Fone: (51) 3320-3611 – Fax (51) 3320-3621

E-mail: ppgcc@inf.pucrs.br www.pucrs.br/facin/pos

"Toda a sabedoria vem do Senhor Deus, ela sempre esteve com Ele. Ela existe antes de todos os séculos".

(Livro do Eclesiástico Capítulo 1, versículo 1).

## Agradecimentos

Gostaria de agradecer principalmente a Deus, a Nossa Senhora do Perpétuo Socorro, de quem sou devoto e grato por todas as graças recebidas desde que cheguei a Porto Alegre, e também a toda a minha família, que mesmo distante sempre me ofereceu suporte e acreditou na finalização desse trabalho. Agradeço aos meus pais: Luiz José Ferreira Pontes e Zaclis Terezinha Hilgemberg Pontes, por todo o apoio e empenho para educar-me. Aos meus irmãos: Andrea Hilgemberg Pontes, Emerson Luis Hilgemberg Pontes, Tais Hilgemberg Pontes e Marcos Javert Hilgemberg Pontes, que me apoiaram e me motivaram para que esse trabalho fosse concluído. Gostaria de agradecer a compreensão e carinho da minha namorada Patrícia Loren Inácio e de sua mãe Terezinha de Fátima Bueno. Gostaria de agradecer a todos os meus amigos de trabalho do GAPH, em especial ao Ewerson Carvalho, Edson Moreno, Rafael Soares, Leonel Tedesco e Matheus Trevisan por toda a ajuda e amizade durante esses dois anos. Gostaria de agradecer a CAPES pelo apoio financeiro. Agradeço ao meu orientador, Ney Laert Vilar Calazans pela orientação e pela motivação dada ao meu engajamento em trabalhos de pesquisa científica. Ao professor Fernando Gehm Moraes pelos conselhos, instruções e direcionamentos. Gostaria de agradecer aos amigos que me ajudaram desde a minha chegada em Porto Alegre: Anderson Mossi, Sebastião Romero, Marcio Farias e Laerte Strelow. Finalizando, gostaria de agradecer às pessoas da cidade de Ponta Grossa-PR que participaram direta ou indiretamente da minha formação, Mauro Silva e aos Professores da UEPG: Dr. Jorim das Virgens Filho e Dr. Márcio de Souza.

Muito Obrigado.

#### Resumo

Devido à evolução das tecnologias submicrônicas, hoje é possível o desenvolvimento de sistemas cada vez mais complexos dentro de um chip. Entretanto, esta evolução está inviabilizando algumas práticas de projeto tradicionais. O uso de comunicação intrachip multiponto, exemplificada por arquiteturas de barramento, e o desenvolvimento de sistemas completamente síncronos são exemplos destas práticas. Adicionalmente, a dissipação de potência está se tornando uma das principais restrições de projeto devido, por exemplo, ao aumento do uso e relevância de produtos baseados em baterias como PDAs, telefones celulares e computadores portáteis. Uma alternativa para superar estas práticas de projeto que estão perdendo viabilidade é a utilização de redes de comunicação intrachip que dêem suporte ao desenvolvimento de sistemas globalmente assíncronos e localmente síncronos (GALS). Este trabalho tem como principal alvo o desenvolvimento de suporte para o projeto utilizando o paradigma GALS em FPGAs. FPGAs foram selecionados como arquitetura alvo porque dispositivos comerciais atuais já possuem parte da infra-estrutura para dar suporte a sistemas GALS, incluindo múltiplos domínios de relógio em um único dispositivo. Também, FPGAs são dispositivos essenciais na etapa de verificação de projetos complexos que serão mais tarde sintetizados como circuitos integrados dedicados. Ao longo do trabalho, três eixos de viabilização de projeto GALS em FPGAs foram abordados, cada um gerando resultados práticos. Primeiro, foi proposta e desenvolvida uma biblioteca de macro blocos para dar suporte ao projeto de dispositivos assíncronos em FPGAs de forma compacta e eficiente. Segundo, após uma fase de comparação de interfaces assíncronas sugeridas na literatura para FPGAs e ASICs, foi proposta e validada SCAFFI, uma família de interfaces assíncronas para comunicação de módulos síncronos com relógios distintos. Terceiro, dois tipos de roteadores de redes intrachip com suporte para o projeto de sistemas GALS foram propostos e validados: Hermes GALS (Hermes-G) e Hermes GALS Low Power (Hermes-GLP). O roteador Hermes-GLP, além de dar suporte ao desenvolvimento de sistemas GALS, aproveita as características desse estilo de projeto para reduzir a dissipação de potência nos roteadores. Isto se dá através do emprego de mecanismos de chaveamento de frequência internamente ao roteador. Alguns circuitos foram usados como estudos de caso para validar as duas primeiras estruturas propostas, exemplos sendo um núcleo de criptografia RSA e multiplicadores combinacionais e pipeline. A contribuição mais importante deste trabalho foi a geração de uma infra-estrutura básica para projeto de sistemas GALS em FPGAs.

Palavras Chave: Projeto GALS, interfaces assíncronas, redes intrachip, NoCs, FPGAs.

### **Abstract**

The evolution of deep submicron technologies allows the development of increasingly complex Systems on a Chip. However, this evolution is rendering less viable some well-established design practices. Examples of these are the use of multipoint communication architectures (e. g. busses) and designing fully synchronous systems. In addition, power dissipation is becoming one of the main design concerns due e. g. to the increasing use of mobile products such as PDAs, mobile phones and laptop computers. An alternative to overcome the design practices becoming unviable is adopting Networks on Chip (NoCs) communication architectures supporting globally asynchronous locally synchronous (GALS) system design. This work has as main goal the development of features to support the design of GALS systems in FPGAs devices. The selection of FPGAs as target architecture occurred because several of these commercial devices already contain features supporting the design of GALS systems, such as the availability of multiple independent clock domains. Also, FPGAs are used in many scenarios as an important verification step in the design of complex integrated circuits. This works explores three development axes for enabling GALS design in FPGAs. Each one led to its own set of usable, practical results. First, there is the proposition and design of a macro block library of asynchronous devices for FPGAs. The cells of this library can be used to create compact and efficient non-synchronous modules in FPGAs. Second, after comparing a set of approaches for developing asynchronous interfaces in FPGAs and ASICS, the SCAFFI family of asynchronous interfaces was proposed. SCAFFI allows that modules operating in distinct clock domains interconnect to each other seamlessly. Third, two NoC routers supporting the GALS systems were proposed and validated: Hermes GALS (Hermes-G) and Hermes GALS Low Power (Hermes-GLP). The Hermes-GLP router, besides supporting the development of GALS systems, takes advantage of the GALS design style to reduce power dissipation in the routers. The way to achieve this is to add frequency switching mechanisms to the latter. Some circuits have been employed as case studies to validate the two first development axes, including an RSA cryptography core and combinational and pipeline multipliers. The most relevant strategic contribution of this work is the generation of a basic infrastructure for the design of GALS systems in FPGAs.

**Keywords:** GALS design, asynchronous interfaces, networks on chip, NoCs, FPGAs.

# Lista de Figuras

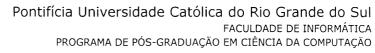

| Figura 1 – Exemplo de estrutura de um circuito síncrono. Os módulos CC são blocos de          |

|-----------------------------------------------------------------------------------------------|

| lógica combinacional e os módulos R são elementos de armazenamento27                          |

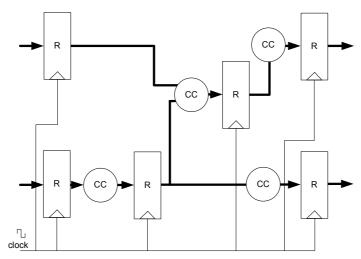

| Figura 2 – Estrutura geral de um estágio de um circuito dessincronizado. Cada módulo de       |

| processamento (lógica combinacional) é sucedido por um ou mais estágios de                    |

| sincronização, com elementos de armazenamento associados a módulos de sincronização           |

| cujo atraso de operação é ajustado durante o processo de projeto. Assim os resultados do      |

| módulo somente são armazenados e disponibilizados para outros estágios quando alcançam        |

| o final de sua computação29                                                                   |

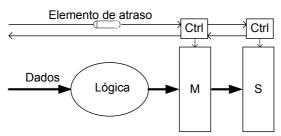

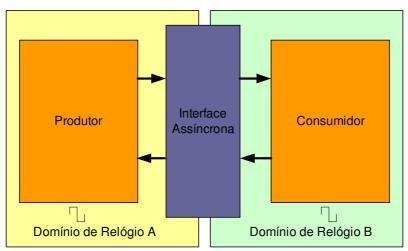

| Figura 3 – Estrutura geral de um sistema GALS29                                               |

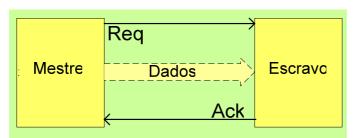

| Figura 4 – Esquema básico de um canal de comunicação utilizando protocolo handshake. C        |

| canal de dados é opcional, Caso ele exista no sentido mostrado, o canal se denomina push      |

| channel37                                                                                     |

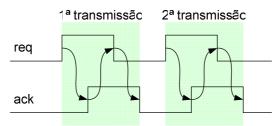

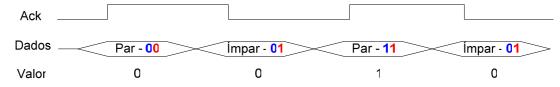

| Figura 5 – Operação do protocolo de comunicação de quatro fases                               |

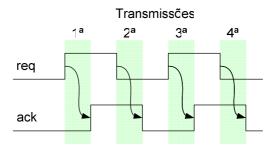

| Figura 6 – Operação do protocolo de comunicação de duas fases38                               |

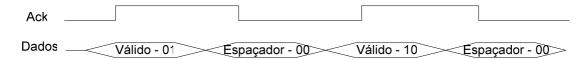

| Figura 7 – Transmissão de dados utilizando codificação de trilha dupla e protocolo            |

| handshake de quatro fases39                                                                   |

| Figura 8 – Transmissão de dados utilizando codificação de trilha dupla e protocolo            |

| handshake de duas fases                                                                       |

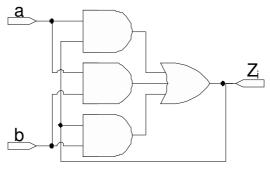

| Figura 9 – Uma forma de implementação de um C-Element de Muller de 2 entradas usando          |

| portas lógicas42                                                                              |

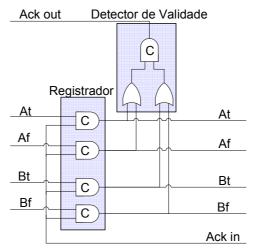

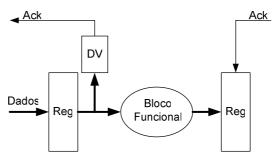

| Figura 10 – Registrador de dois bits trilha dupla do tipo half buffer associado a detector de |

| validade43                                                                                    |

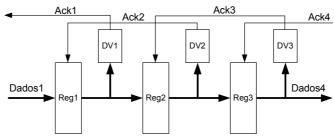

| Figura 11 – Fila assíncrona para dados codificados em trilha dupla. Os blocos DVi são         |

| detectores de validade e Regi são registradores                                               |

| Figura 12 – Posição típica de um bloco funcional em um circuito que usa codificação de        |

| trilha dupla43                                                                                |

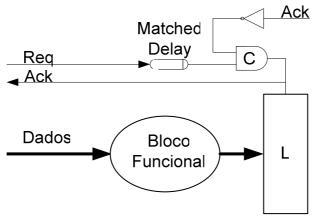

| Figura 13 – Bloco funcional para codificação bundled data associado ao circuito de            |

| armazenamento. O bloco assinalado com L designa um latch                                      |

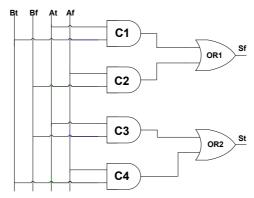

| Figura 14 – Exemplo de uma porta XOR implementada com a técnica DIMS45                        |

| Figura 15 – Representação e implementação bundled data de um circuito de controle de          |

| fluxo incondicional merge 45                                                                  |

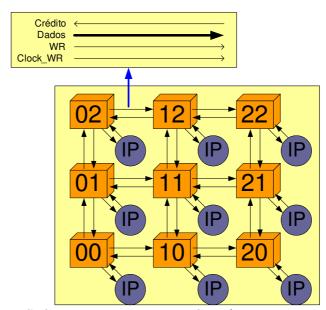

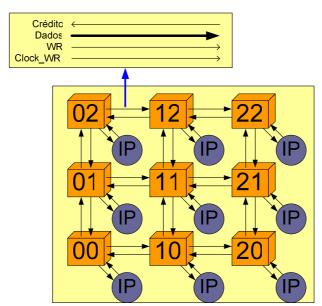

| Figura 16 – Exemplo de um SoC composto por uma NoC e núcleos IP, onde cada roteador       |

|-------------------------------------------------------------------------------------------|

| possui um núcleo IP associado. No detalhe apresenta-se a interface física de cada canal   |

| unidirecional entre dois roteadores47                                                     |

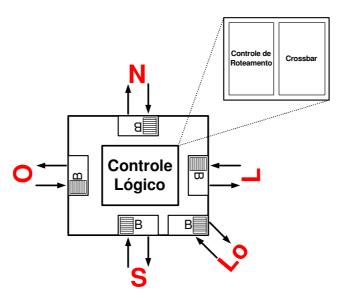

| Figura 17 – Estrutura interna de um roteador de NoC de cinco portas utilizando a infra-   |

| estrutura Hermes47                                                                        |

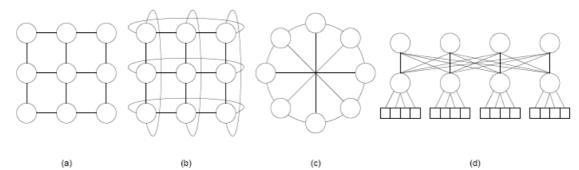

| Figura 18 - Algumas topologias de redes intrachip [SCH07] (a) malha 2D; (b) toro 2D; (c)  |

| anel cordal; (d) árvore gorda                                                             |

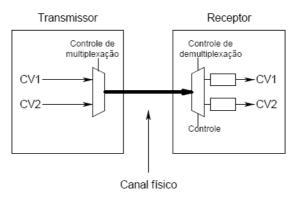

| Figura 19 – Ilustração de implementação de 2 canais virtuais compartilhando 1 canal       |

| físico. Nota-se que os canais virtuais baseiam-se em buffers de entrada compartilhando um |

| enlace físico e componentes de multiplexação e demultiplexação, além de uma lógica de     |

| controle associada [SCH07]50                                                              |

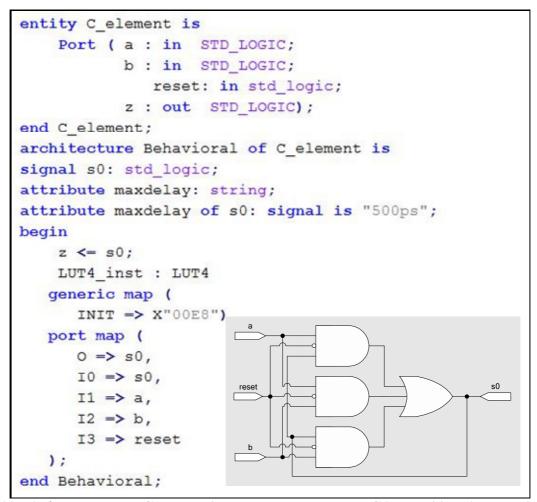

| Figura 20 – Soft macro de um C-element implementado usando FPGAs da Xilinx. A             |

| determinação do valor de configuração da LUT (INIT => X"00E8") é feita através dos        |

| valores obtidos da tabela verdade do C-element, adicionado uma lógica de reset que leva a |

| saída do C-element para 0 quando o sinal de reset = 160                                   |

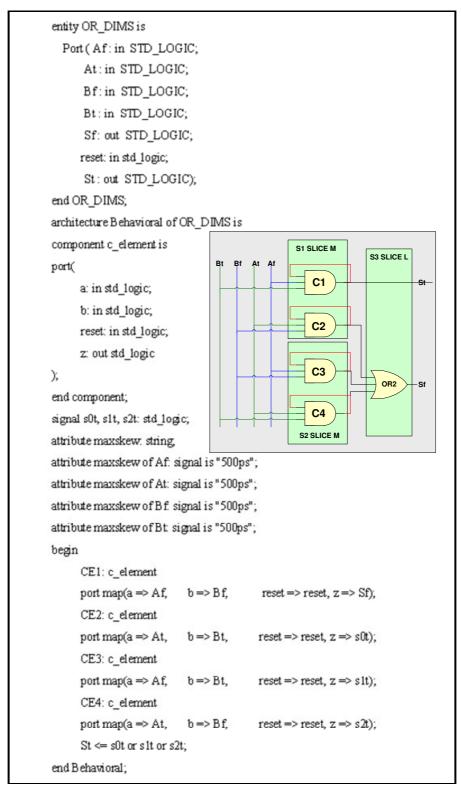

| Figura 21 – Código de uma soft macro para uma porta OR DIMS. No código VHDL são           |

| especificadas as restrições temporais das derivações isócronas. Cada C-Element consiste   |

| em uma instância do componente da Figura 20                                               |

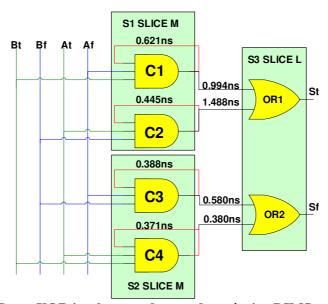

| Figura 22 – Restrições de posicionamento para transformar a porta OR DIMS da Figura 21    |

| em RPM62                                                                                  |

| Figura 23 – Porta XOR implementada usando a técnica DIMS em hard macro64                  |

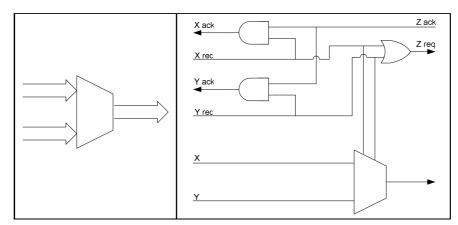

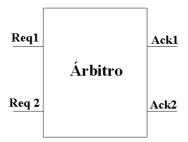

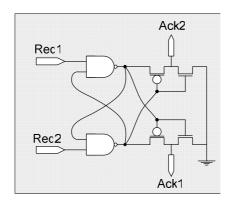

| Figura 24 – Estrutura genérica de um árbitro com descrição do seu comportamento 65        |

| Figura 25 – Estruturas internas para árbitros empregados em projeto de ASICs [MOO98].     |

| 65                                                                                        |

| Figura 26 – Circuito do árbitro proposto por Moore e Robinson                             |

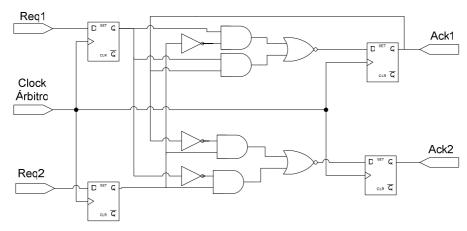

| Figura 27 – Implementação dos latches de entrada do árbitro proposto por Moore e          |

| Robinson                                                                                  |

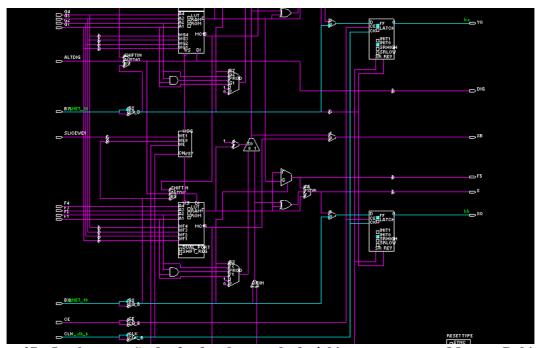

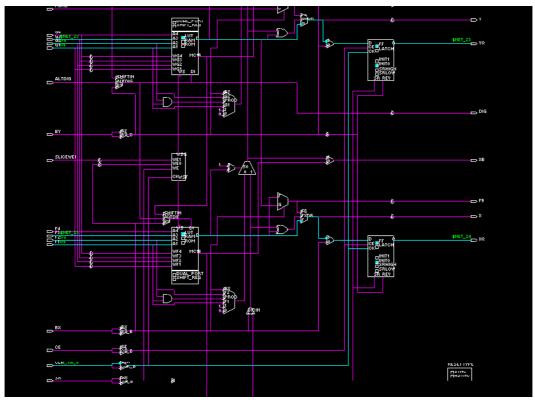

| Figura 28 – Implementação da lógica combinacional e dos latches de saída da macro do      |

| árbitro proposto por Moore67                                                              |

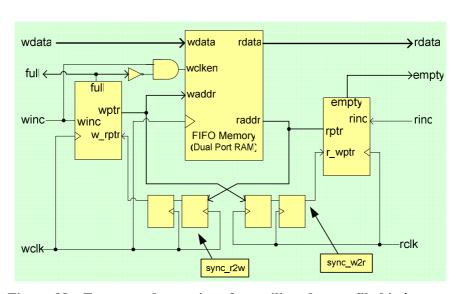

| Figura 29 – Diagrama de blocos do sistema produtor-consumidor usado para validar as       |

| interfaces assíncronas implementadas69                                                    |

| Figura 30 – Representação em SDF de um buffer70                                           |

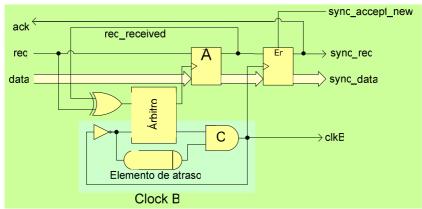

| Figura 31 – Porta de entrada da interface com relógio pausável. Usada entre um produtor   |

| assíncrono e um consumidor síncrono                                                       |

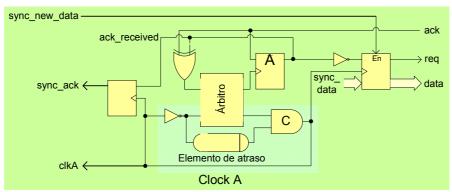

| Figura 32 – Porta de saída da interface com relógio pausável. Usada entre um produtos                                |

|----------------------------------------------------------------------------------------------------------------------|

| síncrono e um consumidor assíncrono                                                                                  |

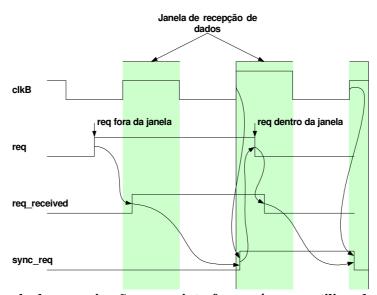

| Figura 33 - Protocolo de comunicação para a interface assíncrona utilizando relógic                                  |

| pausável71                                                                                                           |

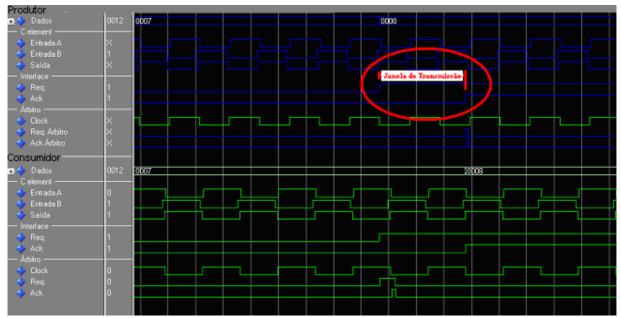

| Figura 34 - Simulação SDF da abordagem proposta por Moore dividida em dois blocos                                    |

| produtor e consumidor. Cada bloco é dividido ainda em C-element, Interface e Árbitro 73                              |

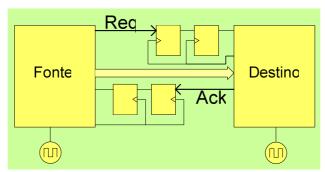

| Figura 35 – Interface entre um produtor e um consumidor utilizando sincronizadores 74                                |

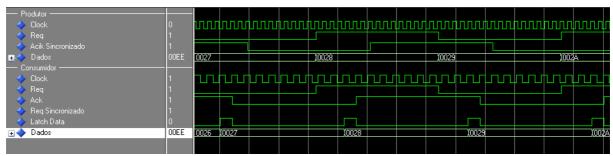

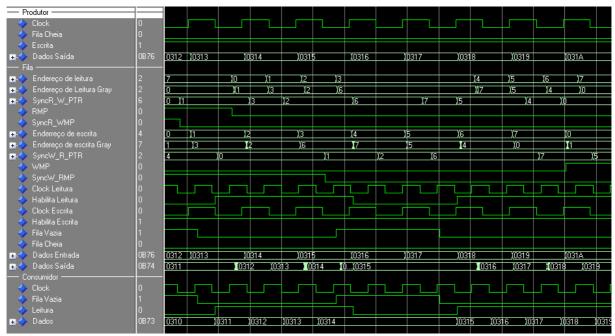

| Figura 36 – Simulação SDF para período do produtor=26ns e período do consumidor=42                                   |

| ns                                                                                                                   |

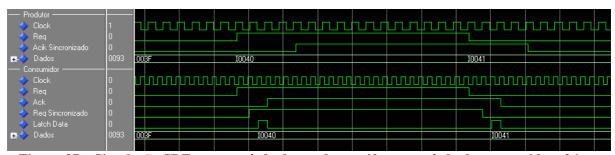

| Figura 37 – Simulação SDF para período do produtor=42 ns e período do consumidor=26                                  |

| ns                                                                                                                   |

| Figura 38 – Estrutura de uma interface utilizando uma fila bi-síncrona                                               |

| Figura~39-Simulação~SDF~de~uma~fila~bi-síncrona~para~Tcons=22ns~e~Tprod=34ns7991120000000000000000000000000000000000 |

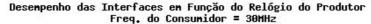

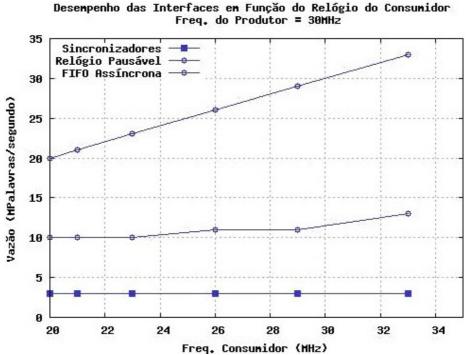

| Figura 40 – Comparação entre o desempenho faz abordagens em função do sinal de relógic                               |

| do produtor. O relógio do consumidor foi fixado com período Tcons = 30ns                                             |

| Figura 41 – Comparação de desempenho de interfaces em função do sinal de relógio de                                  |

| consumidor. O relógio do produtor foi fixado com período Tprod = 30ns81                                              |

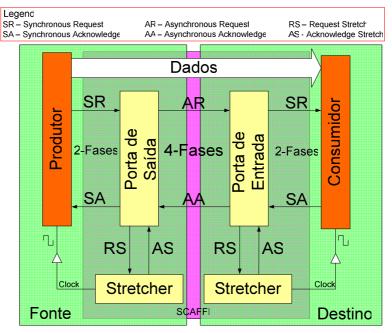

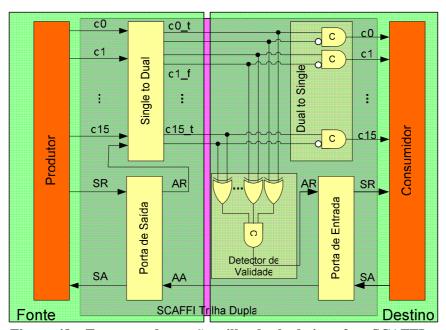

| Figura 42 – Diagrama de blocos da interface SCAFFI, mostrando a comunicação entre un                                 |

| produtor e um consumidor de dados84                                                                                  |

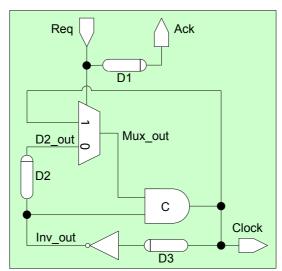

| Figura 43 – Estrutura do Stretcher. O oscilador em anel compreende os elementos: C                                   |

| element, o elemento de atraso D3 e o inversor85                                                                      |

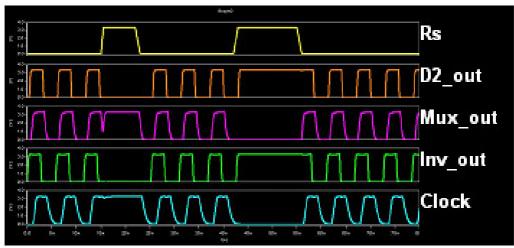

| Figura 44 – Simulação SPICE do Stretcher                                                                             |

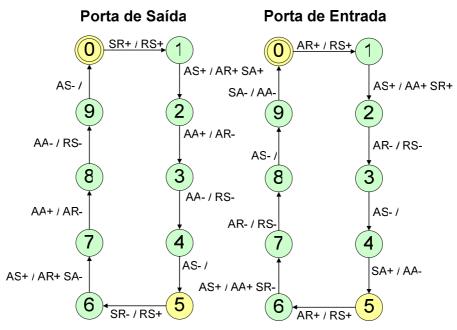

| Figura 45 – Especificação burst mode das portas de entrada e de saída da interface                                   |

| SCAFFI86                                                                                                             |

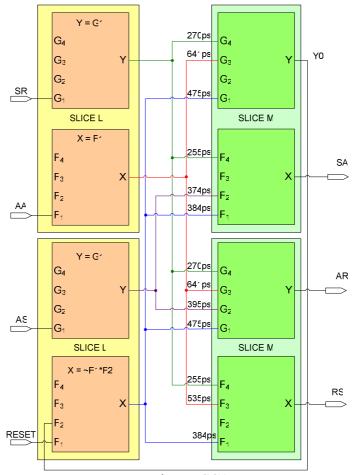

| Figura 46 – Implementação de uma porta de saída da SCAFFI usando hard macros. A.                                     |

| equações dos sinais Y0, AS, AR e RS são apresentadas na Tabela 1388                                                  |

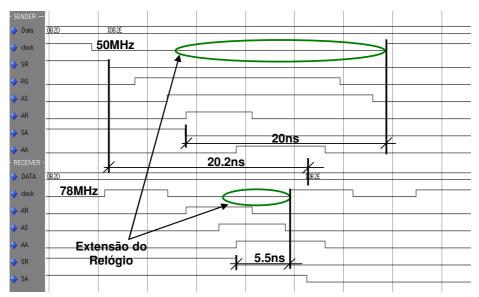

| Figura 47 – Exemplo de uma transmissão de dados utilizando a SCAFFI extraído de uma                                  |

| simulação com temporização. Os sinais AR e AA são repetidos no transmissor e no receptor                             |

| para facilitar a compreensão. O sinal RS do receptor é o mesmo sinal AR (ver Tabela 13)                              |

| As duas portas partem do estado 5                                                                                    |

| Figura 48 – Estrutura da versão trilha dupla da interface SCAFFI90                                                   |

| Figura 49 – Estrutura geral de uma rede intrachip Hermes 3x3. Cada roteador possui un                                |

| endereço XY associado93                                                                                              |

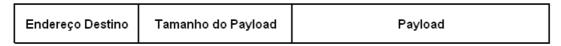

| Figura 50 – Formato do pacote da rede Hermes94                                                                       |

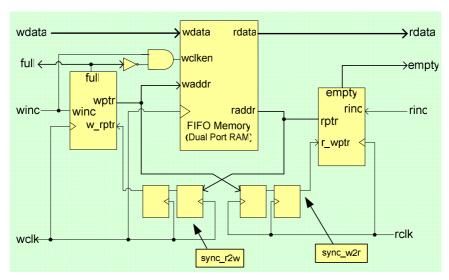

| Figura 51 – Estrutura da fila bi-síncrona adicionada à rede Hermes para sincronização dos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dados. [CUM02]9-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

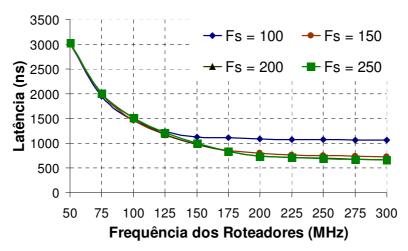

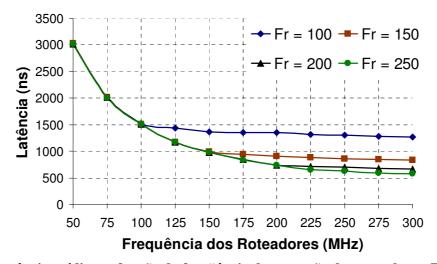

| Figura 52 - Latência média em função da freqüência de operação dos roteadores. Fr =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 200MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figura 53 - Latência média em função da freqüência de operação dos roteadores. Fs =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 200MHz97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

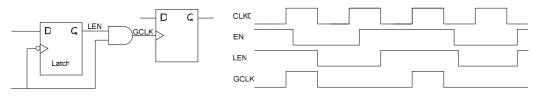

| Figura 54 – Circuito e exemplo de funcionalidade para utilizar técnicas de clock gating99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

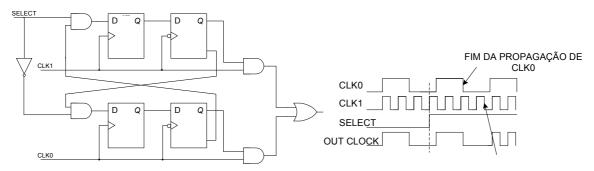

| Figura 55 - Circuito que realiza a seleção entre dois sinais de relógio e exemplo de sua                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| funcionalidade100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

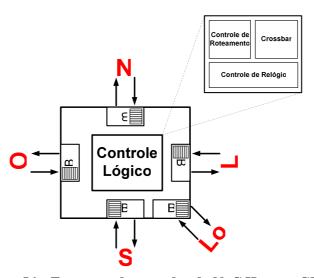

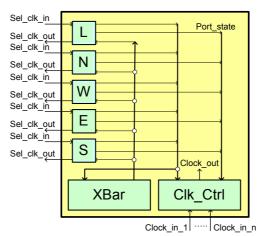

| Figura 56 – Estrutura do roteador da NoC Hermes-GLP100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figura 57 – Estrutura do controle de relógio do roteador da Hermes-GLP10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

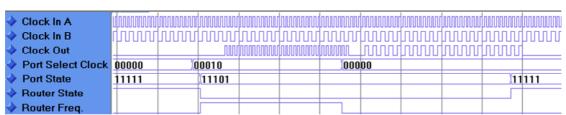

| Figura 58 – Simulação do controlador de relógio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

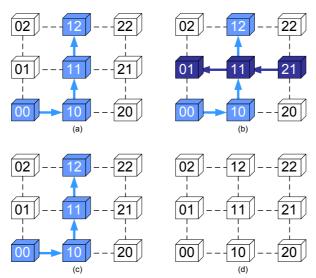

| Figura 59 – Exemplo de controle de freqüência do sinal de relógio em uma NoC Hermes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GLP 3x3. Os roteadores mais escuros possuem freqüência de operação mais elevada 10 de contra de cont |

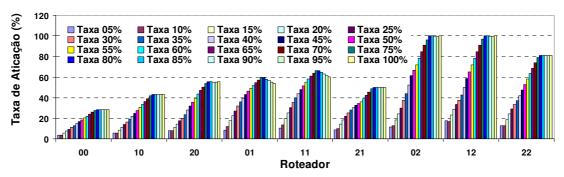

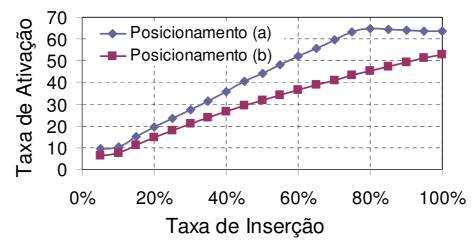

| Figura 60 – Taxa de ativação por roteador do cenário (a) (Tabela 16), em função da taxa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| de injeção de dados                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figura 61 – Comparação da taxa de ativação dos mapeamentos da Tabela 16 e da Tabela                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 17, em função das taxas de inserção10-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

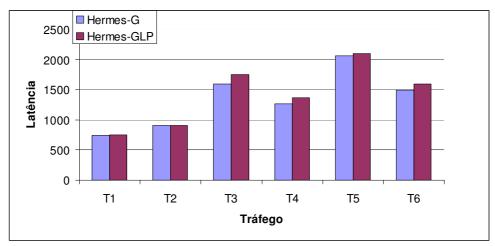

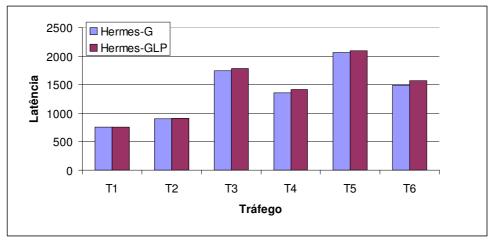

| Figura 62 – Comparação da latência média entre a NoC Hermes-G e a NoC Hermes-GLA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| para os tráfegos da Tabela 16 com taxa de inserção 30%10%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

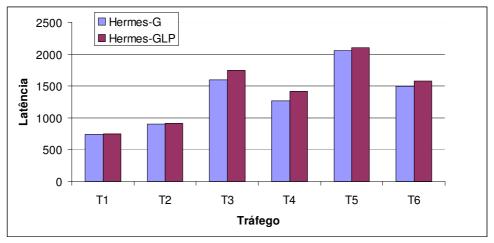

| Figura 63 – Comparação da latência média entre a NoC Hermes-G e a NoC Hermes-GLA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| para os tráfegos da Tabela 16 com taxa de inserção 50%10%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

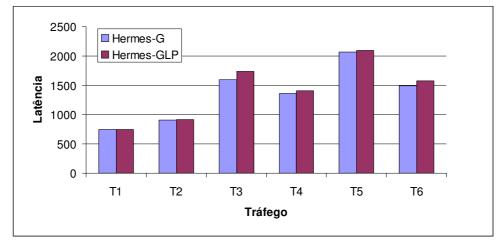

| Figura 64 – Comparação da latência média entre a NoC Hermes-G e a NoC Hermes-GLA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| para os tráfegos da Tabela 16 com taxa de inserção 70%10%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figura 65 – Comparação da latência média entre a NoC Hermes-G e a NoC Hermes-GLA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| para os tráfegos da Tabela 16 com taxa de inserção 90%108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

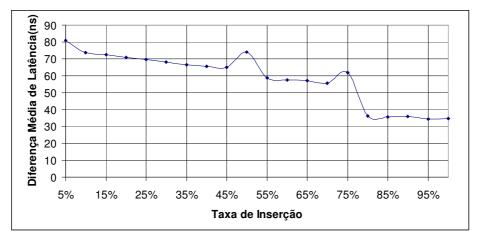

| Figura 66 – Comparação da diferença média de latência entre a Hermes-G e a Hermes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GLP em função da taxa de inserção de dados108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# Lista de Tabelas

| Tabela 1 – Relação entre estilos de projeto e recursos de projeto adicionais e o tipo de    |

|---------------------------------------------------------------------------------------------|

| circuito resultante de sua aplicação combinada                                              |

| Tabela 2 – Codificação trilha dupla de 1 bit de dados para transmissão utilizando protocolo |

| handshake de quatro fases. O valor $d.t=1$ e $d.f=1$ é inválido e nunca deve ocorrer39      |

| Tabela 3 – Codificação trilha dupla de 1 bit de dado para transmissão utilizando protocolo  |

| de handshake de duas fases. O fio em azul codifica o valor e o fio em vermelho codifica o   |

| paridade40                                                                                  |

| Tabela 4 – Codificação 1-de-N para representar 4 valores                                    |

| Tabela 5 – Tabela verdade de um C-element de Muller com 2 entradas                          |

| Tabela 6 – Classificação das NoCs e SoC baseados nestas, com base no tipo de projeto de     |

| roteador e na forma da comunicação entre roteadores e entre roteador e núcleo IP 52         |

| Tabela 7 – Comparação entre as abordagens. Quando a NoC possui um nome, este é usado        |

| na primeira coluna. Caso contrário, usa-se o nome dos autores da referência57               |